该CDC328A包含一个时钟驱动器电路,该电路分配一个 输入信号到六个输出,时钟分配的偏差最小。 通过使用极性控制输入 (T/C),各种 可以获得真实输出和互补输出的组合。

该CDC328A的特点是在 -40°C 至 85°C。

*附件:cdc328a.pdf

特性

- 低输出偏斜,适用于时钟分配和时钟生成应用

- TTL 兼容输入和输出

- 将一个时钟输入分配到六个时钟输出

- 极性控制选择真输出或互补输出

- 分布式V

CCGND 引脚可降低开关噪声 - 高驱动输出 (-48mA I

哦, 48毫安 I老) - 最先进的 EPIC-IIB^TM的^BiCMOS设计显著降低功耗

- 封装选项包括塑料小外形 (D) 和收缩小外形 (DB) 封装

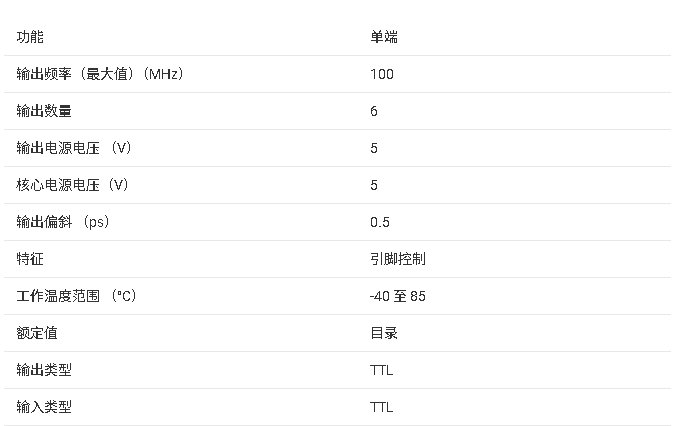

参数

1. 产品概述

CDC328A是德州仪器(TI)推出的 1输入转6输出 低偏移时钟驱动器,采用 EPIC-ΙΙB™ BiCMOS 工艺,支持极性选择功能。核心特性包括:

- 输入/输出兼容性:TTL兼容输入,CMOS兼容输出,供电范围 4.75V至5.25V(典型5V)。

- 极性控制:通过 T/C引脚 可选择输出同相(True)或反相(Complementary)信号。

- 低偏移设计:输出间最大偏移(tsk(o))仅 0.5ns,脉冲偏移(tsk(p))1ns。

- 工作温度:**-40°C至85°C**(工业级)。

2. 关键功能与逻辑

- 信号分配:单路时钟输入(A)驱动6路输出(Y1-Y4, 3Y, 4Y),支持高驱动能力(**±48mA**)。

- 控制逻辑:| T/C输入 | A输入 | 输出Y状态 |

| ----------------------- | --------------------- | ------------------------- |

| L | L/H | 同相(跟随A) |

| H | L/H | 反相(A取反) | - 封装选项:16引脚SOIC(D)或SSOP(DB)封装,符合RoHS标准。

3. 电气参数

| 参数 | 条件 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| **传播延迟(tPLH/tPHL)** | CL=50pF, VCC=5V | 1.5 | 5 | ns |

| **静态电流(ICC)** | 输出高阻态 | - | 40 | mA |

| **输入电容(Ci)** | VI=2.5V或0.5V | - | 3 | pF |

4. 绝对最大额定值

- 电压范围:输入/输出电压 **-0.5V至7V ,电源电压 -0.5V至7V**。

- 功耗限制:

- SOIC封装:0.77W(55°C静止空气)。

- SSOP封装:0.6W。

5. 应用设计注意事项

- 布局建议:

- 输入信号过渡时间需 **≤2.5ns**,避免振铃。

- 未使用的输入引脚需固定为高/低电平。

- 热管理:建议PCB设计时考虑散热,确保结温≤150°C。

总结:CDC328A是一款适用于工业环境的精密时钟分配芯片,其灵活的极性控制和低偏移特性使其成为同步系统的理想选择。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

6232浏览量

243385 -

电路

+关注

关注

173文章

6085浏览量

178825 -

输入信号

+关注

关注

0文章

559浏览量

13213 -

时钟驱动器

+关注

关注

0文章

124浏览量

14410

发布评论请先 登录

相关推荐

热点推荐

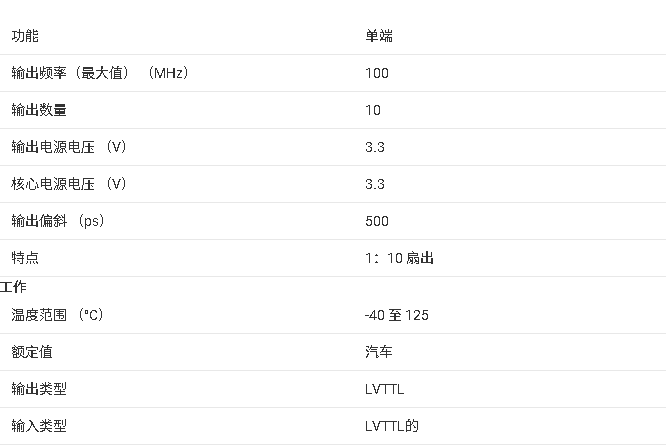

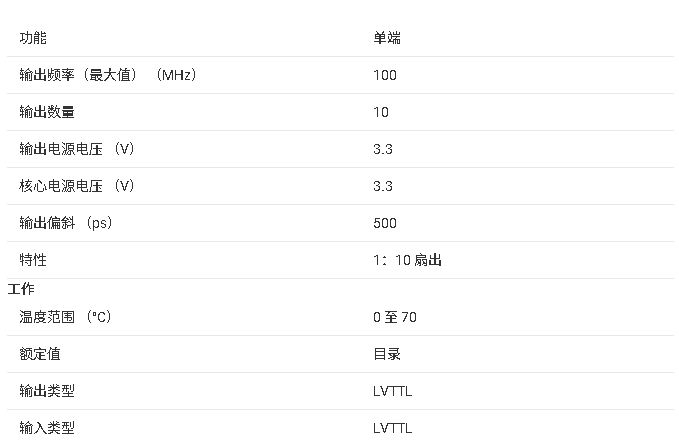

CDC2351-Q1 1:10时钟驱动器技术文档总结

该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE\) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联

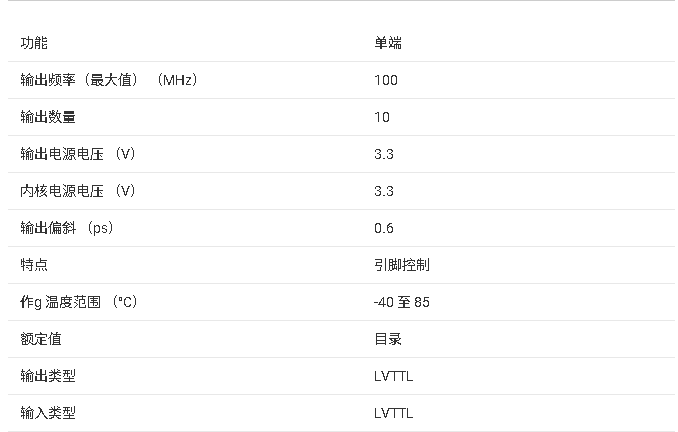

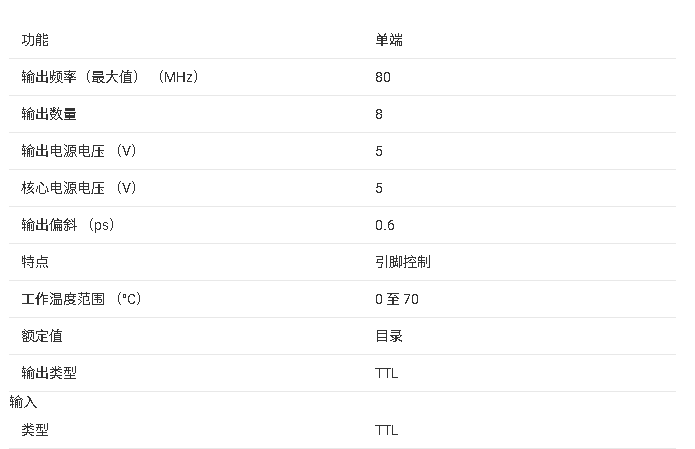

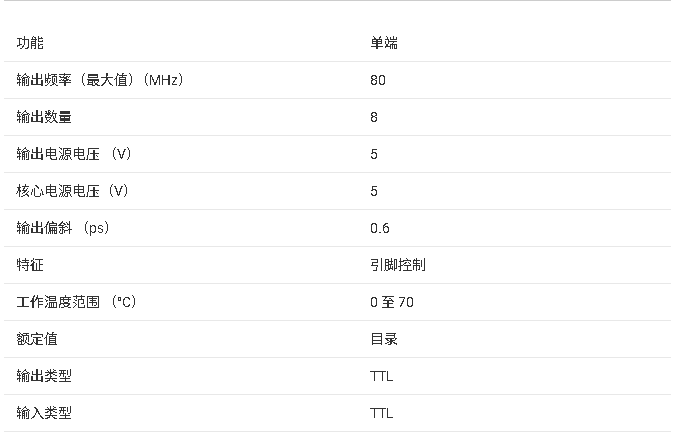

CDC351 1:10时钟驱动器技术文档总结

CDC351 是一款高性能时钟驱动器电路,可将 1 个输入 (A) 分配到 10 个输出 (Y),时钟分配偏斜最小。输出使能 (OE)\ 输入将输出禁用到高阻抗状态。

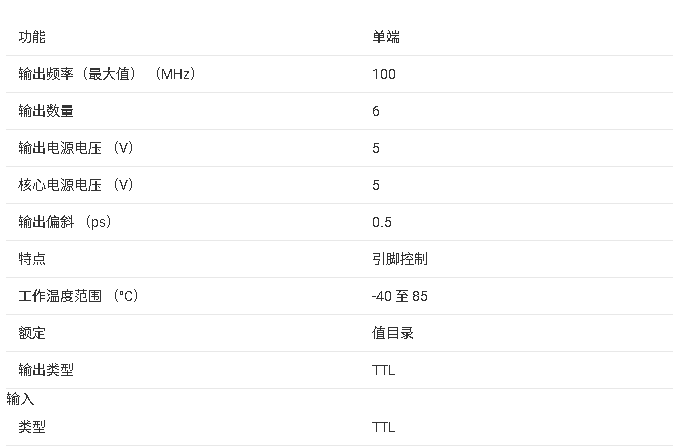

CDC329A 时钟驱动器技术文档总结

该CDC329A包含一个时钟驱动器电路,该电路将一个输入信号分配到六个输出,时钟分配的偏斜最小。通过使用极性控制输入(T\/C),可以获得真输出和互补输出的各种组合。

该CDC329A

CDC391 时钟驱动器技术文档总结

CDC391 包含一个时钟驱动器电路,该电路分配一个 输入信号到六个输出,时钟分配的偏差最小。 通过使用极性控制 (T\/C) 输入,各种 可以获得真实输出和互补输出的组合。这 output-enable 输入为 用于将输出禁

CDC2536 锁相环时钟驱动器技术文档总结

CDC2536是一款高性能、低偏斜、低抖动的时钟驱动器。它使用锁相环 (PLL) 将时钟输出信号在频率和相位上精确对齐到时钟输入 (CLKIN) 信号。它专门设计用于同步 DRAM 和

CDC2351 1线转10线时钟驱动器技术文档总结

该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE\) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC2516:高性能锁相环时钟驱动器的深度解析 在电子设计领域,时钟驱动器是确保系统稳定运行的关键组件之一。今天,我们就来详细探讨一款高性能的锁相环时钟驱动器——

CDC339 时钟驱动器:高性价比解决方案

CDC339 时钟驱动器:高性价比解决方案 在当今的电子设备中,时钟信号的精确分配和产生至关重要。CDC339 时钟驱动器以其卓越的性能和丰

CDC328A:高性能时钟驱动器的技术剖析

CDC328A:高性能时钟驱动器的技术剖析 在电子设计领域,时钟驱动器对于确保时钟信号的精确分配和稳定传输至关重要。

CDC329A:高性能1线转6线时钟驱动器的深度剖析

CDC329A:高性能1线转6线时钟驱动器的深度剖析 在电子设计领域,时钟驱动器是确保系统时钟信号稳定、准确传输的关键组件。今天,我们就来深入探讨德州仪器(Texas Instrume

德州仪器CDC2536:高性能时钟驱动器的技术剖析

德州仪器CDC2536:高性能时钟驱动器的技术剖析 在电子设计领域,时钟驱动器是确保系统时钟信号稳定、精确传输的关键组件。德州仪器(TI)的

CDC2351:高性能时钟驱动器的卓越之选

- LINE TO 10 - LINE时钟驱动器,看看它在时钟分配和生成应用中能为我们带来哪些出色的表现。 文件下载: cdc2351.pdf 产品概述 CDC2351是一款高性能的

CDC328A 时钟驱动器技术文档总结

CDC328A 时钟驱动器技术文档总结

评论