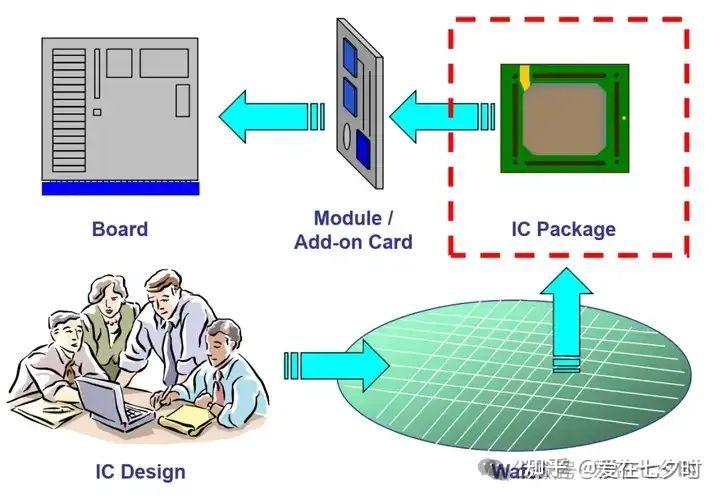

在半导体产业中,封装是连接芯片与外界电路的关键环节,而互连工艺则是封装中的核心技术之一。它负责将芯片的输入输出端口(I/O端口)与封装基板或外部电路连接起来,实现电信号的传输与交互。本文将详细介绍半导体封装中的互连工艺,包括其主要分类、技术特点、应用场景以及未来的发展趋势。

一、互连工艺概述

半导体封装中的互连工艺是连接芯片与封装基板或外部电路的关键环节。在集成电路中,各个器件或模块之间需要进行信号传输和电力供应,这就需要使用互连技术来实现。互连工艺的好坏直接影响器件的电性能、可靠性和成本。因此,它是半导体封装技术中不可或缺的一部分。

二、主要互连技术分类

1. 引线键合(Wire Bonding)

原理:

引线键合技术是通过金属线(如金线、铜线或铝线)将芯片的焊盘(Pad)与封装基板的引脚连接。这种连接方式具有设备成本低、工艺成熟的特点,非常适合低密度封装。

技术分类:

- 热压焊(Thermocompression Bonding):利用高温加压实现金属扩散键合,常用于金线。

- 超声焊(Ultrasonic Bonding):利用超声波振动清洁表面并实现键合,适合铝线。

- 热超声焊(Thermosonic Bonding):结合热压与超声技术,主要用于金线。

金属线材料:

- 金线:具有高导电性、抗腐蚀等优点,但成本较高。

- 铜线:低成本、高机械强度,但易氧化。

- 铝线:用于低端封装,成本低但导电性较差。

优点:

- 设备成本低,工艺成熟。

- 适合低密度封装。

缺点:

- 互连密度低,高频性能受限。

- 线长影响信号延迟。

2. 倒装芯片(Flip Chip)

原理:

倒装芯片技术是将芯片正面朝下,通过凸点(Bump)直接与基板焊接。这种连接方式具有高密度、短互连路径、优异的高频性能等优点。

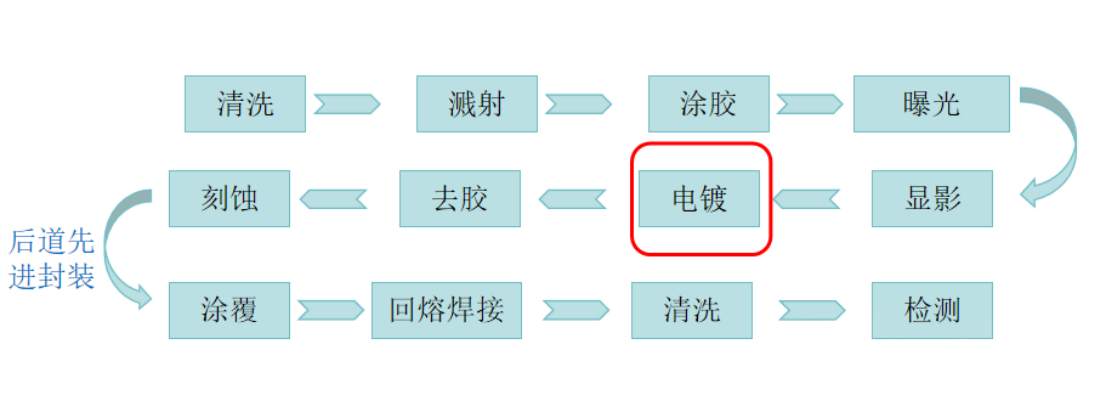

工艺流程:

- 晶圆凸块制备:在芯片焊盘上制作金属凸点,如焊料、铜柱等。

- 切割与倒装:将晶圆切割为单个芯片,翻转后对准基板焊盘。

- 回流焊接:加热使焊料熔化形成电连接。

- 底部填充(Underfill):填充环氧树脂以缓解热应力。

凸点材料:

- 焊料凸点(Sn-Ag-Cu等):成本低,但需高温回流。

- 铜柱凸点(Cu Pillar):高频性能优,用于高密度互连。

优点:

- 高密度、短互连路径。

- 优异的高频性能。

缺点:

- 工艺复杂,需精准对准。

- 成本较高。

3. 晶圆级封装(Wafer-Level Packaging, WLP)

原理:

晶圆级封装技术是在晶圆阶段完成封装和互连,切割后直接得到成品芯片。这种技术具有封装尺寸小、生产效率高等优点。

关键技术:

- 重分布层(RDL):通过光刻和电镀在芯片表面重新布线,扩展焊盘位置。

- 铜柱凸点(Cu Pillar):实现高密度垂直互连。

应用场景:

- 适用于移动设备(如CIS、射频芯片)等。

优点:

- 封装尺寸小,生产效率高。

- 适用于大规模生产。

缺点:

- 技术复杂度较高。

- 需要高精度的设备支持。

4. 扇出型晶圆级封装(Fan-Out WLP, FOWLP)

原理:

扇出型晶圆级封装技术是将芯片嵌入环氧模塑料(EMC)中,通过RDL将焊盘扇出到更大区域。这种技术可以支持更多I/O,降低封装成本。

优势:

- 支持更多I/O。

- 无需基板,降低成本。

典型应用:

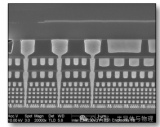

5. 硅通孔(Through-Silicon Via, TSV)

原理:

硅通孔技术是在芯片或硅中介层上制作垂直导电通道,用于3D堆叠封装。这种技术可以极大地缩短芯片间的互连长度,减小信号延迟和功耗。

工艺流程:

- 深孔刻蚀:利用干法刻蚀在硅中形成通孔。

- 绝缘层沉积(SiO₂或聚合物):隔离硅基体与导电材料。

- 阻挡层/种子层(Ti/Cu):防止金属扩散并辅助电镀。

- 电镀填充:用铜填充通孔。

导电材料:

- 金:高可靠性,但成本高。

- 铜:主流选择,导电性好,需防氧化。

- 焊料合金(Sn-Ag-Cu):用于倒装芯片,熔点可调。

应用场景:

- 高带宽存储器(HBM)、3D IC集成等。

三、互连工艺的技术特点与应用场景

1. 技术特点

- 引线键合:设备成本低,工艺成熟,但互连密度低,高频性能受限。

- 倒装芯片:高密度、短互连路径、优异的高频性能,但工艺复杂,成本较高。

- 晶圆级封装:封装尺寸小,生产效率高,适用于大规模生产,但技术复杂度较高。

- 扇出型晶圆级封装:支持更多I/O,降低成本,适用于高端芯片封装。

- 硅通孔:实现3D堆叠封装,缩短互连长度,减小信号延迟和功耗,但成本较高。

2. 应用场景

- 引线键合:适用于对成本敏感、互连密度要求不高的应用场景,如消费电子、家电等。

- 倒装芯片:适用于对高频性能、高密度互连要求高的应用场景,如处理器、GPU、高速接口芯片等。

- 晶圆级封装:适用于大规模生产、对封装尺寸要求高的应用场景,如移动设备、可穿戴设备等。

- 扇出型晶圆级封装:适用于高端芯片封装,如处理器、5G射频模块等。

- 硅通孔:适用于需要高密度集成、高速数据传输的应用场景,如高带宽存储器、3D IC集成等。

四、互连工艺的发展趋势

1. 高密度、高频性能提升

随着电子产品向小型化、高性能化方向发展,对半导体封装中的互连工艺提出了更高的要求。未来,互连工艺将向高密度、高频性能提升方向发展。例如,铜柱凸点、RDL技术等将得到更广泛的应用,以满足对高频性能、高密度互连的要求。

2. 先进封装技术的兴起

先进封装技术如3D封装、Chiplet技术等正在兴起。这些技术需要更高效的互连工艺来支持。例如,硅通孔技术是实现3D封装的关键工艺之一,未来将得到更广泛的应用。同时,混合键合(Hybrid Bonding)等新型互连技术也在不断发展,将进一步提升封装的密度和性能。

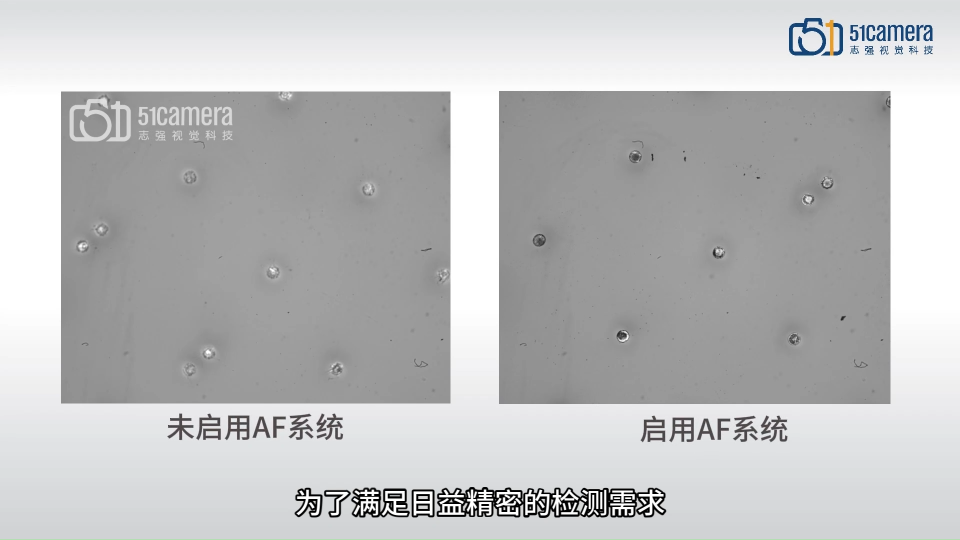

3. 自动化与智能化升级

随着人工智能、大数据等技术的发展,半导体封装行业也将迎来自动化与智能化升级。通过集成人工智能技术,可以不断优化焊接参数、实现实时工艺监控,从而提高封装质量和生产效率。例如,Wire Bonder设备正在向自动化、智能化方向发展,以满足对高精度、高效率封装的需求。

4. 环保与可持续发展

环保与可持续发展是全球关注的热点话题。半导体封装行业也将积极响应这一趋势,推动绿色封装技术的发展。例如,研究并应用新型焊接材料(如铜线替代金线)以减少贵金属的使用;开发环保型封装材料以减少对环境的影响等。

五、结论

半导体封装中的互连工艺是连接芯片与外界电路的关键环节,其好坏直接影响器件的电性能、可靠性和成本。随着电子产品向小型化、高性能化方向发展,对互连工艺提出了更高的要求。未来,互连工艺将向高密度、高频性能提升、先进封装技术兴起、自动化与智能化升级以及环保与可持续发展等方向发展。半导体封装企业需要密切关注市场动态和技术发展趋势,不断创新和优化互连工艺,以满足市场对高性能、高可靠性、低成本封装的需求。

在半导体封装领域,互连工艺的发展不仅关系到单个芯片的性能和可靠性,还对整个电子产品的性能、尺寸和成本产生重要影响。因此,半导体封装企业需要加强技术研发和创新能力,不断提升互连工艺的水平和竞争力。同时,政府和社会各界也应加大对半导体封装技术的支持和投入,共同推动半导体产业的发展和进步。

此外,随着全球半导体市场的竞争日益激烈,半导体封装企业需要不断提升自身的核心竞争力和市场响应速度。通过加强技术研发、优化生产流程、提高产品质量和服务水平等措施,可以在激烈的市场竞争中占据有利地位。同时,加强与国际先进企业的合作与交流也是提升半导体封装技术水平的重要途径之一。通过借鉴国际先进经验和技术成果,可以加快

-

芯片

+关注

关注

463文章

54443浏览量

469437 -

封装

+关注

关注

128文章

9333浏览量

149053 -

半导体封装

+关注

关注

4文章

328浏览量

15267

发布评论请先 登录

SMT工艺革新:高精度贴装与微型化组装的未来趋势

德州仪器:铜键合线在半导体封装中的应用变革

芯趋势 | 从 “锦上添花” 到 “生死刚需”:AI 重构半导体封装,破解良率成本困局

半导体“封装过程”工艺技术的详解;

半导体封装介绍

自主创新赋能半导体封装产业——江苏拓能半导体科技有限公司与 “半导体封装结构设计软件” 的突破之路

从良率突破到成本优化:PLP解决方案如何改写半导体封装规则

半导体分层工艺的简单介绍

半导体芯片中的互连层次

半导体封装工艺流程的主要步骤

半导体封装革新之路:互连工艺的升级与变革

半导体封装革新之路:互连工艺的升级与变革

评论