文章来源:半导体与物理

原文作者:jjfly686

本文介绍了芯片的分层制造工艺。

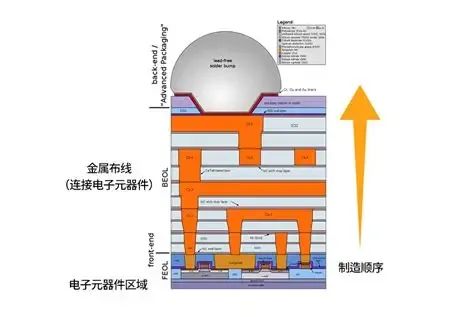

在指甲盖大小的硅片上建造包含数百亿晶体管的“纳米城市”,需要极其精密的工程规划。分层制造工艺如同建造摩天大楼:先打地基(晶体管层),再逐层搭建电路网络(金属互连),最后封顶防护(封装层)。这种将芯片分为FEOL(前道工序)与BEOL(后道工序)的智慧,正是半导体工业的基石。

一、芯片:从硅衬底到金属穹顶

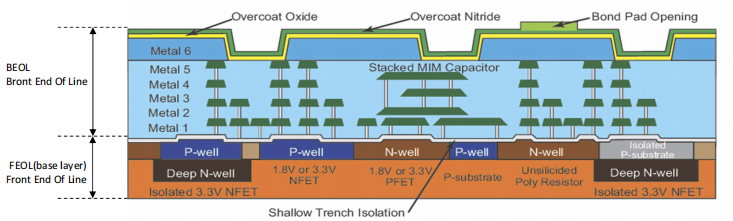

下图展示了典型集成电路的剖面结构,自上而下共分三大功能区:

▲ 顶层防护层(Overcoat)

氮化硅保护层(SiN)—— 防潮防刮

氧化硅绝缘层(SiO₂)—— 电气隔离

焊盘开口(Bond Pad Opening)—— 连接外部引脚

▲ 后道工序层(BEOL:Back End Of Line)

金属4-1层(Cu/Co)—— 局部数据互连

▲ 前道工序层(FEOL:Front End Of Line)

晶体管层(NFET/PFET)—— 开关核心

多晶硅(Poly)—— 电路导线

浅槽隔离(STI)—— 晶体管间绝缘

N阱(N-well)—— 高压器件隔离

二、FEOL:建造晶体管

前道工序(FEOL)在裸硅晶圆上直接制造晶体管,如同城市的地基建设:

核心工艺与功能

| 浅槽隔离(STI) | 刻蚀沟槽→填充SiO₂ | 隔离相邻晶体管,防止漏电 |

| 深N阱 | 高能磷注入 | 创建独立电势区 |

| 晶体管沟道 | 离子注入+退火 | 形成NMOS/PMOS导电通道 |

| 多晶硅栅 | LPCVD沉积+光刻 | 控制电子开关 |

| 硅化物阻挡层 | 氮化硅掩膜 | 保护导电区域 |

| 结构 | 制造工艺 | 核心作用 |

|---|

技术突破:

应变硅技术:在PMOS源漏区嵌入SiGe,空穴迁移率提升40%;

高k金属栅:HfO₂替代SiO₂,栅极漏电流降低1000倍。

三、BEOL:编织电路

后道工序(BEOL)在晶体管层之上构建金属互连网络,如同城市的道路与电网:

核心结构解析

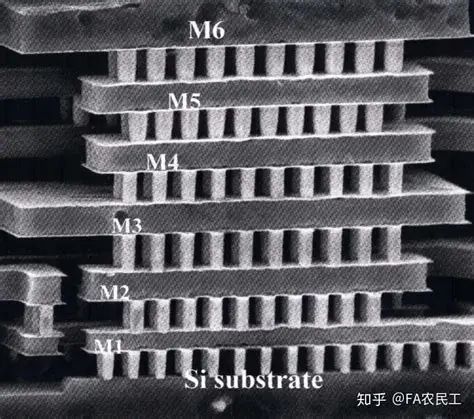

1. 金属互连层(Metal 1-6)

铜互连(Cu)替代铝,电阻降低37%;钴镶边(Co Liner)抑制电迁移,寿命提升10倍。Metal 1:晶体管直接连接(线宽10-20 nm);Metal 4:模块间互连(如CPU与缓存);Metal 6:全局电源网络(厚度1 μm,载流>1A)。

2. 堆叠电容(MIM Capacitor)结构

TaN-绝缘层(Al₂O₃)-TaN“三明治”;作用:为模拟电路(如PLL)提供稳定电荷;密度:5 fF/μm²,占面积仅为传统MOS电容的1/5。

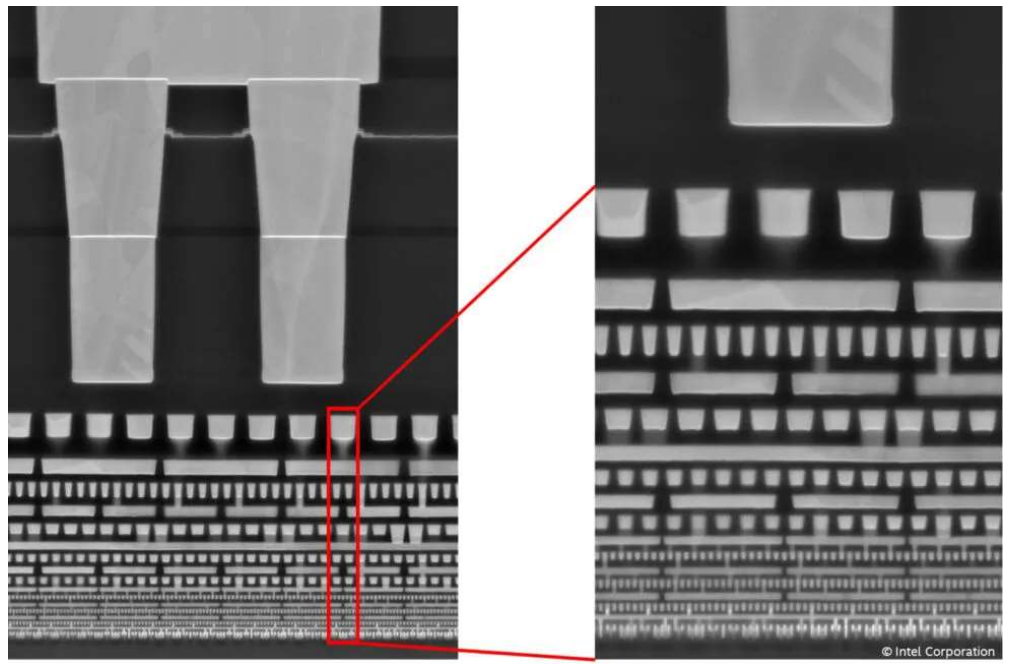

3. 通孔(Via)与沟槽(Trench)

双大马士革工艺:同步刻蚀通孔+导线槽,铜一步填充;深宽比极限:3 nm节点达5:1,ALD沉积2 nm钽阻挡层。

四、顶层防护

氧化硅覆盖层(Overcoat Oxide)阻挡湿气腐蚀;

氮化硅密封层(Overcoat Nitride)抗划伤强度抵御封装应力;

焊盘开口(Bond Pad Opening)激光开窗露出铝焊盘。

创新防护技术低k聚合物涂层:填充金属线间隙,减少信号串扰30%;原子层沉积密封:Al₂O₃薄膜隔绝钠离子污染。

-

半导体

+关注

关注

339文章

31316浏览量

266946 -

制造工艺

+关注

关注

2文章

217浏览量

21317 -

芯片制造

+关注

关注

11文章

736浏览量

30540

原文标题:芯片制造:揭秘半导体分层工艺的奥秘

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体分层工艺的简单介绍

半导体分层工艺的简单介绍

评论