本文介绍了FinFet Process Flow-源漏极是怎样形成的。

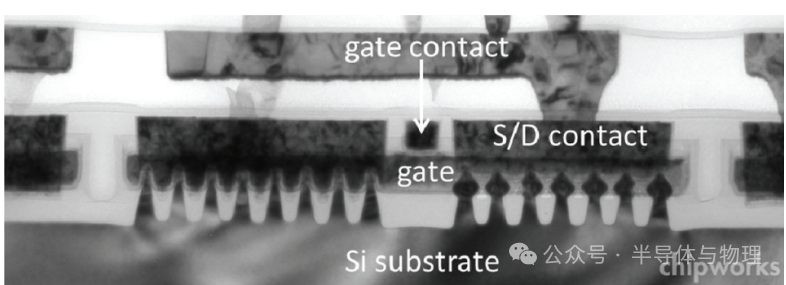

在FinFET制造工艺中,当完成伪栅极结构后,接下来的关键步骤是形成源漏极(Source/Drain)。这一阶段对于确保器件性能和可靠性至关重要。以下是详细的工艺流程描述,特别关注PMOS和NMOS源漏极形成的每一步及其作用。

FinFet Process Flow-Fin的形成,FinFet Process Flow-哑栅极的形成。

一、为栅极侧壁沉积

晶圆清洁与侧壁沉积

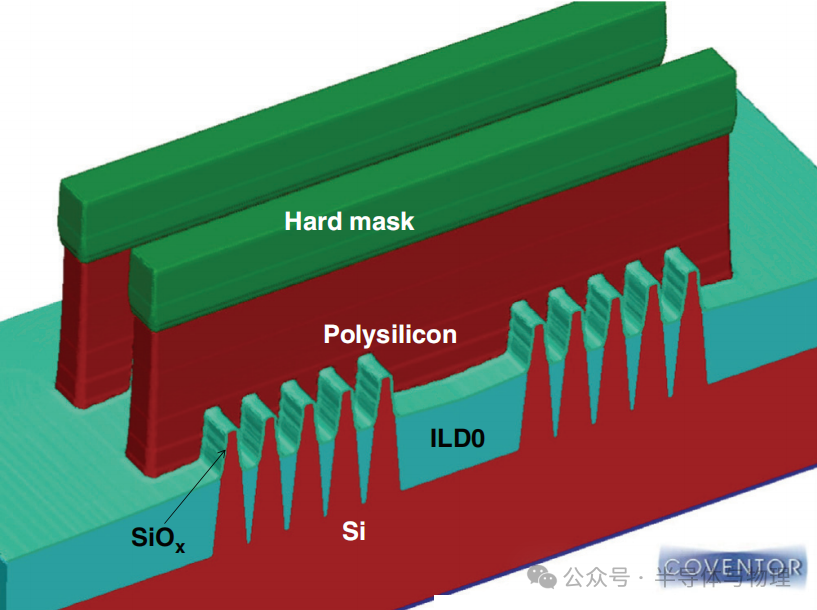

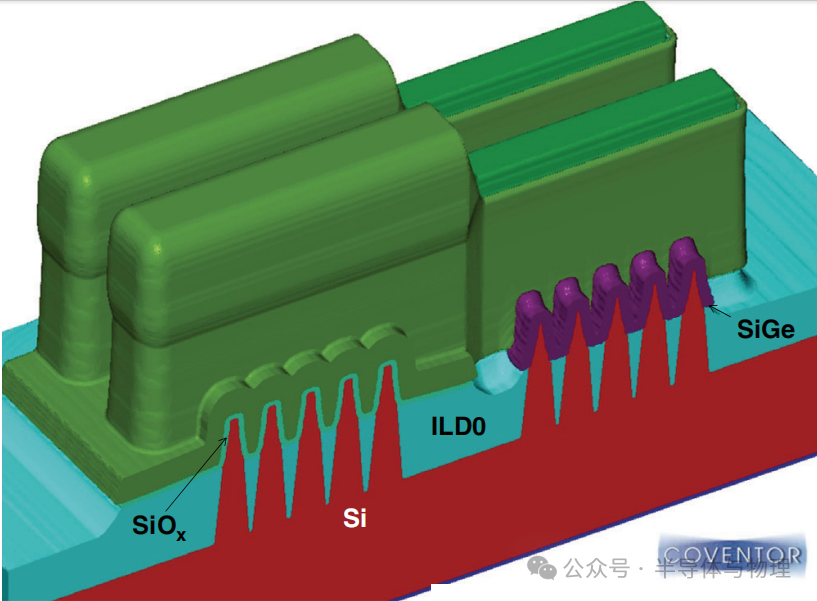

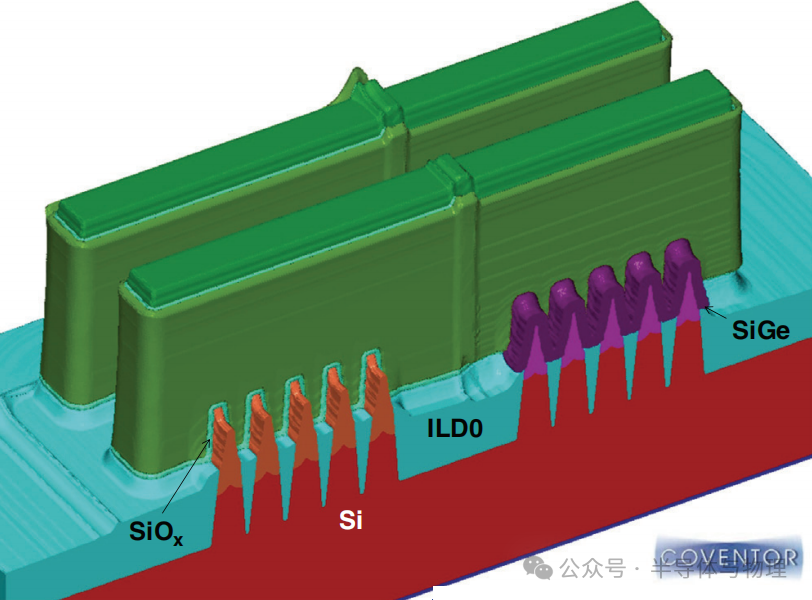

首先,在完成伪栅极结构后的晶圆上进行彻底清洁,以去除任何可能影响后续步骤的污染物。接着,沉积一层薄的侧壁(通常为氧化硅SiOx)芯片制造:薄膜工艺,这层材料作为后续侧壁间隔物的基础,并有助于保护鳍片免受直接损伤。

二、PMOS源漏极形成

PMOS光刻芯片制造:光刻工艺原理与流程

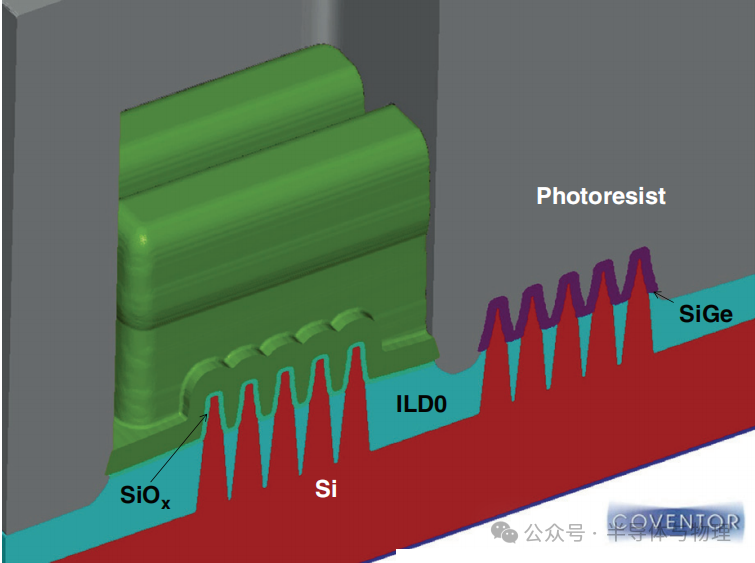

为了允许PMOS源漏极的形成,应用一个PMOS掩模,使得NMOS区域被光刻胶(PR)覆盖。

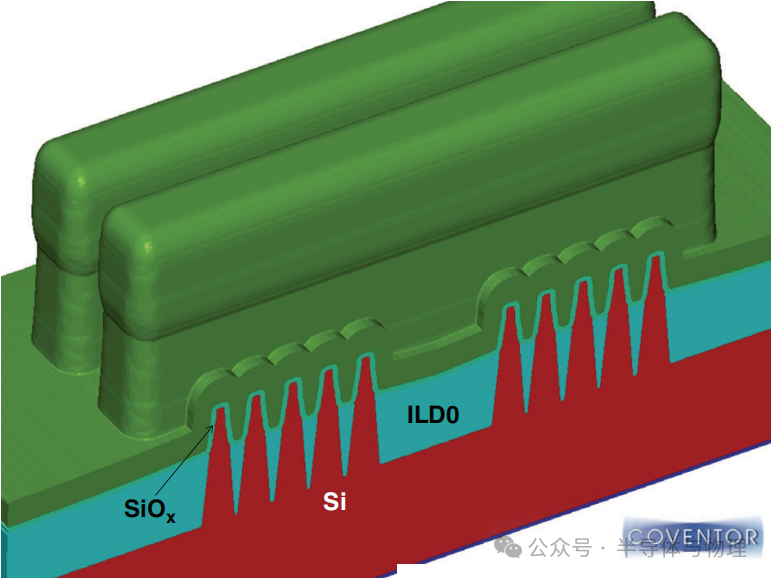

PMOS侧壁间隔物蚀刻与鳍片间隔物移除

在PMOS区域,通过蚀刻去除侧壁间隔物并移除鳍片上的SiO2间隔物。此步骤为后续的选择性外延生长(Selective Epitaxial Growth,芯片制造中的SiGe)做好了准备。

光刻胶剥离与晶圆清洗

完成上述蚀刻后,剥离光刻胶并清洗晶圆,以清除任何残留物质,保证接下来的生长过程不受污染。

硅凹陷与SiGe选择性外延生长

接下来,通过蚀刻使硅表面略微凹陷,然后在这些凹陷处生长重掺杂的p型SiGe。选择性外延生长技术用于在此处形成高质量的SiGe晶体芯片制造中的SiGe,它不仅增加了PMOS器件的载流子迁移率,还提高了其性能。至此,PMOS器件的源漏极形成完毕。

三、NMOS源漏极形成

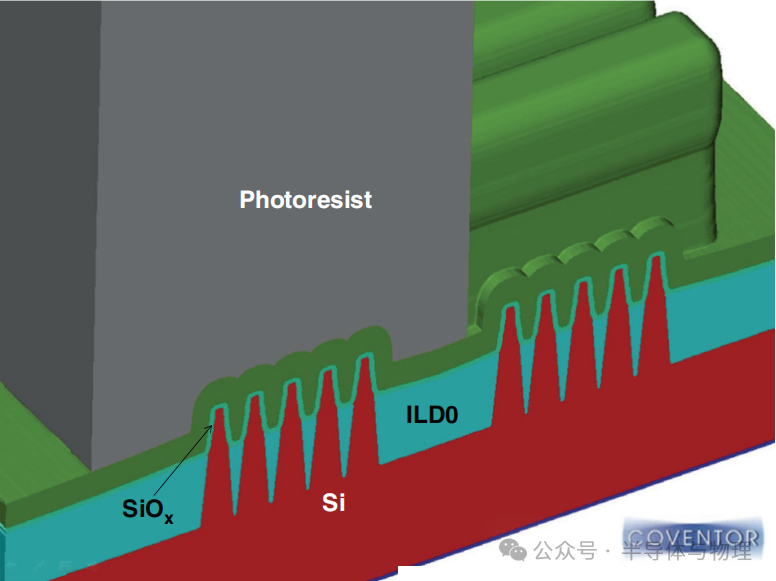

NMOS光刻

接下来,切换到NMOS区域,应用相应的光刻胶掩模,这次是PMOS区域被覆盖,NMOS区域暴露出来。目的是为接下来的NMOS源漏极形成做准备。

NMOS侧壁间隔物蚀刻与鳍片间隔物移除

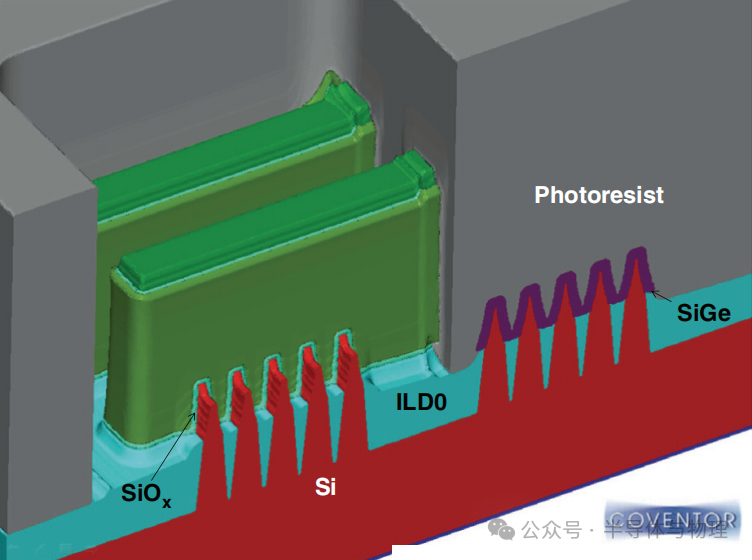

类似于PMOS的处理,蚀刻NMOS侧壁间隔物并移除NMOS鳍片上的间隔物。

这是为了确保接下来的n型离子注入可以准确地定位到目标位置。

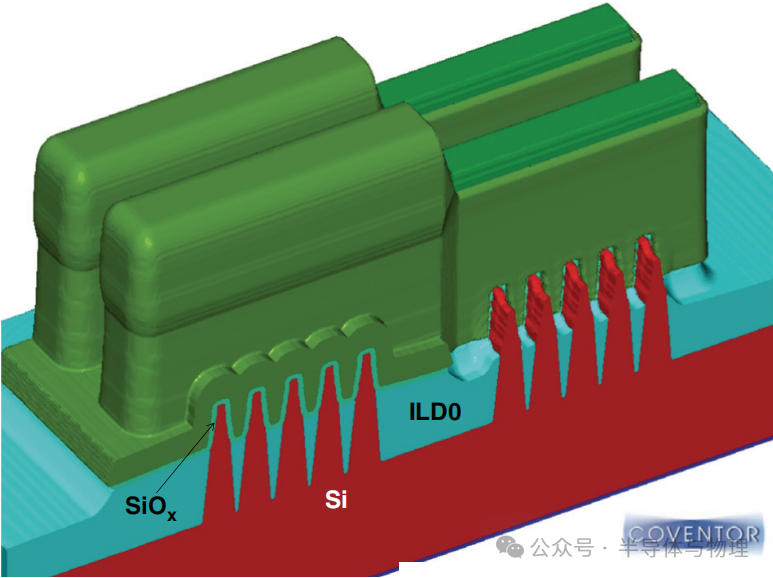

n型离子注入芯片制造:离子注入工艺

执行n型离子注入以重掺杂NMOS源漏极。该步骤旨在将大量的n型杂质引入到硅中,以创建低电阻的源漏区。

光刻胶剥离与晶圆清洗

再次剥离光刻胶并清洗晶圆,确保没有残留物质干扰接下来的退火过程。

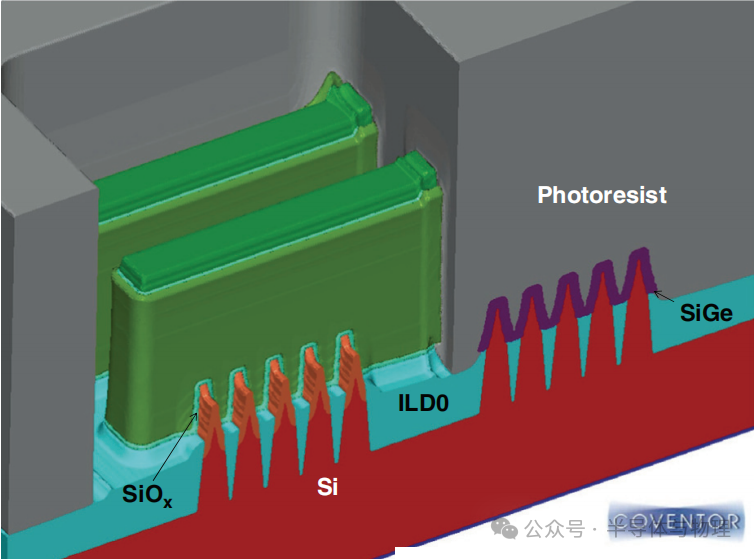

退火芯片制造:退火工艺

最后,通过退火激活掺杂剂。退火过程可以使掺杂原子进入硅晶格的适当位置,从而优化电学特性。

-

漏极

+关注

关注

0文章

35浏览量

11030 -

FinFET

+关注

关注

12文章

262浏览量

92371 -

Process

+关注

关注

0文章

17浏览量

12492

原文标题:FinFet Process Flow-源漏极形成

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用 Neutron 运行eiq_genai_flow时输出错误怎么解决?

抬升源漏技术如何拯救纳米尺度晶体管

选型手册:VS6808DH 共漏极双通道 N 沟道增强型功率 MOSFET 晶体管

NVTFWS002N04XM功率MOSFET技术解析与应用指南

芯片漏印工装

RDS(on)低至8.6mΩ,扬杰推出200V MOSFET Gen2.0系列

CYW20704 的 UART 4 针(TX/RX/CTS/RTS)是什么形式(推拉或漏极开路)吗?

体硅FinFET和SOI FinFET的差异

源漏扩展结构概述

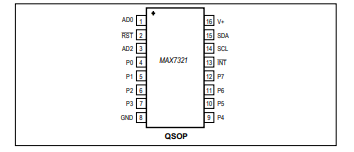

MAX7321 I²C端口扩展器,具有8路漏极开路I/O技术手册

FinFet Process Flow-源漏极是怎样形成的

FinFet Process Flow-源漏极是怎样形成的

评论