源漏扩展结构(Source/Drain Extension,SDE)在控制 MOS 器件的短沟道效应中起到重要作用。SDE(源漏扩展结构)引入了一个浅的源漏扩展区,以连接沟道和源漏区域。结深的微缩归因于 SDE 深度的降低。随着 CMOS尺寸的降低,为控制短沟道效应,结深也需要相应的降低。然而,降低源漏扩展区的深度会导致更高的电阻。这两个互相矛盾的趋势要求新的工艺技术能够在更浅的区域形成高活化和低扩散的高浓度结。

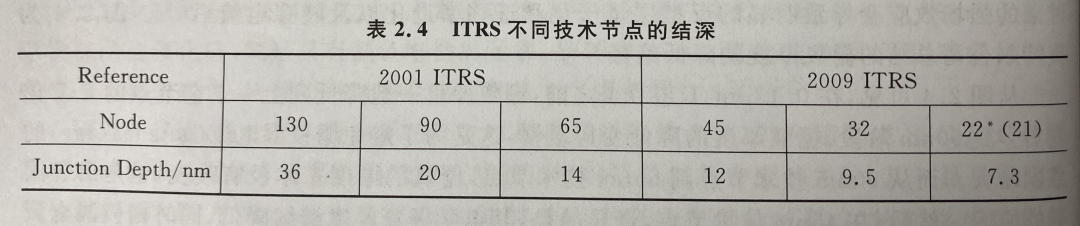

根据ITRS 提供的数据,不同技术节点的结深归纳如表2.4所示。

结(junction)的制造工艺包含离子注入工艺和注入后退火工艺。离子注入需要小心控制以在最小化的注入损伤下,在近表面获得高掺杂浓度。为满足上述需求,新的工艺技术,比如无定型化技术、分子离子注入技术和冷注入技术,已经得到应用。为得到掺杂剂的高活化和有限的掺杂剂扩散,注入后退火的热预算非常关键。由于将掺杂原子置入晶格中的活化过程相比掺杂剂的扩散过程需要更高的活化能,快速升降温的热过程有利于高活化和低扩散。针对该目的而开发的毫秒级和亚毫秒级的退火技术已经应用于大规模工业生产。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

工艺

+关注

关注

4文章

720浏览量

30390 -

制造工艺

+关注

关注

2文章

215浏览量

21315 -

MOS

+关注

关注

32文章

1757浏览量

101220

原文标题:源漏工程

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

MOS管漏源极导通的原因是什么?

普通N MOS管给栅极一个高电压 ,漏极一个低电压,漏源极就能导通。这个GS之间加了背靠背的稳压管,给栅极一个4-10V的电压,漏源极不能导

发表于 06-21 13:30

漏源电压VDS相关资料下载

1、电压负载 在具有直流稳压大功率电路的应用中,通常首先考虑选择漏源电压VDS。这里的理由是,在实际工作环境中,MOSFET的最大峰值漏极-源极电压小于器件规格的标称

发表于 11-12 08:12

漏源电压振荡严重

全桥单向DC-DC变换器中,MOSFET漏源电压波形如图所示振荡很严重,这种现象在1kHz的时候不明显,50khz的时候如图所示很明显,请问是为什么?

发表于 04-25 11:19

PNP与NPN哪个是“源”与”漏“的浑水

源型与漏型是PNP与NPN放大电路的电流流向的一种形象化表述,最初是由日系PLC引入这样的简称,在日系语系用中文字表达的一种方式,在原来的中国学校教育中并不怎么使用“源型”与“漏型”这

栅极源极漏极怎么区分?漏极 源极 栅极相当于三极管的哪极?

什么是漏极?什么是源极?什么是栅极?栅极源极漏极怎么区分?漏极 源极 栅极相当于三极管的哪极?

mos芯片源极漏极栅极在哪 mos管怎么判断漏栅源极

之间的连接是理解该器件工作原理的关键。 MOS管结构简介: MOS管是由一片半导体材料(通常是硅)构成的,通过在硅片上掺杂不同类型的杂质形成两个PN结。这些杂质掺入区域形成了源极和漏极,而栅极是通过在硅片上形成一层金属(通常是铝

MOS管源极和漏极是什么意思

(Source, S)和漏极(Drain, D)是两个关键的电极,它们与栅极(Gate, G)共同构成了MOS管的基本结构。以下是对MOS管源极和漏极的详细解释,包括它们的定义、功能、

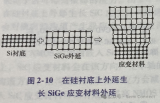

源漏嵌入SiC应变技术简介

源漏区嵌入SiC 应变技术被广泛用于提高90nm 及以下工艺制程 NMOS 的速度,它是通过外延生长技术在源漏嵌入 SiC 应变材料,利用硅和碳晶格常数不同,从而对沟道和衬底硅产生应力

晶体管的漏极与源极有什么区别

在探讨晶体管的漏极(Drain)与源极(Source)的区别时,我们首先需要明确晶体管的基本结构和工作原理。晶体管,尤其是场效应晶体管(FET),是一种通过控制输入回路的电场效应来控制输出回路电流的电子器件。在FET中,

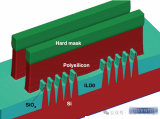

FinFet Process Flow-源漏极是怎样形成的

本文介绍了FinFet Process Flow-源漏极是怎样形成的。 在FinFET制造工艺中,当完成伪栅极结构后,接下来的关键步骤是形成源漏

源漏扩展结构概述

源漏扩展结构概述

评论