无论是平面栅还是沟槽栅,SiC MOSFET都采用垂直导电结构,其纵向(从漏极到源极)的层状结构是通用的,如下图所示:

图1. 沟槽型--英飞凌非对称沟栅CoolSiC MOSFET

图2. 平面栅型MOSFET

N-外延层(Drift Layer):低掺杂,用于承受高阻断电压。

P-body区:P型阱区,通过离子注入形成。其上方是源极的N+区。

栅极(Gate):在SiO2绝缘层(栅氧)之上,用于控制沟道导通。

源极(Source):与P-body区和N+源区相连。

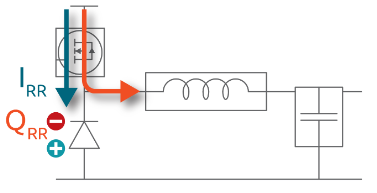

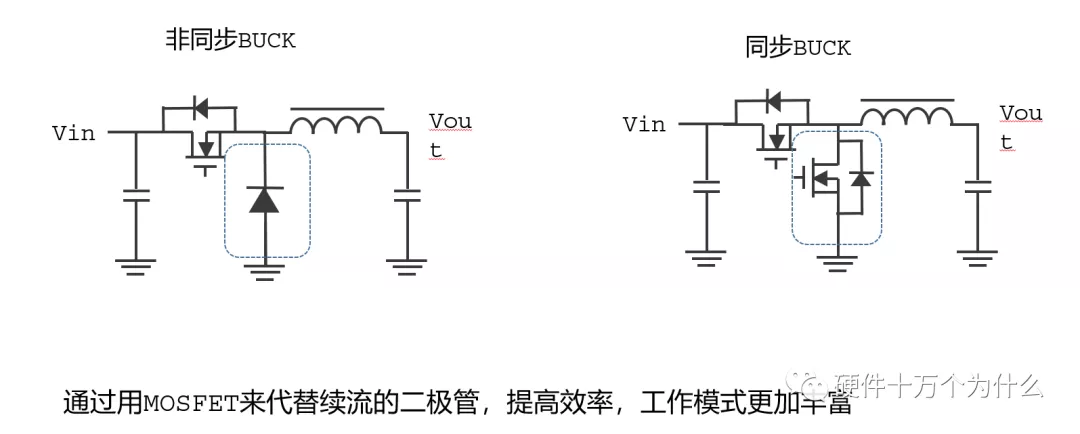

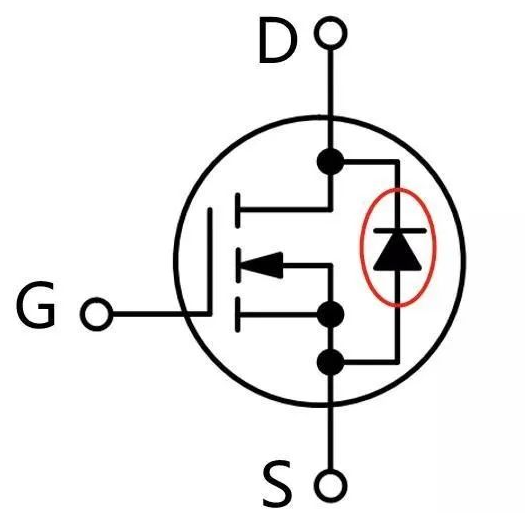

体二极管(Body Diode)也被称为寄生二极管或内置二极管。它是由MOSFET本身结构“天然”形成的一个PN结二极管。观察结构图,P-body区(P型)和 N- 外延层(N型)直接接触,自然而然地构成了一个PN结。

SiC的体二极管特性:

1.

反向恢复电荷小

由于SiC具有比Si更宽的禁带宽度,使得SiC具有极低的本征载流子浓度和极高的临界击穿电场。高临界击穿电场允许SiC MOSFET的漂移区做得更薄、掺杂更高。低本征载流子浓度和高掺杂薄漂移区共同作用,使得PN结正向导通时注入和储存的少数载流子总量非常少。同时,SiC的载流子寿命也更短,使得这些本就不多的储存电荷复合速度极快。因此,当SiC MOSFET的体二极管从正向偏置切换到反向偏置时,需要被移除的电荷(Qrr)极少,且移除/复合的速度极快。此外,空间电荷区产生电容Coss。关断过程中Coss被充电,达到Vdc。PN二极管的这个关断过程通常称为反向恢复,由双极电流和电容电流驱动。因此,SiC反向恢复电流(Irr)相较于Si器件而言小很多,反向恢复时间短,拖尾电流小。但是SiC体二极管仍旧存在一定的反向恢复损耗,可以从电路角度进一步优化。

2.

导通压降较高

同样因为SiC有更宽的禁带宽度,导致其PN结的开启电压较高,理论上,SiC PN结的开启电压就在2.5V - 3V左右,远高于硅二极管约0.7V的开启电压。

此外,从平面栅型SiC MOSFET的结构中可以看到,体二极管的电流路径是:源极 → P-body → N- 漂移区 → N+ 衬底→漏极。其中,P-body区为了与其他区域形成良好的PN结,其掺杂浓度和深度经过优化,但通常电阻较高。电流流经这个高阻区会产生比较大的压降。另外,由于内部少数载流子寿命非常短,当体二极管导通时,注入到漂移区的少数载流子(空穴)还来不及进行充分的电导调制(Conductivity Modulation)来降低漂移区的电阻,就被迅速复合掉了。因此,漂移区无法像在IGBT或硅PiN二极管中那样电阻大幅下降,仍然保持较高的电阻率。传统SiC体二极管的高压降是“高开启电压”和“高串联电阻”共同作用的结果。这导致其导通损耗很大。

02

死区时间的选择

死区时间是为了防止逆变桥或半桥电路中上下两个开关管同时导通,造成“直通”(Shoot-through)而短路烧毁器件。在死区时间内,负载电流会通过互补开关管的体二极管进行续流。死区时间的选择主要从以下两个方面影响SiC MOSFET的损耗表现:

1

体二极管在死区时间内,在其漂移区建立双极等离子体。当死区时间设置为极短时间时,漂移区的等离子体在体二极管关断时可能还未完全建立起来。因此,必须从漂移区消除的电荷量比死区时间很长时要少,即反向恢复电荷较少。

2

如果死区时间较长,体二极管持续导通续流,由于Vf较高,会导致较大导通损耗。

应用电路中的典型死区时间在150ns至1µs之间。图3显示了死区时间较短的影响。从图中可以看出,与死区时间为1µs相比,死区时间为300ns时,反向恢复电荷显著减少。漂移区的等离子体浓度在死区时间为500ns至1µs时达到饱和。当td≥1µs,可以看出反向恢复特性无差异。缩短死区时间,是提升SiC MOSFET性能的有效方式。

图3:在T=150°C条件下,不同死区时间下的快速体二极管关断。

英飞凌CoolSiC MOSFET G2通过非对称沟槽栅与深P阱设计、优化寄生电容等手段,其增强型体二极管的反向恢复特性得到改善,允许系统采用更短的死区时间(可短至 150ns ),但实际应用中仍需仔细评估以避免桥臂直通风险。

首先,死区时间必须大于开关管(如低边LS MOSFET)的关断延迟与续流管(如高边HS MOSFET)的开通延迟之间的差值,并考虑一定裕量。其次,死区时间的设定还需要考虑驱动信号的传输延时。因此,死区时间的选择可以参考如下公式:

td_off_max为最大关断时间,td_on_min为最小开通时间,tpdd_max为驱动信号的最大传输延迟时间,tpdd_min为驱动信号的最小传输延时时间,系数1.2为裕量。

实际使用时,可根据实际的工况提前用示波器进行测量:

1.

初始设置与安全基准

设定保守值:参考数据手册和上述公式,从一个较长的死区时间开始。

连接示波器:建议使用四个通道,分别测量同一桥臂上管和下管的栅源极电压(Vgs),下管的漏源极电压(Vds)以及使用电流探头观察漏极电流(Id)。

捕获基准波形:在安全条件下,捕获一个完整的开关周期波形。此时波形应干净,无异常尖峰。

2.

逐步优化与临界点判断

逐步减小死区时间:以10-20ns为步长,逐步减小死区时间。每调整一次,都需用示波器仔细观察开关瞬间的波形。

观察关键“危险信号”:

Vgs交叠:放大观察上下管Vgs的上升沿和下降沿。绝对禁止出现两者同时高于器件导通阈值电压的情况。

Vds/Id异常:关注开关瞬间的Vds和Id波形。如果出现异常的电压凹陷或巨大的电流尖峰,是发生直通的明确证据。

找到临界点:持续减小死区时间,直到示波器上刚刚开始出现上述危险的迹象(如Vgs波形几乎贴在一起,Vds出现微小毛刺)。这个点就是安全的极限。

图4给出了死区的临界点仿真示意图,其中虚线所示的波形为安全波形,实线所示的波形由于死区时间过短发生了直通的问题。直通发生时,SiC瞬态电流上升明显,开关损耗也有大幅度的增加,应该避免这种情况的发生。

图4:死区设置临界点仿真示意图

3.

确定最优值并全工况验证

增加设计余量:在找到的临界死区时间值上,增加20%-50%的余量。这个余量用于应对温度变化、器件离散性、栅极驱动波动等因素,确保系统长期可靠运行。

全工况验证:将设置好的死区时间在不同条件下进行测试,包括轻重负载、冷机热机状态等。确保在所有极端情况下,系统均能稳定工作,无直通风险。

-

MOSFET

+关注

关注

151文章

10795浏览量

234870 -

SiC

+关注

关注

32文章

3850浏览量

70090 -

体二极管

+关注

关注

0文章

70浏览量

7287

发布评论请先 登录

SCT30N120内部体二极管能够像mosfet一样处理电流吗?

碳化硅SiC MOSFET:低导通电阻和高可靠性的肖特基势垒二极管

SiC-MOSFET体二极管的特性说明

SiC MOSFET 体二极管特性及死区时间选择

SiC MOSFET 体二极管特性及死区时间选择

评论