文章来源:半导体与物理

原文作者:jjfly686

本文简单介绍了体硅FinFET和SOI FinFET之间的结构差异与工艺差异。

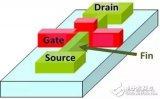

在半导体制造领域,晶体管结构的选择如同建筑中的地基设计,直接决定了芯片的性能上限与能效边界。当制程节点推进到22nm以下时,传统平面晶体管已无法满足需求,鳍式场效应晶体管(FinFET) 以其三维立体结构成为行业主流。然而在FinFET阵营内部,一场关于“地基材料”的技术路线竞争悄然展开——这便是Bulk Silicon(体硅) 与SOI(绝缘体上硅) 两大技术的对决。这场对决不仅关乎性能极限的突破,更牵动着芯片成本与可靠性的微妙平衡,成为半导体行业持续演进的关键战场。

结构差异:从物理基础看技术分野

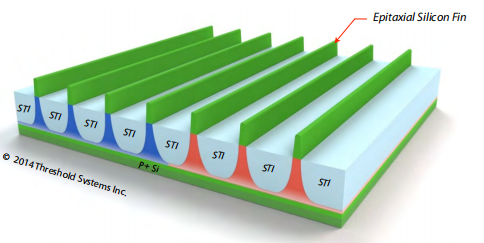

Bulk Silicon FinFET:深槽隔离的工程杰作

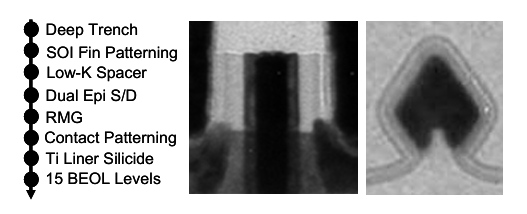

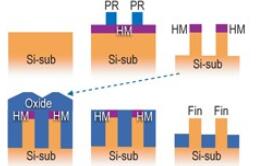

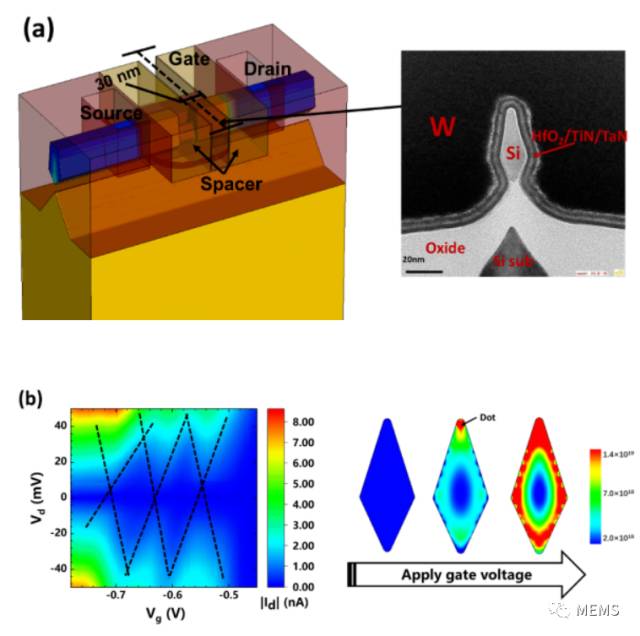

Bulk Silicon FinFET基于常规硅晶圆制造,其核心挑战在于如何在导电的硅衬底上实现相邻晶体管间的有效隔离。为实现这一目标,工程师们开发了浅沟槽隔离(STI) 技术:通过等离子刻蚀在硅衬底上挖出深达数百纳米的沟槽;填充二氧化硅(SiO₂) 或氮化硅(Si₃N₄) 作为绝缘材料;在隔离区域之间形成垂直硅鳍(典型高度30-50nm,宽度5-10nm);栅极从三面包裹硅鳍,增强沟道控制能力。

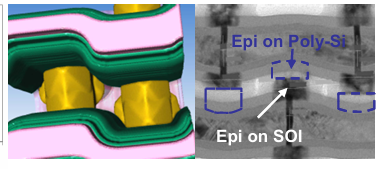

这一结构的复杂性在截面图中显露无遗:硅鳍底部与衬底直接相连,需要通过精密掺杂在鳍基形成隔离层,防止漏电流向衬底扩散。随着鳍高度的增加,掺杂均匀性控制成为难点,可能引发随机掺杂涨落(RDF) 导致的阈值电压波动。

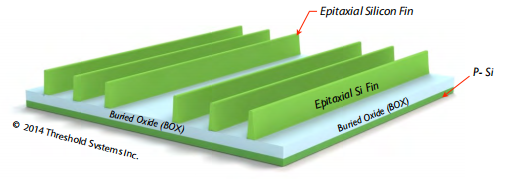

SOI FinFET:天然绝缘的优雅设计

SOI FinFET则构建在特殊的三层晶圆上:顶层硅(~10nm):用于刻蚀形成晶体管鳍片;埋氧层(BOX)(~25nm):二氧化硅绝缘层,隔绝衬底;基底硅:仅起机械支撑作用。

这种结构带来了革命性简化:无需STI刻蚀:埋氧层自然隔离相邻器件;消除鳍基掺杂:BOX层阻挡垂直漏电路径;硅鳍全耗尽:超薄顶层硅确保栅极完全控制沟道。

从电子显微镜图像可见,SOI FinFET的硅鳍如精致的雕塑般矗立在光滑的氧化层上,与Bulk Silicon中复杂的隔离结构形成鲜明对比。

| 衬底材料 | 单层硅晶圆 | 硅/二氧化硅/硅复合晶圆 |

| 隔离方式 | 浅沟槽隔离(STI) | 埋氧层(BOX)天然隔离 |

| 硅鳍连接 | 与衬底直接相连 | 通过BOX层与衬底绝缘 |

| 鳍高 | 30-50nm | 20-40nm |

| 关键掺杂区 | 鳍基防漏电掺杂层 | 无需特殊掺杂 |

| 特性 | Bulk Silicon FinFET | SOI FinFET |

|---|

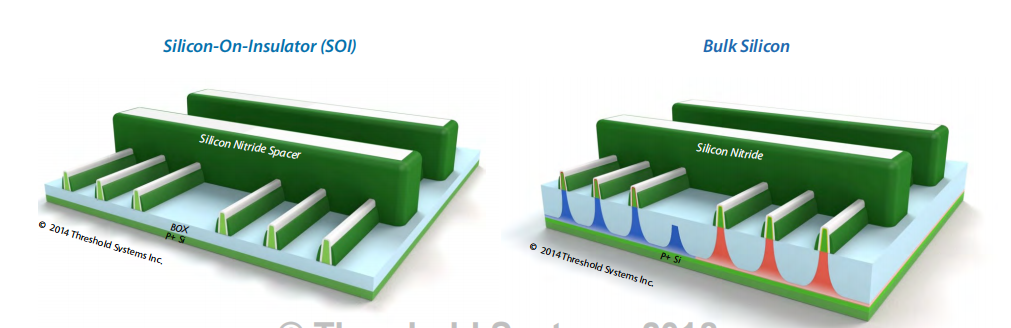

工艺复杂度:从制造流程看成本控制

Bulk Silicon FinFET:繁琐但成熟的前端工艺

Bulk Silicon FinFET的制造前端包含多个高精度步骤:

1、深槽刻蚀:反应离子刻蚀(RIE)形成STI沟槽,深宽比达5:1以上;

2、隔离填充:原子层沉积(ALD)氮化硅+二氧化硅填充沟槽;

3、化学机械抛光(CMP):去除多余隔离材料,实现全局平坦化;

4、鳍基注入:倾斜离子注入形成P/N阱与防穿通掺杂层;

5、硅鳍刻蚀:多重曝光光刻+刻蚀定义鳍阵列;

这些步骤不仅增加5-7道光罩,更引入掺杂均匀性和刻蚀深宽比等控制难点。特别是鳍基注入环节,需精确控制掺杂轮廓以平衡泄漏与性能,退火过程易导致杂质扩散,影响阈值电压稳定性。

SOI FinFET:简化的前端流程

SOI工艺大幅简化前端制程:

跳过STI:BOX层已实现天然隔离,仅需定义有源区图形;

省略鳍基注入:埋氧层阻断漏电,无需复杂掺杂工程;

直接鳍刻蚀:在超薄顶层硅上一步形成全耗尽硅鳍;

这种简化使SOI FinFET的前端工艺步骤减少约30%,显著降低成本。

-

半导体

+关注

关注

336文章

30052浏览量

259002 -

晶体管

+关注

关注

78文章

10291浏览量

146506 -

FinFET

+关注

关注

12文章

259浏览量

92054

原文标题:FinFET技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体厂商产能布局 FinFET与FD-SOI工艺大PK

帮你看懂已经全面攻占iPhone的FinFET

判断FinFET、FD-SOI与平面半导体制程的市场版图还早

详解先进的半导体工艺之FinFET

FD-SOI(全耗尽型绝缘层上硅)

请问FinFET在系统级意味着什么?

SOI和体硅集成电路工艺平台互补问题的探讨

FD-SOI元件与FinFET接近实用化的不断发布

什么是FinFET?FinFET的工作原理是什么?

FD SOI生态系统逐步完善 与FinFET势均力敌

FinFET到了历史的尽头?

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应

体硅FinFET和SOI FinFET的差异

体硅FinFET和SOI FinFET的差异

评论