先进封装技术(Semiconductor Advanced Packaging) - 1 混合键合技术(上)

先进封装技术(Semiconductor Advanced Packaging) - 2 混合键合技术(下)

先进封装技术(Semiconductor Advanced Packaging) - 3 Chiplet 异构集成(上)

先进封装技术(Semiconductor Advanced Packaging) - 4 Chiplet 异构集成(下)

先进封装技术(Semiconductor Advanced Packaging) - 5 TSV 异构集成与等效热仿真

先进封装技术(Semiconductor Advanced Packaging) - 6 扇出型晶圆级封装(FOWLP)

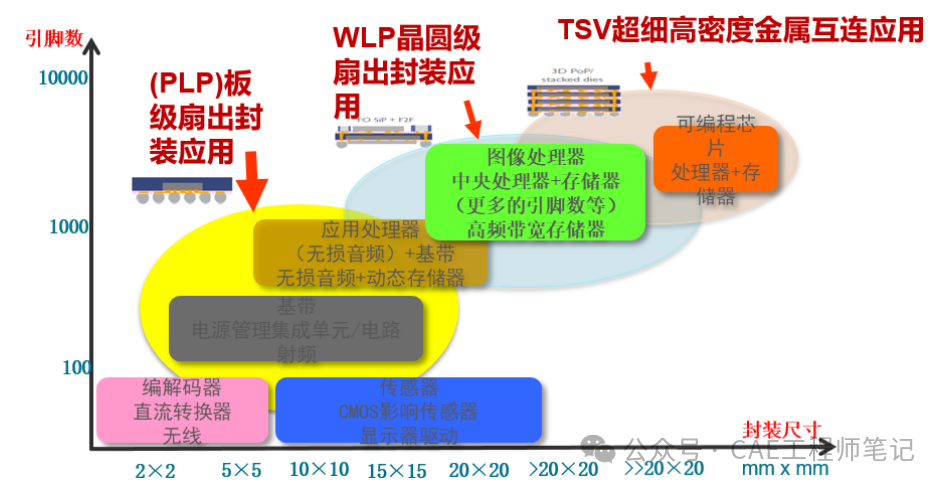

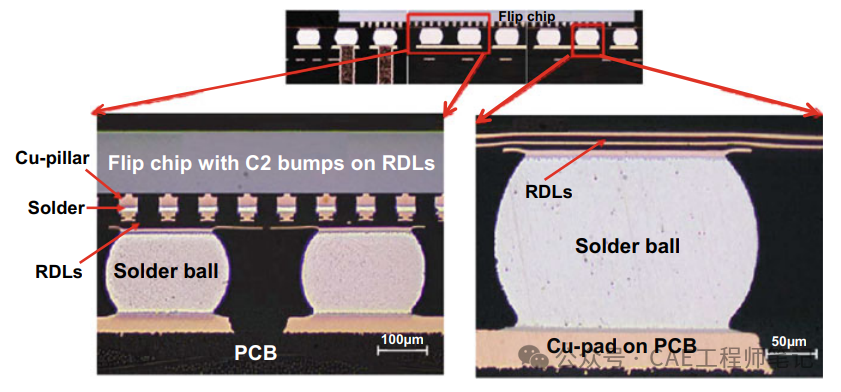

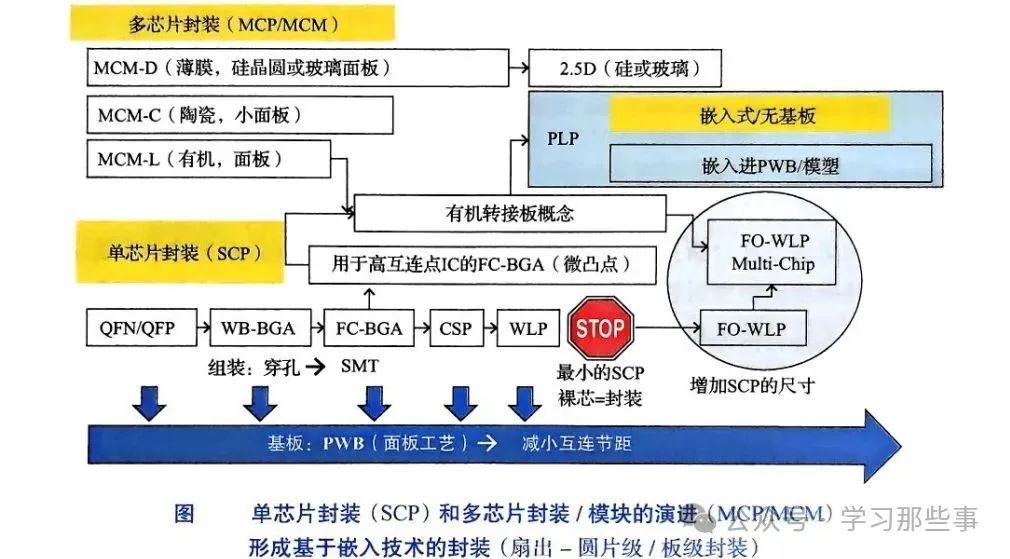

封装技术从早期到现在的发展都是为了提高半导体相关产品的价值,不断增加芯片的功能,增加 I/O 数从而将更多的功能整合到终端产品中去。但是,由于摩尔定律极限的不断逼近使得电子产品的性能已经不能再通过缩小芯片的尺寸来实现,甚至不断增多的 I/O 引脚数已经使得基板下面不能再容纳更多数目的锡球,而如果通过将锡球的尺寸减小这又将带来成本的不断增加。因此,扇出型封装技术的提出就是为了突破芯片与基板面积之间所带来的限制。

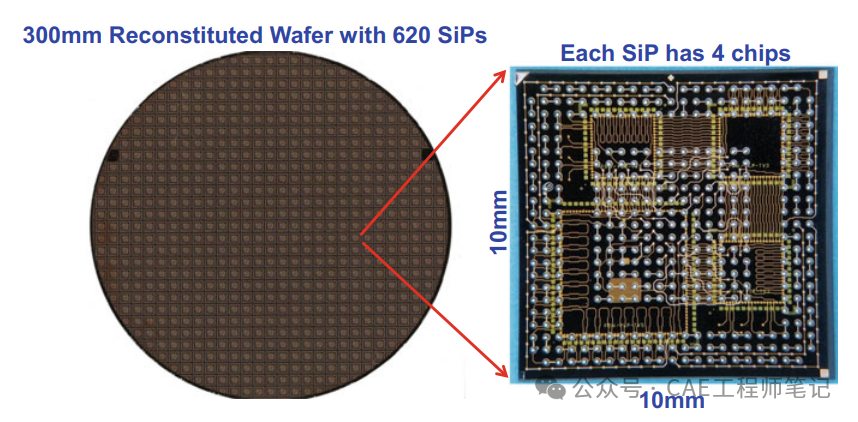

在此背景下,FOWLP(Fan-Out Wafer Level Package)作为一种新兴的封装技术,在商业领域得到了广泛的使用。该技术具有完善的生产过程,可满足各种不断变化的需求。2016 年,苹果公司将 FOWLP 成功地运用到了其最具代表性的产品 iPhone7 的处理器和模块中。

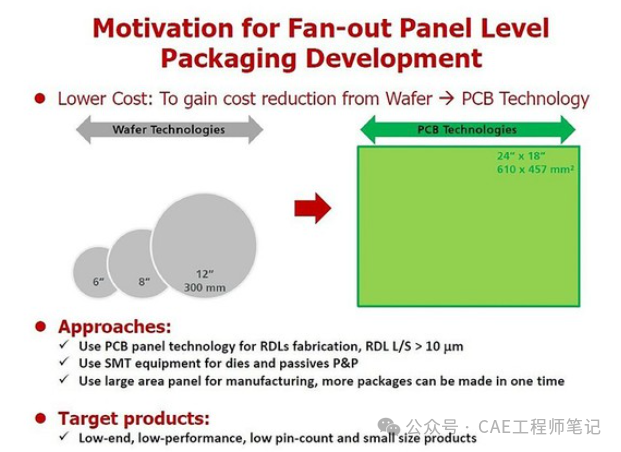

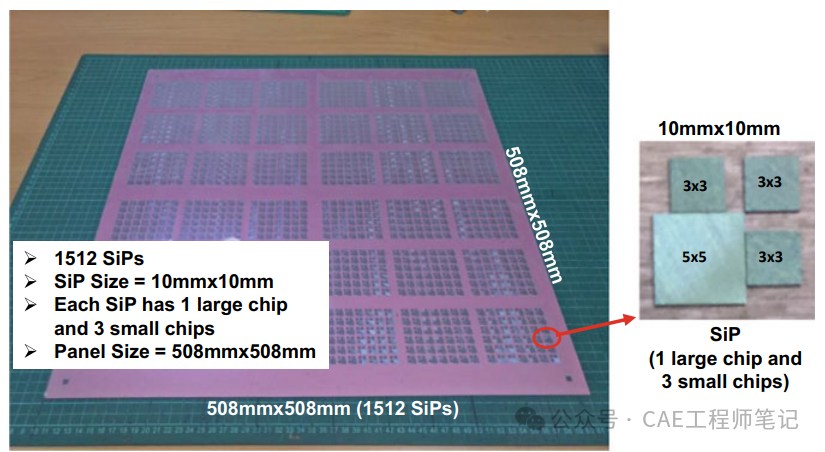

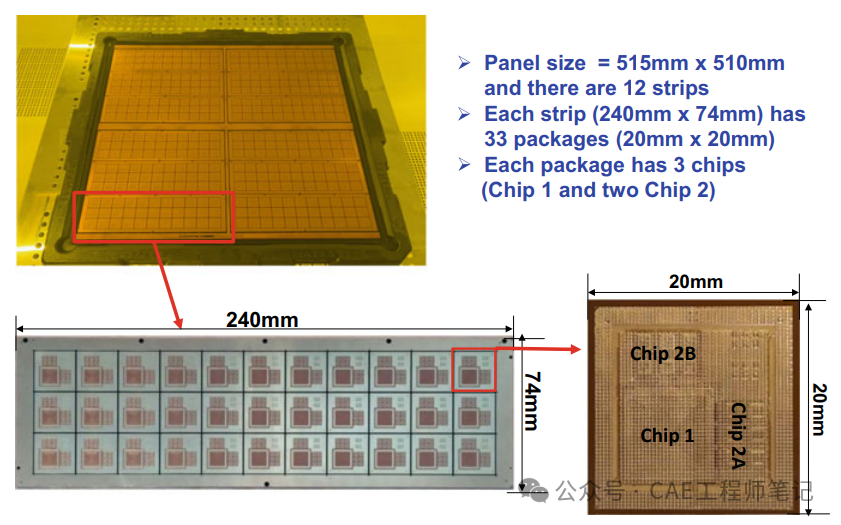

目前扇出型晶圆级封装技术主流的晶圆尺寸为 12 寸,但是为了能在更低的生产成本下有更高的实际产出量,生产方向朝着 18 寸晶圆进行,但是生产过程中也存在很多困难,比如制造 18 寸晶圆所使用的设备需要更新换代,这就需要投入大量的资金,且生产过程中的工艺要求也亟需有所提升。因此,工程师们便考虑通过使用尺寸更大的面板级封装去代替晶圆级封装,这样可以更好地利用其封装规模大和使用效率高的优势。

采用面板级封装去替代晶圆级封装,若在工艺技术已经完备的情况下,其生产成本可以有很大幅度的降低。同时相比较晶圆级封装来说,面板级封装也有着更加高的成品合格率。此外,面板级封装生产所使用的生产设备、技术支持和所涉及到的专业知识都和晶圆级封装以及 PCB 板大相径庭,这也使得面板级封装具有更加良好的前景和发展空间。随着多种因素的共同作用,扇出型板级封装(Fan-out Panel Level Packaging, FOPLP)迅速发展起来。

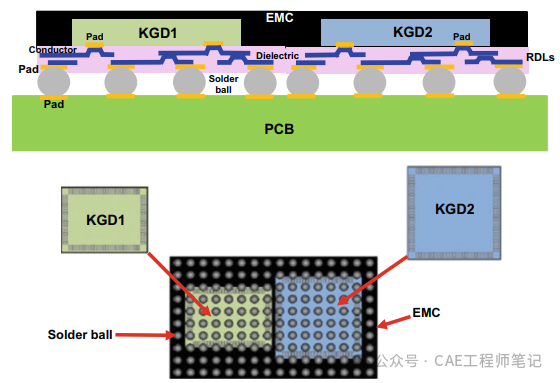

FOPLP 是相对于 FOWLP 来说的,它将晶圆基板替换为面板基板,并采用扇出型封装的方式进行封装,从而实现更高效、更精确的产品。FOPLP 所使用的工艺生产方法与 FOWLP 相似,不同的是FOPLP 具有更高的利用率、更低成本的潜力。

FOPLP 与 FOWLP 并不是竞争关系,而是相辅相成,目前行业内 FOWLP应用于 I/O 密度高和细线宽/线距的高端应用,而扇出型板级封装 FOPLP则关注于 I/O 密度低和粗线宽/线距的低端或中端应用,这样 FOPLP 可以更好的发挥成本优势,基于扇出型板级封装 FOPLP 技术,可以实现更高的封装组件密度和性能。

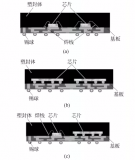

FOPLP Chip First 工艺通常有 Face up 与 Face down两种形式。

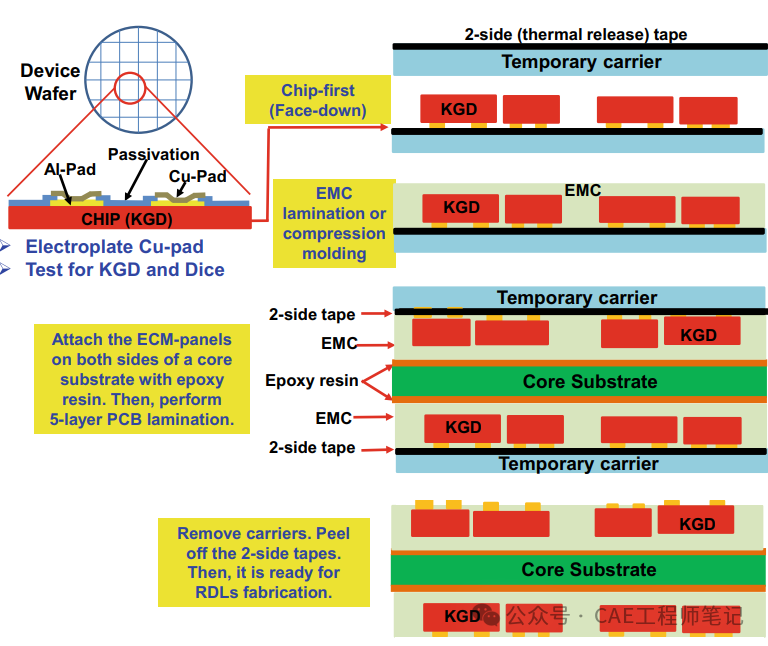

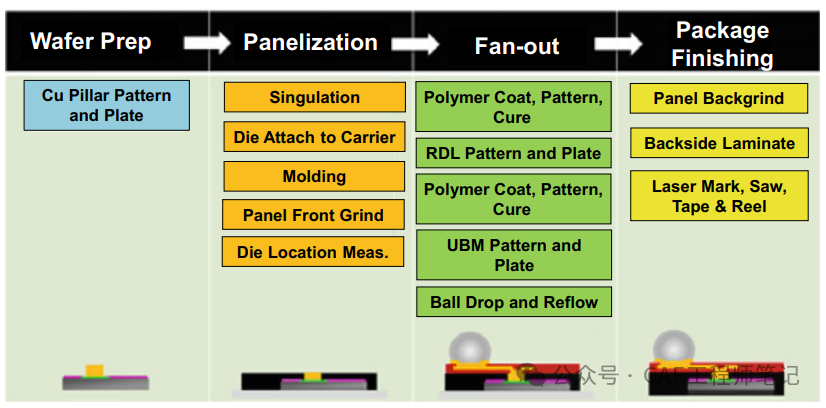

Chip-First and Face-Down

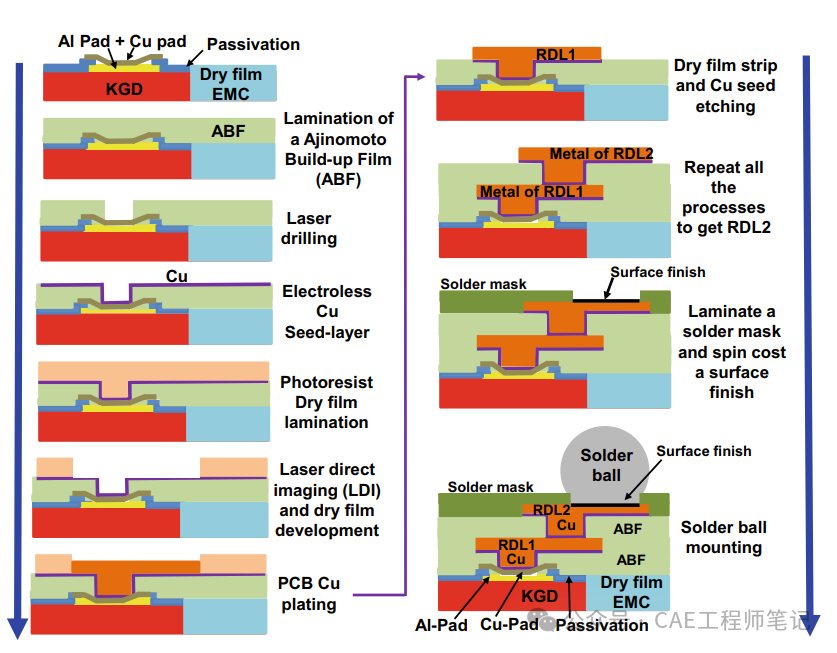

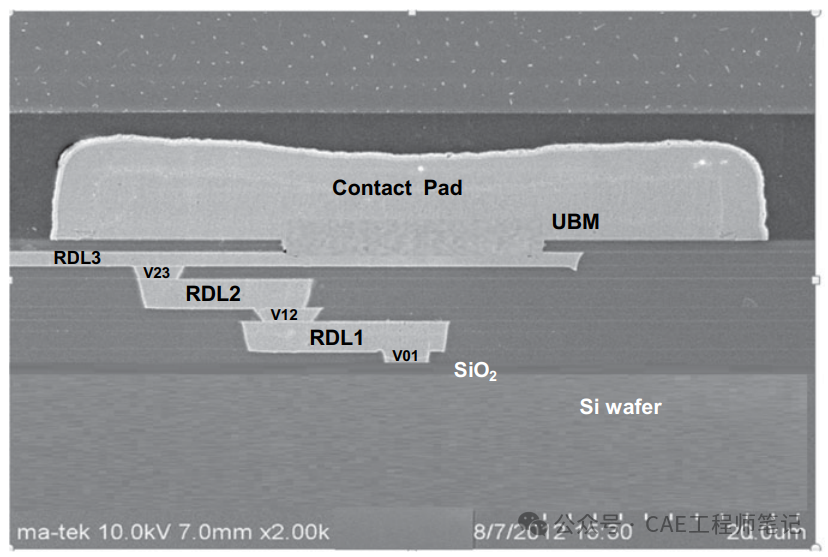

对于 Face down 来说,芯片 I/O 面朝下,粘贴在附带临时键合胶的载板上,然后进行塑封固化和移除载板,接着在芯片 I/O 面热压一层介电层,对 I/O 口处进行激光开孔,露出芯片 I/O 口并清除残余介电层,后续采用真空溅射生成 Ti/Cu 种子层,在种子层上热压一层干膜,进行曝光、显影、电镀做出线路层,最后进行退膜处理,除去多余种子层,在线路层上覆盖感光油墨以及切割成单个封装体。

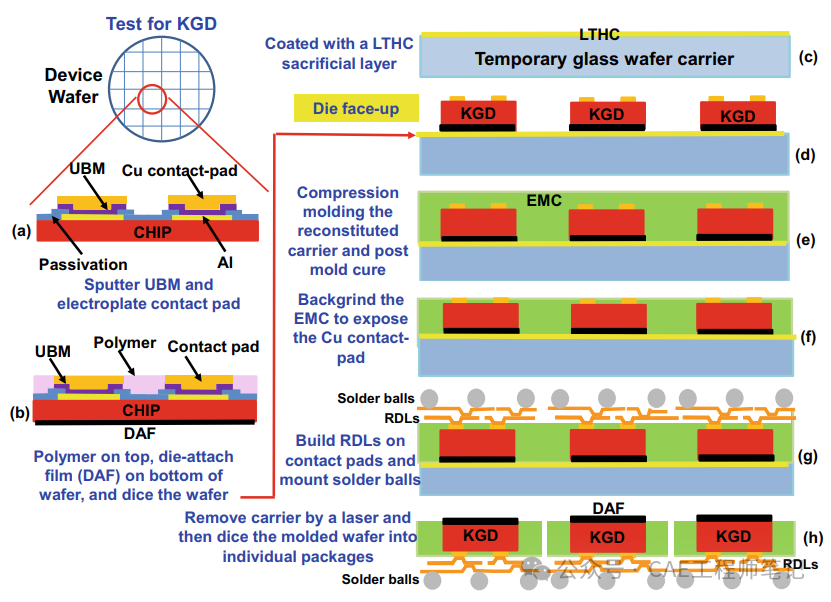

Chip-First and Face-Up

对于 Face up 来说,芯片面朝上粘贴在临时键合胶上,但此处芯片 I/O 口需先具有铜柱,然后进行塑封固化和研磨露出铜柱,接着在铜柱上热压一层介电层,对 I/O 口处进行激光开孔,露出芯片 I/O 口并清除残余介电层,后续采用真空溅射生成 Ti/Cu 种子层,在种子层上热压一层干膜,进行曝光、显影、电镀做出线路层,最后进行退膜处理,除去多余种子层,在线路层上覆盖感光油墨以及切割成单个封装体。

以上两种 Chip First 封装工艺中存在以下几项挑战性问题:

其封装产量由 RDL 的生产良率决定;

芯片表面的 I/O 间距会受到芯片与 RDL 之间对准误差的限制;

重构晶圆中需要可以低温固化的树脂,可能会降低封装可靠性;

RDL 的工艺制程一般都在 10 µm 以下,在制作 RDL 前,重构晶圆的轻微翘曲或芯片偏移均会严重影响 RDL 的生产良率;

一旦发现有部分 RDL 损坏,损坏部分的RDL 对应的 KGDs 也无法再利用,容易造成资源的浪费。

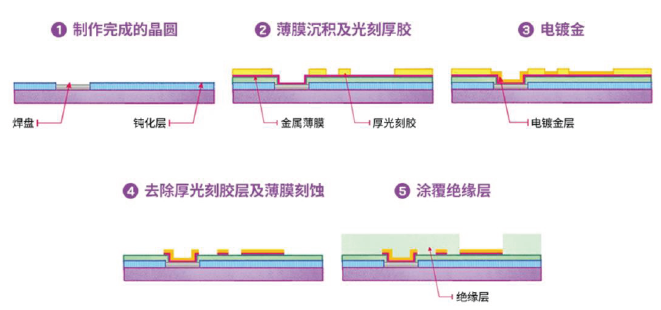

为了克服这些挑战,Deca technologies 公司在 2012 年提出了芯片后装或 RDL 先装 (Chip-Last or RDL-First) 的技术方案,这项技术是带有馈通转接板的智能芯片互连技术(SMAFTI)的基础。

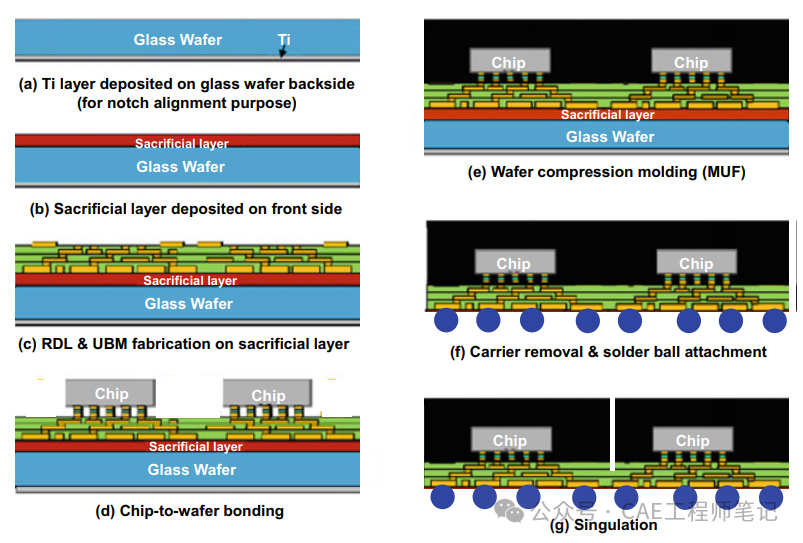

Chip-Last or RDL-First

首先,在平坦的临时载板上制作 RDL,可以消除前端工艺中翘曲带来的影响;其次将 KGDs 以 I/O 面朝下的方式与 RDL 进行对准互连,完成芯片到晶圆(D2W)的键合工艺后;再使用 EMC 进行固化塑封处理,随后将临时载板去除;最后将焊球安装在底部的 RDL 上并将重构晶圆切割成单独的封装。

相较于 Chip-First 的扇出型封装技术,Chip-Last or RDL-First 技术中每一步工艺的难度都比较大,且这项技术需要更多的材料、设备、生产场地和技术人员,其生产成本非常高,并也有可能导致更大的产能损失。因此,该技术通常只应用于要求超高密度封装和超高性能的产品中,如高端服务器和人工智能。

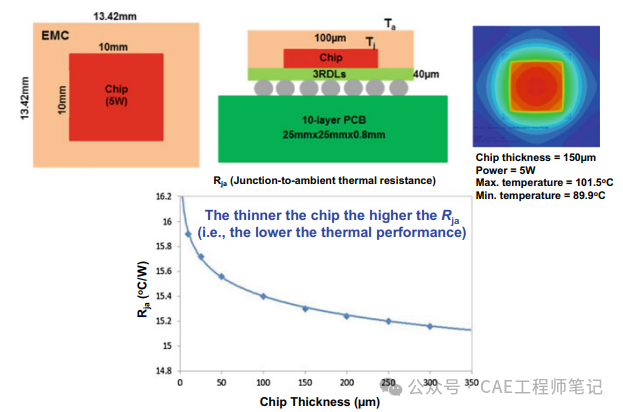

由于 Fan-out 封装结构本身具有厚度更薄、密度更高等特征,也给FOPLP 带来了诸多考验。

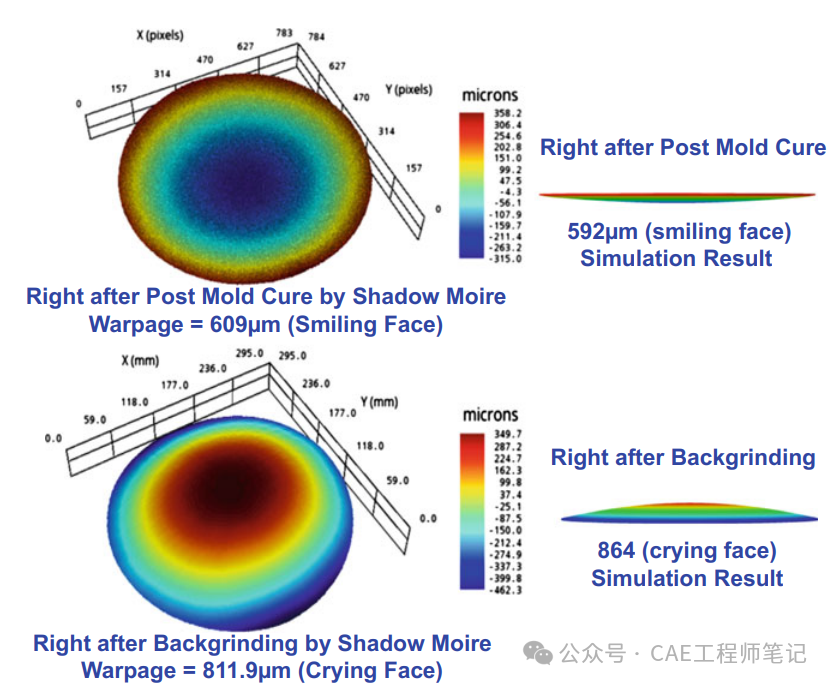

工艺翘曲:在制造工艺过程中的翘曲行为是扇出型封装在普及过程中面临的一个重大挑战。由于不同材料的热膨胀系数并不完全一致,在生产工艺中经历升温和降温时,不同材料受热膨胀和冷却收缩的程度均不一样,从而导致的热失配应力是翘曲产生的主要原因。FOPLP 由于具有面积大而厚度小的特点,使得整个组件抵抗翘曲的能力较低,过大的工艺翘曲会严重影响封装的生产良率以及无法进一步减小 RDL 的线宽和线距,因而是 FOPLP 封装量产和工艺升级过程中的主要难点。在其他条件固定时,FOPLP 的面积越大,则翘曲幅度越大。所选用的封装结构、塑封工艺、温度载荷的不同,都可能对 FOPLP 的翘曲产生影响。

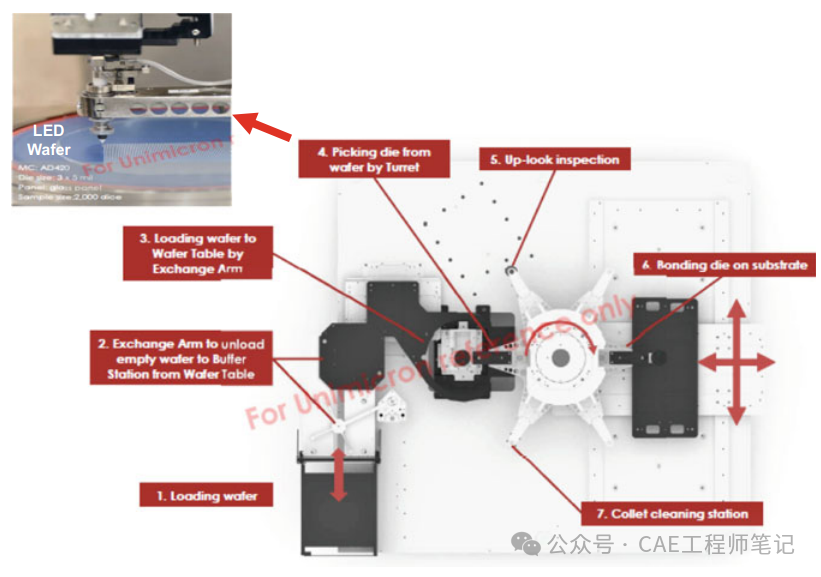

芯片偏移:在芯片拾取和放置过程中芯片定位精度的不足、在 EMC 压缩成型过程中芯片受到液体流动带来的拖动力和材料之间热膨胀系数不匹配导致的热失配应力均是造成芯片偏移的主要原因。轻微的芯片偏移会使后续光刻步骤中对准工艺产生明显的偏差,对 RDL 的制造是一个巨大的挑战。RDL 的线宽和线距以及器件焊盘之间的间距均会因芯片偏移而降低要求,导致封装尺寸和产能损失也有所增大。

界面分层:工艺过程中使用了较多的聚合物,这些聚合物在常温或常压下易吸收空气中的水分,在经过回流焊(220~260 °C)时,聚合物中的水分在高温下会瞬间气化,使聚合物内产生较大的蒸汽压,同时受到热失配应力的影响,重构晶圆内不同的粘接界面易发生裂纹萌生和分层现象。

芯片挤出:芯片挤出是指模塑料表面到芯片 I/O 面具有一定的台阶高度。在 RDL 制造中光刻工艺的精细间距和宽度的严格要求面临着共面性问题,芯片突出问题将极大地影响 RDL 的断裂,短路和开路故障。

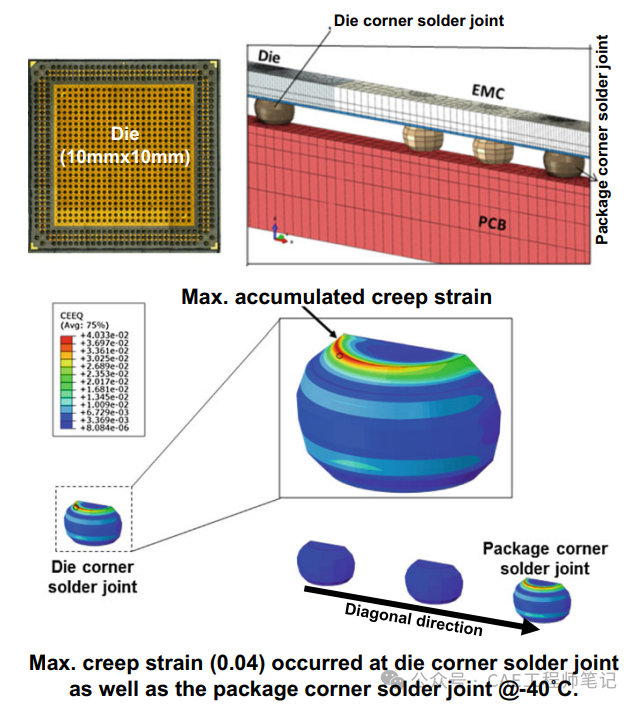

焊点疲劳失效:焊点的疲劳失效主要包括热疲劳和力学疲劳,其中热疲劳是导致焊点失效的主要因素,热疲劳源于器件在服役过程中承受的热循环载荷和功率载荷等。 宏观上表现为热疲劳损伤导致在远离焊点中心区的钎料与基板过度区(即高压力区)产生初始裂纹,裂纹逐渐沿钎料与基板界面扩展至整个焊点;微观上表现为热疲劳断口表面有疲劳条纹的特征、晶界微孔洞和蠕变沿晶界断裂的痕迹。焊点的疲劳寿命决定着整个器件的使用寿命,一个焊点的失效便可导致整个器件无法正常工作。

总的来说,从 2009 年 FOWLP 这一概念被提出以来,到现在随着尺寸超过 600×600 mm 的 FOPLP 的不断涌现。可以看出,要实现更高的制造效率,降低晶圆的浪费程度,同时维护好封装成本,FOWLP 朝着 FOPLP 的转变是必然的趋势。

-

晶圆

+关注

关注

53文章

5449浏览量

132749 -

封装

+关注

关注

128文章

9329浏览量

149039 -

先进封装

+关注

关注

2文章

562浏览量

1062

原文标题:先进封装技术(Semiconductor Advanced Packaging) - 7 扇出型板级封装(FOPLP)

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高速逻辑之HMC850LC3:1:2扇出缓冲器的卓越表现

高速利器——HMC724LC3 1:2扇出缓冲器深度解析

3.3V低噪声1:9扇出缓冲器ADH987S的设计与应用

深入解析SN65EL11:5V PECL/ECL 1:2扇出缓冲器

化圆为方,台积电整合推出最先进CoPoS半导体封装

基于板级封装的异构集成详解

先进封装技术-7扇出型板级封装(FOPLP)

先进封装技术-7扇出型板级封装(FOPLP)

评论