本文由半导体产业纵横(ID:ICVIEWS)综合

AI的激增推动了对先进半导体芯片的需求,推动了芯片设计和制造的界限。AI 的快速发展迎来了半导体比以往任何时候都更加重要的时代。从训练到部署,每个 AI 模型和应用程序的背后都隐藏着一个复杂的半导体网络,这些网络使处理大量数据所需的处理能力成为可能。AI 的激增推动了对先进半导体芯片的需求,推动了芯片设计和制造的界限。为了满足这些需求,半导体行业越来越多地转向 3D 异构集成等创新解决方案。

打破冯·诺依曼瓶颈

传统上,半导体行业遵循摩尔定律,该定律预测微芯片上的晶体管数量大约每两年翻一番。几十年来,这种对提高计算能力的不懈追求推动了晶体管的小型化。

然而,随着我们接近缩小晶体管的物理极限,该行业面临着新的挑战,尤其是在优化芯片架构以管理生成式 AI 不断增长的数据需求方面。现代芯片设计中最重要的挑战之一是“内存墙”或“冯·诺依曼瓶颈”,即数据在芯片内的内存和逻辑单元之间传输的速度受到限制。随着 AI 模型复杂性的增加和数据集的扩展,这种瓶颈变得更加明显,导致数据移动效率低下,从而阻碍整体性能。

为了克服这一瓶颈,半导体行业采用了 3D 异构集成,该技术涉及垂直堆叠内存和逻辑单元,而不是并排放置。这种垂直集成缩短了数据路径,提高了能源效率,并允许更高的互连密度——这是实现 AI 应用所需的高带宽的关键因素。通过采用这种方法,该行业可以绕过一些传统上限制芯片性能的物理限制。

摩尔定律规范着该行业

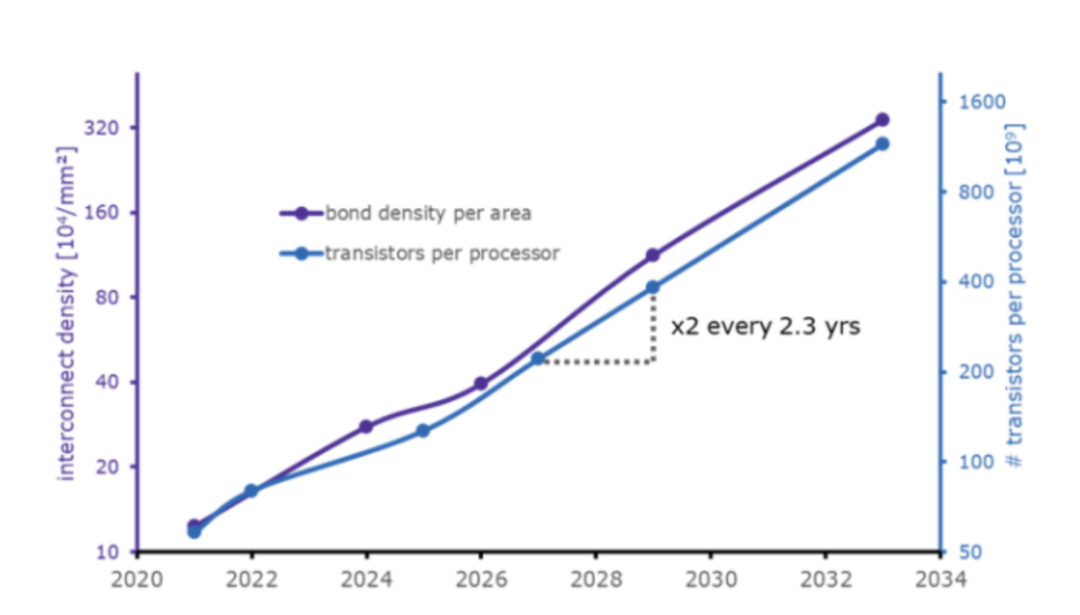

如图 1 所示,上述趋势不仅可以从经验上观察到,还可以从数量上反映出来。

图 1:摩尔定律支配着整个行业。紫色:增加互联密度以保持带宽。蓝色:晶体管数量增加,以提高逻辑能力。(数据和预测来自台积电)

每个处理器的晶体管数量每 2.3 年翻一番,符合经典的摩尔定律。有趣的是,另一个几乎以相同速度增长的指标:互连密度。摩尔定律可以追溯到 20 世纪 70 年代,而后者则是芯片带宽需求不断增长所带来的最新趋势——这也是人工智能面临的最严峻挑战之一。

尽管两者是不同的衡量标准,但当芯片性能进一步提高时,两者不可避免地会相互联系。要想取得成功,必须在这两个阶段(即前端和后端,因为尖端技术的进步依赖于其中任何一个阶段)都有所作为。

随着芯片向 3D 架构发展,这些互连线的密度变得与晶体管数量同等重要。更高的互连密度可以加快数据传输,这对人工智能加速器和系统级封装(SiP)解决方案至关重要。然而,要在不影响能效的前提下增加互连数量,就必须采用先进的材料和精密制造技术——在这些领域,计量学发挥着举足轻重的作用。

在晶圆厂内,一个晶圆需要经过数月的数百个步骤才能转化为高端芯片,而每个步骤都需要原子级的制造精度。瑕疵并非不存在。因此,良品率是衡量晶圆缺陷数量和程度的重要标准。高端芯片几乎不能容忍任何缺陷,而同样结构的芯片,如果缺陷率增加,则可能用于较低等级的应用。

显然,制造商的目标是最大限度地提高产量,因为在最终质量检查(也称为计量)确定芯片能力之前,运营成本已经累积。

计量在人工智能芯片制造中的关键作用

随着半导体芯片变得越来越复杂,计量学的作用也变得越来越关键。计量学涉及芯片特征的精确测量和检测,对于确保先进半导体器件的质量和功能至关重要。在三维异质集成的背景下尤其如此,传统的二维测量技术已不再足够。

新的计量工具旨在以纳米级精度高速测量复杂的三维结构。这些工具对于检测缺陷、监控关键尺寸和验证半导体器件所用材料的完整性至关重要。例如,在生产人工智能应用不可或缺的 HBM 单元时,多个 DRAM 单元的垂直整合需要原子级的精度。必须在每个芯片上钻出通道,以最高精度连接各层,因此计量是制造过程中的关键步骤。

人工智能创新的关键技术集成

半导体公司正在不断发展计量和检测仪器技术,这些技术对于确保半导体芯片的质量和产量至关重要,尤其是在三维异质集成等先进工艺中。

鉴于行业正向更复杂的芯片架构转变,计量工具显得尤为重要。随着芯片的垂直集成度越来越高,计量工具的精度和速度对于识别和纠正缺陷变得越来越重要,否则可能会影响整个芯片的性能。

人工智能芯片制造的未来

随着对人工智能和其他先进计算技术的需求不断增长,对能够提供更高性能、更高效率和前所未有的集成度的半导体芯片的需求也在不断增长。三维异构集成与先进计量技术的结合为满足这些需求提供了一条途径,使芯片的生产速度更快、体积更小、能效更高。

在这方面,Unity-SC 的三维光学计量解决方案在互连检测和大批量制造计量方面的专业知识,从而支持以高速大批量提高产量。

随着芯片架构变得越来越复杂,功能越来越小,互连越来越错综复杂,精确的测量和检测对于确保质量和功能至关重要。这些能力对于保持高产量和实现人工智能、AR/VR 等先进技术的性能要求至关重要。

-

3D

+关注

关注

9文章

3023浏览量

115577 -

AI

+关注

关注

91文章

41156浏览量

302620 -

半导体芯片

+关注

关注

61文章

946浏览量

72813

发布评论请先 登录

3D打印又火了!全球最大工厂将落地深圳

GRM2030:高集成3D Buck PowerSoC的卓越性能与应用

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进封装重塑热管理

西门子EDA重塑3D IC设计:突破高效协同、可靠验证、散热及应力管理多重门

【海翔科技】玻璃晶圆 TTV 厚度对 3D 集成封装可靠性的影响评估

iTOF技术,多样化的3D视觉应用

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

3D异构集成重塑芯片格局

3D异构集成重塑芯片格局

评论