随着摩尔定律逐渐接近物理极限,传统的二维集成电路技术在性能提升和芯片密度方面遇到了瓶颈。为了满足日益增长的高性能计算、人工智能等应用需求,3D IC技术应运而生,通过将多个芯片和器件在垂直方向上进行堆叠,极大地提高了芯片的集成度和性能,成为未来集成电路产业的重要发展方向。然而,3D IC在设计过程中也面临着诸多技术挑战。

高效协同平台,重塑异构复杂设计范式

3D IC的设计复杂度远超传统平面IC,其核心在于需要将不同功能、不同工艺的芯片集成在一起,形成一个高性能的系统。这种复杂的设计过程通常涉及多个工程团队的分布式设计,而缺乏统一的设计管理环境使得跨系统连接规划和协调变得极为困难。与此同时,3D IC的设计规模不断扩大,目前业界领先的3D IC已有多达百万个管脚,这对设计工具的性能和效率提出了极高的要求。

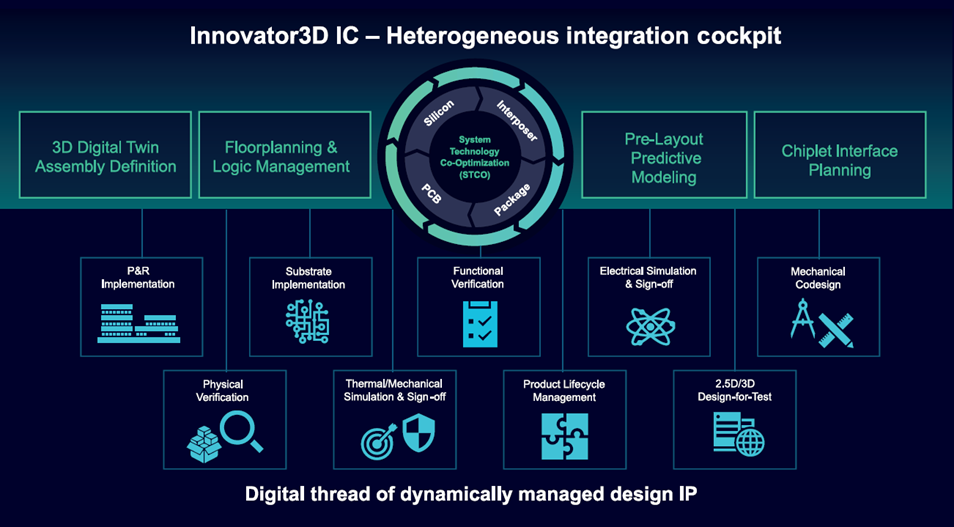

2024年,西门子EDA推出Innovator3D IC解决方案,助力IC设计师高效创建、仿真和管理异构集成的2.5D/3D IC设计。设计团队能够高效管理3D IC系统数据并实现有效关联,不仅可以一键导出文件至仿真与验证工具,快速执行评估,而且清晰的数据传递能够助力设计团队精准预测和规避下游问题。

2025年6月,Innovator3D IC套件发布,具备强大的多线程与多核处理能力,可为500多万管脚的设计提供优化的性能。其中,Innovator3D IC Integrator,可通过统一数据模型构建数字孪生的整合集成环境,以用于设计规划、原型验证及预测分析;Innovator3D IC Layout解决方案,可用于“设计即正确”封装中介层与基底实现;Innovator3D IC Protocol Analyzer,可用于芯粒间及裸片间接口合规性分析;Innovator3D IC Data Management,可以解决设计的复杂性、协作性和可靠性,以及设计数据IP的在研管理。

Innovator3D IC还支持通过LEF/DEF进行层次化器件规划,可在短短几分钟内构建拥有百万个引脚的Chiplet(小芯片),并提供高效的ECO(工程变更指令)流程。它能够在层次化数据模型之上,将芯片/小芯片、中介层、封装基板乃至系统PCB建模为多层级的器件层次结构,即使在涉及超过五千万个引脚的设计组装中,也能展现出卓越的可扩展性、容量和性能。

此外,西门子EDA的物理设计工具xPD及Aprisa进一步提供了创新的设计自动化、验证、优化和良率增强技术,确保客户的Layout设计满足所有性能、制造和可靠性要求。这些工具的强大设计性能专为复杂设计而生,目前已支持总引脚超过200万管脚的复杂设计。与此同时,xPD也支持多用户异地实时协同设计,极大地提高了团队协作效率并缩短了设计周期。

堆叠验证全覆盖,筑牢3D IC可靠性

3D IC系统由多颗芯片堆叠而成,验证这些芯片在堆叠后是否正确连接,这不仅涉及芯片间的DRC(设计规则检查)和LVS(电路与版图对比验证),尤其当芯片采用不同制造工艺时,如何实现自动且高效的准确验证,成为一个亟待解决的难题。此外,芯片堆叠连接后,整个ESD(静电放电)网络和路径可能会发生本质变化,如何验证新ESD网络和路径的可靠性变得更为复杂。

西门子EDA针对这些验证挑战,扩展了其Calibre平台。Calibre 3DStack工具能够自动化检查die引脚版图是否对准以及3D IC的LVS,确保芯片间的连接正确无误。同时,Calibre 3DPERC和mPower工具可以验证die堆叠之后的可靠性问题,例如ESD、EMIR等。

伴随着复杂的3D IC设计系统,同时也带来了更多的系统性能问题,如信号完整性、电源完整性等。西门子EDA提供组合Calibre xACT和HyperLynx SI,以及mPower和HyperLynx PI,可以对芯片、系统和PCB建模,并能够进行结合的仿真分析,保证整个3D IC系统的仿真结果和精度。此方案还可以嵌入到设计流程中进行快速仿真,提升仿真收益。

前瞻性分析,解决散热和应力难题

在3D堆叠结构中,每颗芯片工作时产生的热量难以有效散发,热量的堆积会导致晶体管结温和金属互联线温度的升高,从而影响芯片的性能,甚至损坏芯片。如何仿真3D IC的散热情况,并将温度分布反馈到每个芯片的器件来验证对性能的影响,是芯片设计工程师不得不面对的问题。

西门子EDA推出的Calibre 3DThermal软件,可针对3D IC中的热效应进行分析、验证与调试。该工具可以让芯片设计人员能够从芯片和封装设计的早期内部探索到signoff阶段,对热效应进行快速建模和可视化呈现。它能够帮助用户分析芯片堆叠之后的散热效果以及每个芯片上单元级别的热分布状况,从而仿真分析散热对每个芯片的性能的影响,进而优化芯片的布局布线或封装设计,有效解决散热问题。

此外,随着2.5D/3D IC架构的裸片厚度降低及封装工艺温度升高,高温会给芯片带来新的应力,从而导致器件的电学性能发生偏移,如何预估这种应力对芯片电学性能的影响也是一个难题。

Calibre 3DStress正是针对这一挑战而推出,支持在3D IC封装场景下对热-机械应力及翘曲进行晶体管级精确分析、验证与调试,使芯片设计师能够在开发早期评估芯片封装交互作用对设计功能的影响。这种前瞻性分析不仅可预防后期失效,提升设计效率、良率及可靠性,还能优化设计以提升性能与耐用性。

3D IC技术作为未来集成电路重要的发展方向,具有广阔的应用前景。西门子EDA凭借创新的、丰富的工具链,为3D IC的设计协同、堆叠验证、散热和应力等问题提供了全面的解决方案,助力行业突破技术瓶颈。未来,随着工艺进步和市场需求的推动,3D IC有望在更多领域实现突破,而西门子EDA将继续引领技术创新,为3D IC的可持续发展注入强大动力。

-

西门子

+关注

关注

98文章

3374浏览量

120707 -

eda

+关注

关注

72文章

3143浏览量

183756 -

Layout

+关注

关注

15文章

424浏览量

75427 -

3DIC

+关注

关注

3文章

92浏览量

20167 -

3D堆叠封装

+关注

关注

0文章

18浏览量

7604

原文标题:重塑3D IC设计: 突破高效协同、可靠验证、散热及应力管理多重门

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

西门子与NVIDIA实现验证领域关键突破

西门子EDA亮相2026玄铁RISC-V生态大会

西门子EDA亮相Semicon China 2026

西门子Questa One验证解决方案引入智能体AI功能

西门子EDA与Arm携手合作加速系统设计验证进程与软件启动

西门子V90伺服,为3D打印企业降本增效“加足马力”

强强合作 西门子与日月光合作开发 VIPack 先进封装平台工作流程

2025西门子EDA技术峰会圆满落幕

西门子EDA与北京开源芯片研究院达成战略合作

AI 时代,西门子 EDA 走出这三步棋

西门子EDA重塑3D IC设计:突破高效协同、可靠验证、散热及应力管理多重门

西门子EDA重塑3D IC设计:突破高效协同、可靠验证、散热及应力管理多重门

评论