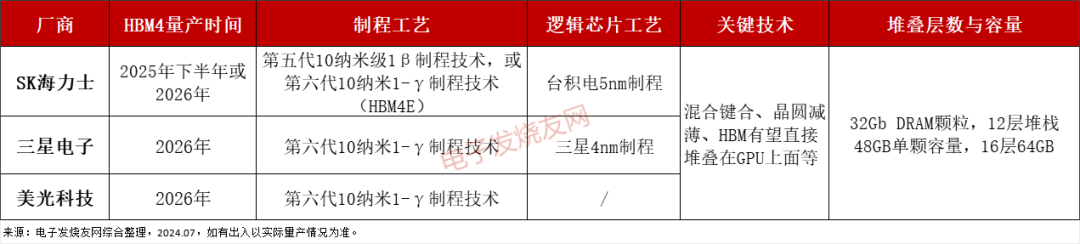

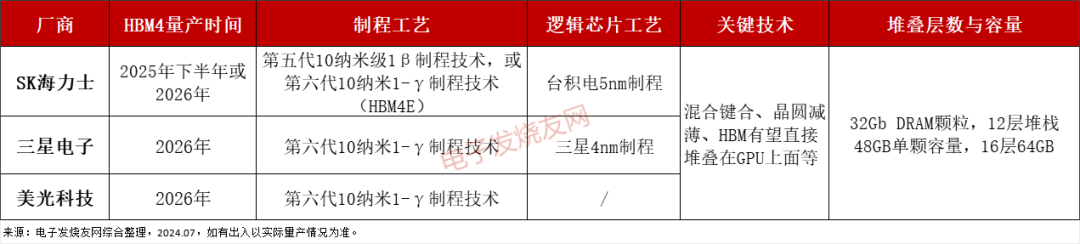

电子发烧友网报道(文/黄晶晶)眼下各家存储芯片厂商的HBM3E陆续量产,HBM4正在紧锣密鼓地研发,从规格标准到工艺制程、封装技术等都有所进展,原本SK海力士计划2026年量产HBM4,不过最近有消息说提前到2025年。其他两家三星电子和美光科技的HBM4的量产时间在2026年。英伟达、AMD等处理器大厂都规划了HBM4与自家GPU结合的产品,HBM4将成为未来AI、HPC、数据中心等高性能应用至关重要的芯片。

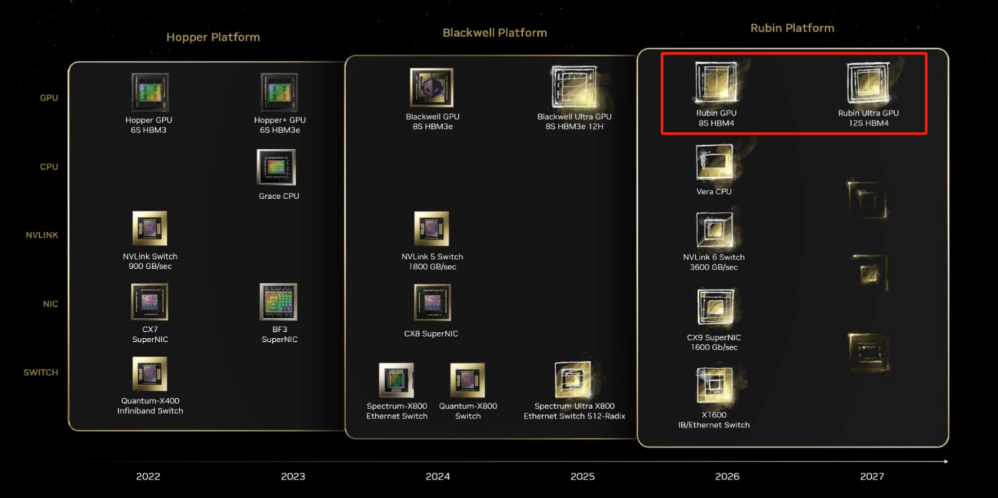

结合正在制定的行业标准以及厂商信息,我们大致可以看到HBM4的一些特性。首先HBM4的接口将采用2048位,比HBM3E的1024位高出一倍。HBM4的带宽在2TB/s或以上,HBM3E的带宽最高可达1.2TB/s。另外,SK海力士技术人员Kim Kwi Wook表示,HBM4E内存可较HBM4在带宽上提升40%、密度提升30%,同时能效也提高30%。堆叠层数和容量上,HBM4采用32Gb DRAM颗粒,12层堆叠达到48GB容量,高至16层可达到64GB,HBM3E采用24Gb DRAM颗粒,8层堆叠为24GB容量,最高12层,36GB容量。今年6月,NVIDIA 宣布下一代Rubin GPU将配备8个HBM4,Rubin Ultra GPU将配备12个HBM4芯片,其总内存容量将显著提升。

结合正在制定的行业标准以及厂商信息,我们大致可以看到HBM4的一些特性。首先HBM4的接口将采用2048位,比HBM3E的1024位高出一倍。HBM4的带宽在2TB/s或以上,HBM3E的带宽最高可达1.2TB/s。另外,SK海力士技术人员Kim Kwi Wook表示,HBM4E内存可较HBM4在带宽上提升40%、密度提升30%,同时能效也提高30%。堆叠层数和容量上,HBM4采用32Gb DRAM颗粒,12层堆叠达到48GB容量,高至16层可达到64GB,HBM3E采用24Gb DRAM颗粒,8层堆叠为24GB容量,最高12层,36GB容量。今年6月,NVIDIA 宣布下一代Rubin GPU将配备8个HBM4,Rubin Ultra GPU将配备12个HBM4芯片,其总内存容量将显著提升。

行业标准制定中

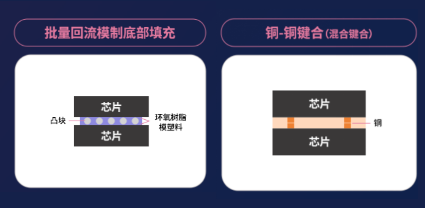

近日,JEDEC固态技术协会发布的新闻稿表示,HBM4标准即将定稿,进一步提高数据处理速率,具有更高带宽、更低功耗以及增加裸晶/堆栈的容量。这些进步对于需要高效处理大型数据集和复杂计算的应用至关重要,包括生成式人工智能(AI)、高性能计算、高端显卡和服务器。 与HBM3相比,HBM4在每个堆栈中引入了两倍的通道计数,具有更大的物理尺寸。为了支持设备兼容性,标准确保单个控制器可以同时处理HBM3和 HBM4。HBM4将指定24 Gb和32 Gb层,并提供支持4层、8层、12层和16层TSV堆栈的选项。该委员会初步同意最高6.4 Gbps的速度,并正在讨论更高频率的问题。 另外,韩媒报道还指出,JEDEC有望放宽对HBM4内存的高度限制。目前,HBM内存的最大DRAM堆叠层数为12层,允许的最大厚度为720微米。三星最近HBM3E 12H产品通过对NCF材料的优化,芯片之间的间隙已降低至7微米。若HBM4内存提升到16层,再加上凸块厚度,传统技术无法实现在720微米厚度下的16层堆叠。于是,据称JEDEC主要参与方已同意放宽HBM4高度限制至775微米。这样也可以为混合键合HBM内存的商业化留出更多时间。 下图左边为SK海力士从HBM3开始采用的先进大规模回流成型底部填充 (MR-MUF) 工艺,右边为Cu-to-Cu(Copper-to-Copper, 铜-铜)键合封装工艺,是一种混合键合方法,可在完全不使用凸块的情况下将间距缩小至10微米及以下。混合键合技术可以进一步缩小间距,同时作为一种无间隙键合(Gapless Bonding)技术,在芯片堆叠时不使用焊接凸块(Solder Bump),因此在封装高度上更具优势,是目前各家存储芯片厂商重点开发的技术。

图源:SK海力士

HBM4制程工艺与性能

HBM的制程工艺方面,SK海力士在HBM3E内存上使用第五代10纳米级1β制程技术,在2024年度IEEE IMW国际存储研讨会上,SK海力士表示计划使用第六代10纳米级的1-γ制程技术的32Gb DRAM裸片构建HBM4E内存。至于HBM4内存,分析认为由于SK海力士将在2025年量产HBM4,比其他两家要早,那时可能还是采用的第五代10纳米级1β制程技术。另外,三星电子、美光科技也纷纷将使用第六代10纳米级的1-γ制程技术用于HBM4内存。

图源:英伟达 (注:右上角红框为配备8个HBM4的Rubin GPU,以及配备12个HBM4芯片的Rubin Ultra GPU)

逻辑芯片、3D堆叠封装工艺更新

三星电子最近介绍了HBM与定制逻辑芯片进行3D堆叠的方案,是将HBM直接安装在系统芯片上,可省去中间件和基板,大幅减少功耗和面积。SK海力士也在考虑HBM4直接堆叠在GPU上的方案。这是除HBM堆叠在GPU芯片旁这种较成熟的方案之外的另一个可能性。 对于逻辑芯片,它是DRAM 堆栈的控制单元,也负责通过互连层与处理器上的内存接口通信,也是 HBM 内存的重要组成部分。由于HBM4的逻辑芯片需要支持更多的信号引脚、更大的数据带宽和承载部分客户定制功能,因此存储厂商开始选择与逻辑晶圆厂合作,用逻辑半导体工艺生产HBM4的逻辑芯片。 目前的消息显示三星将采用自家的4nm制程生产,该制程的良率已经超过70%。三星已经将晶圆代工部门员工派往HBM开发团队,通过内存部门和代工部门的紧密合作,从逻辑裸晶的设计阶段寻求优化,以最大限度地提高HBM4芯片的性能和功耗水平。 SK海力士则在今年4月与台积电签署谅解备忘录,合作生产HBM4。SK海力士表示,以往的HBM产品,包括HBM3E(第五代HBM产品)都是基于公司自身制程工艺制造了基础裸片(也就是逻辑芯片),但从HBM4产品开始计划采用台积电的先进逻辑(Logic)工艺。若在基础裸片采用超细微工艺可以增加更多的功能。由此,公司计划生产在性能和功效等方面更广的满足客户需求的定制化(Customized)HBM产品。 与此同时,双方将协力优化SK海力士的HBM产品和台积电的CoWoS技术融合,共同应对HBM相关客户的要求。 台积电在2024年的技术研讨会上展示了两款HBM4基础裸片,分别是N12FFC+和N5制程技术,其中N5版相较于N12FFC+版面积更小,性能更高,功耗更低,支持6~9μm级别的互联间距,并能实现与逻辑处理器的3D垂直集成,有望大幅提升HPC和AI芯片的内存带宽。那么SK海力士HBM4的逻辑芯片极有可能采用台积电的5nm制程工艺。 同时,韩媒消息称,SK海力士已向全球第二大封测厂Amkor协商供应硅中介层样品。SK海力士将自己生产的HBM和硅中介层等发送给Amkor,由Amko将把它们与英伟达等客户的GPU组装成AI加速器。 混合键合仍面临良率不佳的问题,因此SK海力士技术人员Kim Kwi Wook表示HBM4产品中采用混合键合的可能性不大。不过,为了降低晶圆堆叠的厚度,毕竟现在HBM芯片标准厚度为720um,如果要堆叠更多晶圆,晶圆减薄、铜-铜键合封装等都是关键技术。小结:

AI热度当前,英伟达、AMD等厂商对HBM的需求不减,HBM迭代频率在加快。随着行业标准的正式定稿,以及存储厂商HBM4新规格的发布,我们将进入HBM4的世代。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储

+关注

关注

13文章

4897浏览量

90294 -

HBM

+关注

关注

2文章

435浏览量

15885 -

HBM3E

+关注

关注

0文章

82浏览量

791

发布评论请先 登录

相关推荐

热点推荐

GPU猛兽袭来!HBM4、AI服务器彻底引爆!

电子发烧友网报道(文/黄晶晶)日前,多家服务器厂商表示因AI服务器需求高涨拉高业绩增长。随着AI服务器需求旺盛,以及英伟达GPU的更新换代,势必带动HBM供应商的积极产品推进。三星方面HBM3E

消息称英伟达HBM4订单两家七三分,独缺这一家

的相关产品。 三星电子HBM4 采用1c DRAM 和 4nm 制程工艺,其数据处理速度超过了JEDEC 标准的8Gbps,最高可达11.7Gbps,比上一代 HBM3E(9.6Gbp

HBM3E反常涨价20%,AI算力竞赛重塑存储芯片市场格局

明年HBM3E价格,涨幅接近20%。 此次涨价背后,是AI算力需求爆发与供应链瓶颈的共同作用。随着英伟达H200、谷歌TPU、 亚马逊Trainium 等AI芯片需求激增,HBM3E供需缺口持续扩大。与此同时,存储厂商正将产能转向更先进的

存储迭代暗涌:HBM4与UFS4.1浪潮下,烧录环节何以成为新瓶颈?

存储芯片市场扩产繁荣,HBM4、UFS4.1等先进技术加速量产,但被低估的烧录环节成关键瓶颈。先进存储对烧录的速度、精度和协议复杂度提出极高要求,面临三重技术关卡。需专用烧录方案突破瓶颈,其是国产存储跨越量产“最后一公里”的关键

美光确认HBM4将在2026年Q2量产

2025年9月24日,美光在2025财年第四季度财报电话会议中确认,第四代高带宽内存(HBM4)将于2026年第二季度量产出货,2026年下半年进入产能爬坡阶段。其送样客户的HBM4产

全球首款HBM4量产:2.5TB/s带宽超越JEDEC标准,AI存储迈入新纪元

电子发烧友网报道(文 / 吴子鹏)近日,SK 海力士宣布全球率先完成第六代高带宽存储器(HBM4)的开发,并同步进入量产阶段,成为首家向英伟达等核心客户交付 HBM4 的存储厂商。

发表于 09-17 09:29

•6619次阅读

SK海力士宣布量产HBM4芯片,引领AI存储新变革

HBM4 的开发,并在全球首次构建了量产体系,这一消息犹如一颗重磅炸弹,在半导体行业乃至整个科技领域激起千层浪。 高带宽存储器(HBM)作为一种能够实现高速、宽带宽数据传输的下一代

传三星 HBM4 通过英伟达认证,量产在即

开始实现大规模生产。这一进展将使得三星参与到下一阶段HBM订单的有力竞争。 三星还在HBM3E上提供了非常具有吸引力的报价,传闻向英伟达提供比SK海力士低20%至30%的报价,三星不得不通过激进定价策略来提升市场竞争力。 近日消息,S

传英伟达自研HBM基础裸片

"后的下一代AI GPU "Feynman"。 有分析指出,英伟达此举或是将部分GPU功能集成到基础裸片中,旨在提高HBM和GPU的整体性能。英伟达会将UCIe接口集成到HBM4中,以实现GPU

英伟达认证推迟,但三星HBM3E有了新进展

明年。目前博通凭借自有半导体设计能力,正为谷歌代工第七代TPU"Ironwood"及Meta自研AI芯片"MTIA v3"。 此外,三星电子也积极推进向亚马逊云服务(AWS)供应HBM3E 12层产品,近期已在平泽园区启动实

今日看点丨英特尔计划裁减高达20%员工;超48亿!面板大厂重磅收购

1. 三星向博通供应HBM3E 芯片,重夺AI 芯片市场地位 据韩媒报道,三星电子将向博通供应第五代高带宽内存(HBM3E),继AMD之后再获大单。据业内消息人士透露,三星电子已完成博

发表于 06-18 10:50

•1770次阅读

美光12层堆叠36GB HBM4内存已向主要客户出货

随着数据中心对AI训练与推理工作负载需求的持续增长,高性能内存的重要性达到历史新高。Micron Technology Inc.(美光科技股份有限公司,纳斯达克股票代码:MU)宣布已向多家主要客户送样其12层堆叠36GB HBM4内存。

Cadence推出HBM4 12.8Gbps IP内存系统解决方案

需求。Cadence HBM4 解决方案符合 JEDEC 的内存规范 JESD270-4,与前一代 HBM3E IP 产品相比,内存带宽翻了一番。Cadence

HBM3E量产后,第六代HBM4要来了!

HBM3E量产后,第六代HBM4要来了!

评论