本文转载自: 硬件十万个为什么微信公众号

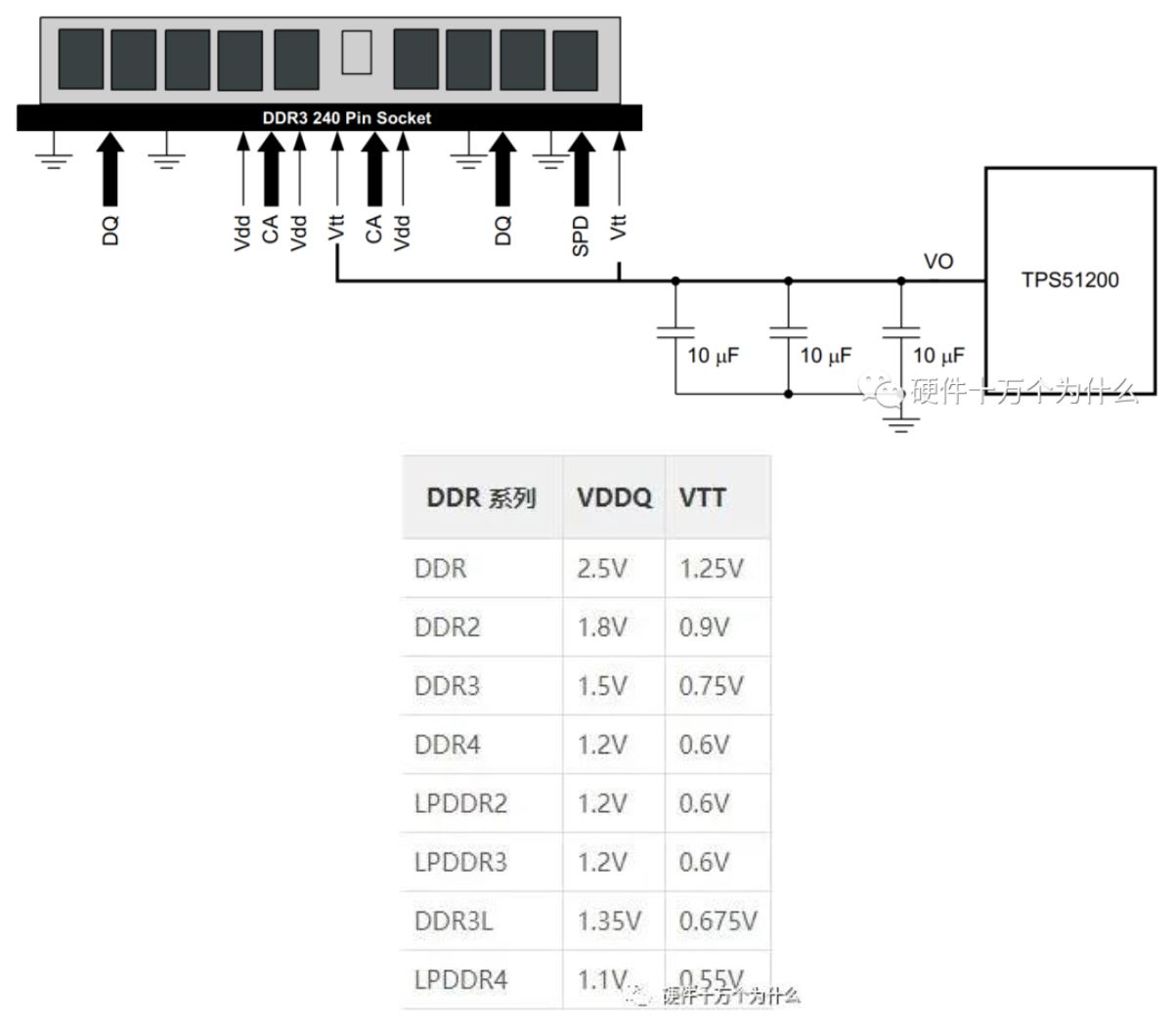

对于电源电压,DDR SDRAM系统要求三个电源,分别为VDDQ、VTT和VREF。

A、主电源VDD和VDDQ

主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给内核供电。但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有专门的VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压、电流是否满足要求。

电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

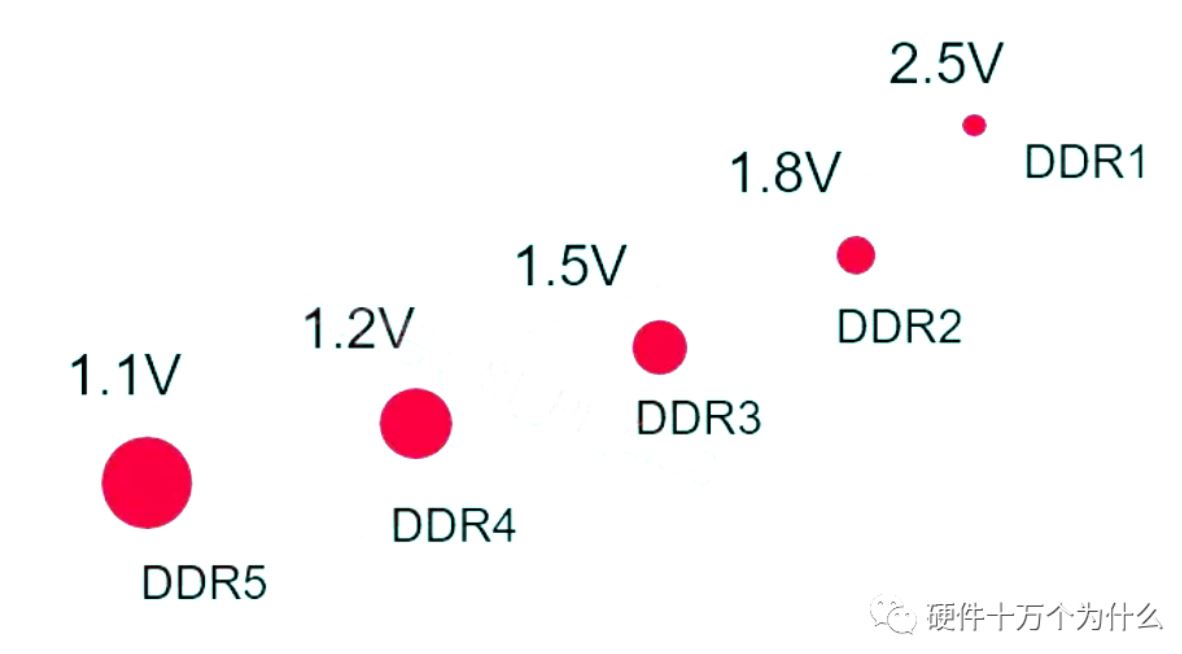

到了DDR5,电压将会从1.2V变到1.1V,下降了8.3%,这是几代DDR总线以来下降比例最少的一次。说明电子技术的发展,对于低功耗的设计难度越来越大。这么低的电压,其抗干扰设计就会更加的难。对于电源完整性和信号完整性的设计要求就越来越严苛。

B、参考电源Vref

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100Ω~10kΩ均可,需要使用1%精度的电阻。Vref参考电压的每个管脚上需要加10nF的电容滤波,并且每个分压电阻上也并联一个电容较好。

Vref此处的电流并不大,通过分压,可以选择阻值稍大的电阻。所以需要靠近芯片放置,放置走线过长,被其他大电流信号干扰。

C、用于匹配的电压VTT(Tracking Termination Voltage)

VDDQ是一种高电流电源DDR芯片的内核、I/O和存储器逻辑供电,而Vref是一种低电流、精确的参考电压,它在逻辑高电平(1)和逻辑低电平(0)之间提供一个阈值,以适应I/O电源电压的变化。通过提供一个适应电源电压的精确阈值,VREF实现了比固定阈值和终端和驱动正常变化情况下更大的噪声裕度。

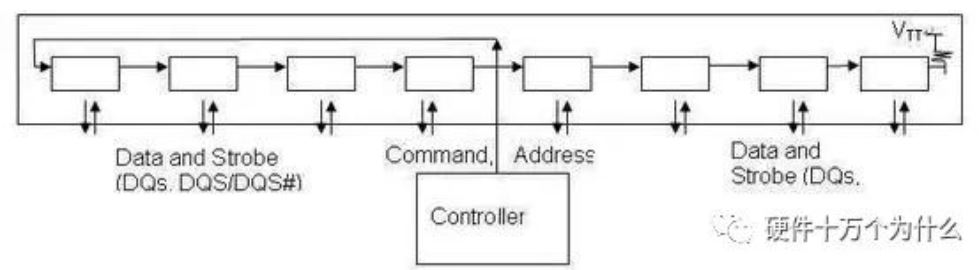

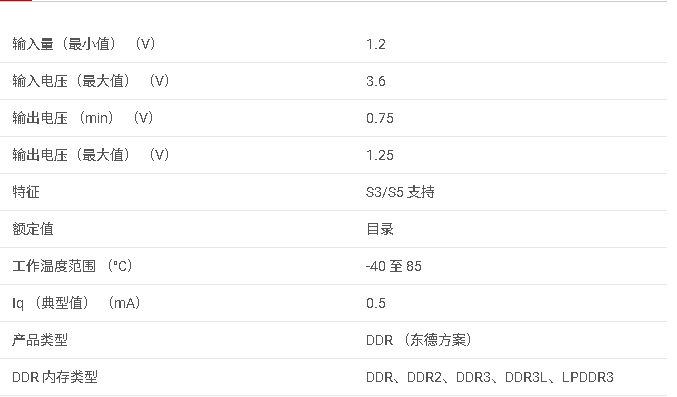

VTT的作用是改善信号质量,最常见的规格是0.49到0.51倍VDDQ,VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源既可以吸电流,又可以灌电流才可以。一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。很多情况下,也采用上下拉电阻实现吸电流和灌电流的功能,即戴维南电路。

而且,每个拉到VTT的电阻旁一般放一个10nF~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

由于VTT电源必须在 1/2 VDDQ提供和吸收电流,因此如果没有通过分流来允许电源吸收电流,那么就不能使用一个标准的开关电源。而且,由于连接到VTT的每条数据线都有较低的阻抗,因而电源就必须非常稳定。在这个电源中的任何噪声都会直接进入数据线。

VTT 被用来从DDR控制器IC中获取电压,给数据总线和地址总线提供电源,VTT不直接应用在DDR器件上,而是在系统电源上(VTT和终端电阻都被集成到 DDR CONTROLLER上),因此不需要在电路图中额外标出。它的值通常设定大致等于VREF的值(在VREF上下0.04V浮动),并且随着VREF的变 化而变化。对于DDR1 SDRAM应用中的地址总线控制信号和数据总线信号都有端接电阻。需要一个没有任何的噪声或者电压变化的参考电压(VREF),用作DDR SDRAM输入接收器,VREF也等于1/2 VDDQ。VREF的变化将会影响存储器的设置和保持时间。

2、为什么需要VTT

为了符合DDR的要求并保证最优的性能,VTT和VREF需要在电压、温度和噪声容限上进行严密的控制以便跟踪1/2 VDDQ。

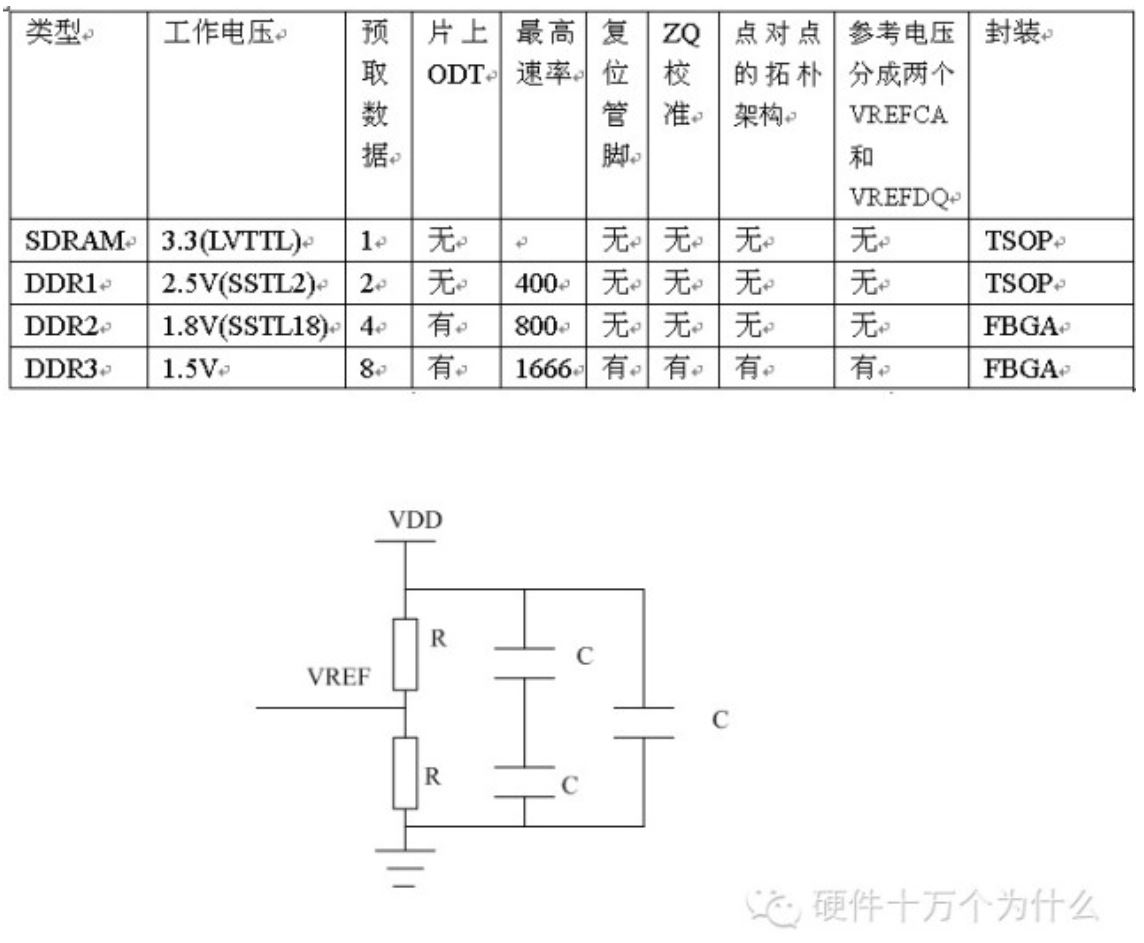

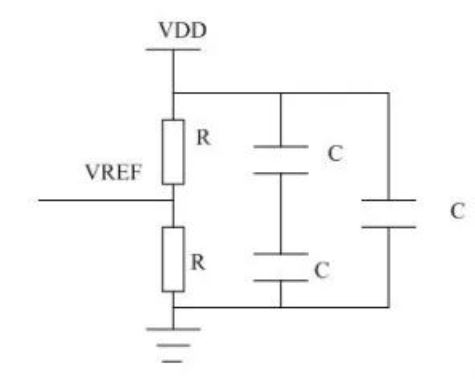

在实际电路中,对于VREF的电压采取电阻分压的方式取得,如下图所示:

其中电容为去耦电容。

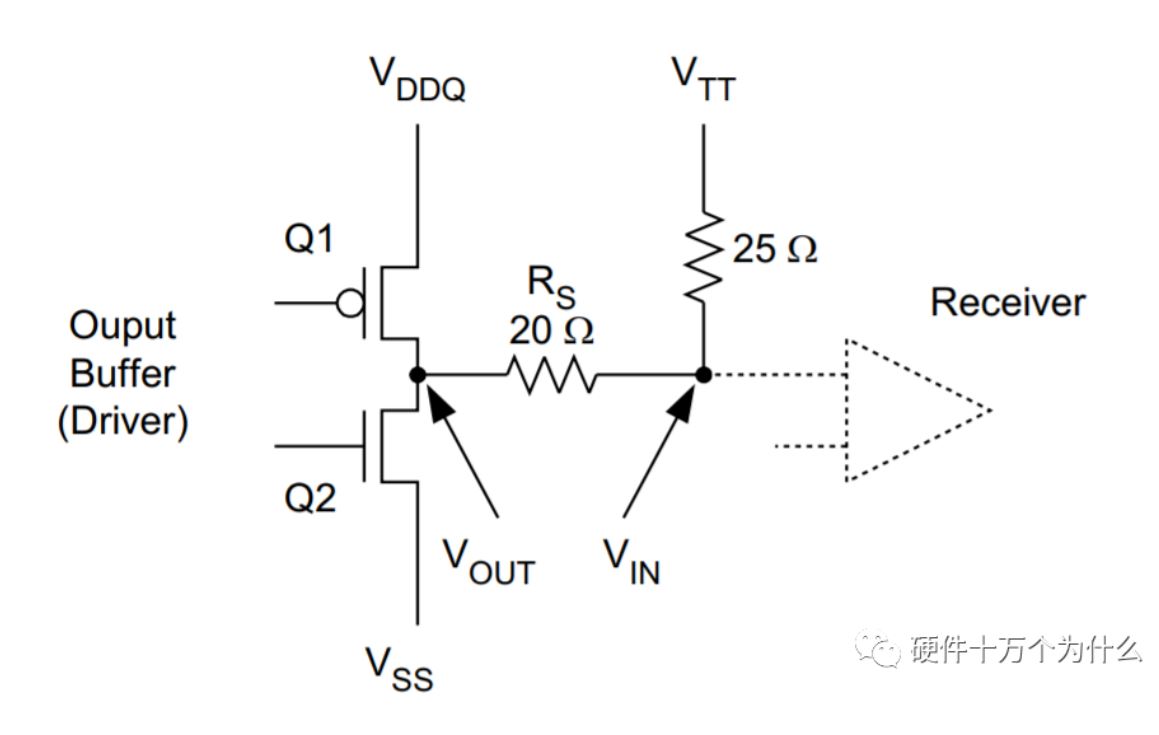

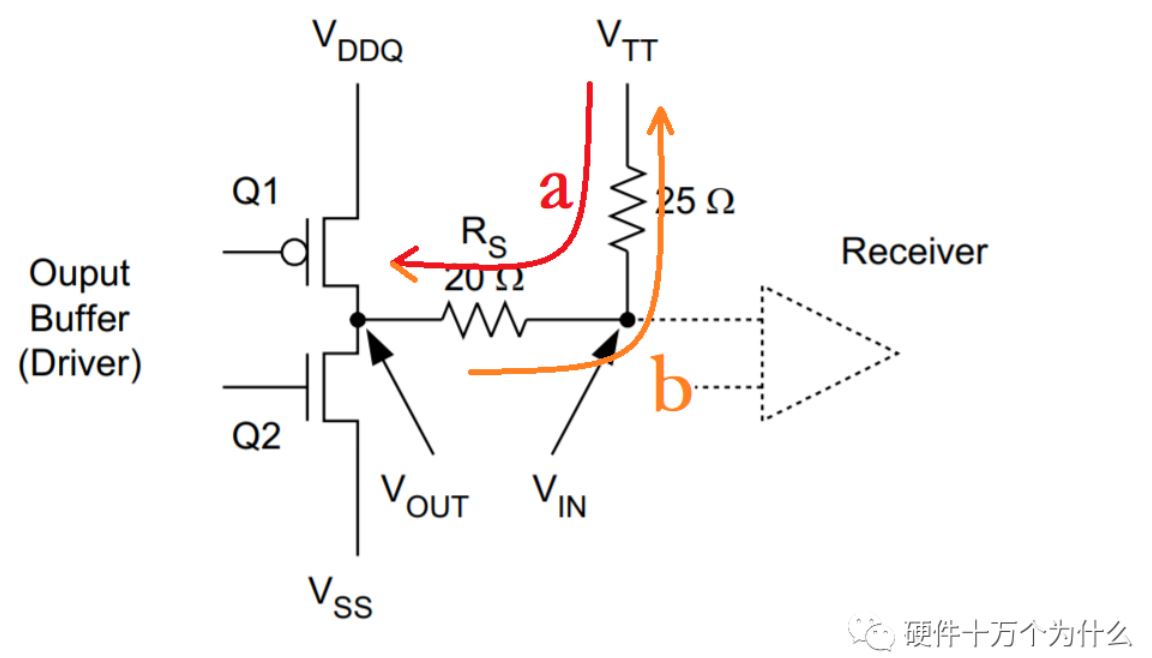

DDR颗粒的接收端比较特殊,它是一个差分放大器,其中的一个PIN脚连接Vref是固定,另一个PIN接在DDR控制器的发送端,发送端发送过来的信号,只要比Vref高,高过一定的门限,接受端就认为1,只要比Vref低,低于一定的门限,接收端就认为0。我们知道DDR的速率(电平的切换)是很快的,同时一个控制器会下挂很多颗粒,这就导致总线上的电流(电荷)来不及泄放和补充,这就需要将VTT在VOUT为高的时候,吸收电流,在VOUT为低的时候补充电流;

以DDR2为例,当VOUT为高电平的时候,VOUT=1V8,VTT=0V9,电流b向处于增加的趋势,当VOUT为0,VTT=0V9,电流a向处于增加趋势;

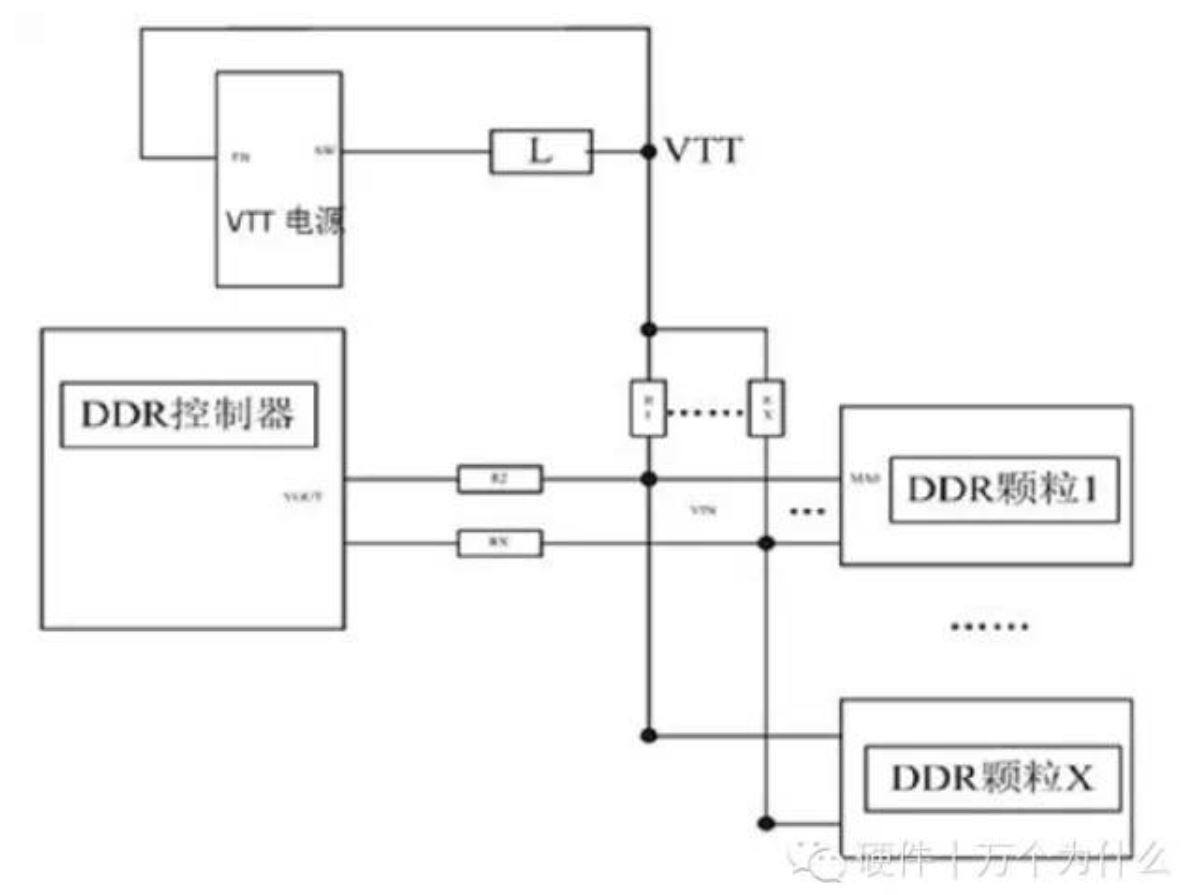

一般DDR VTT的拓扑结构

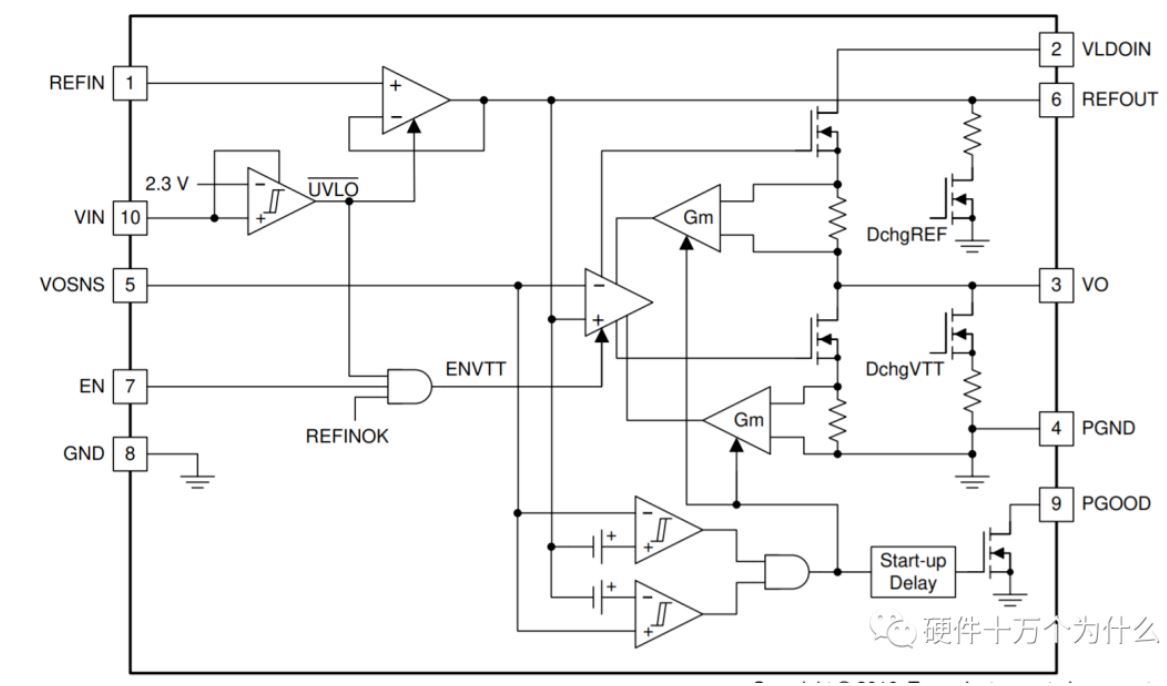

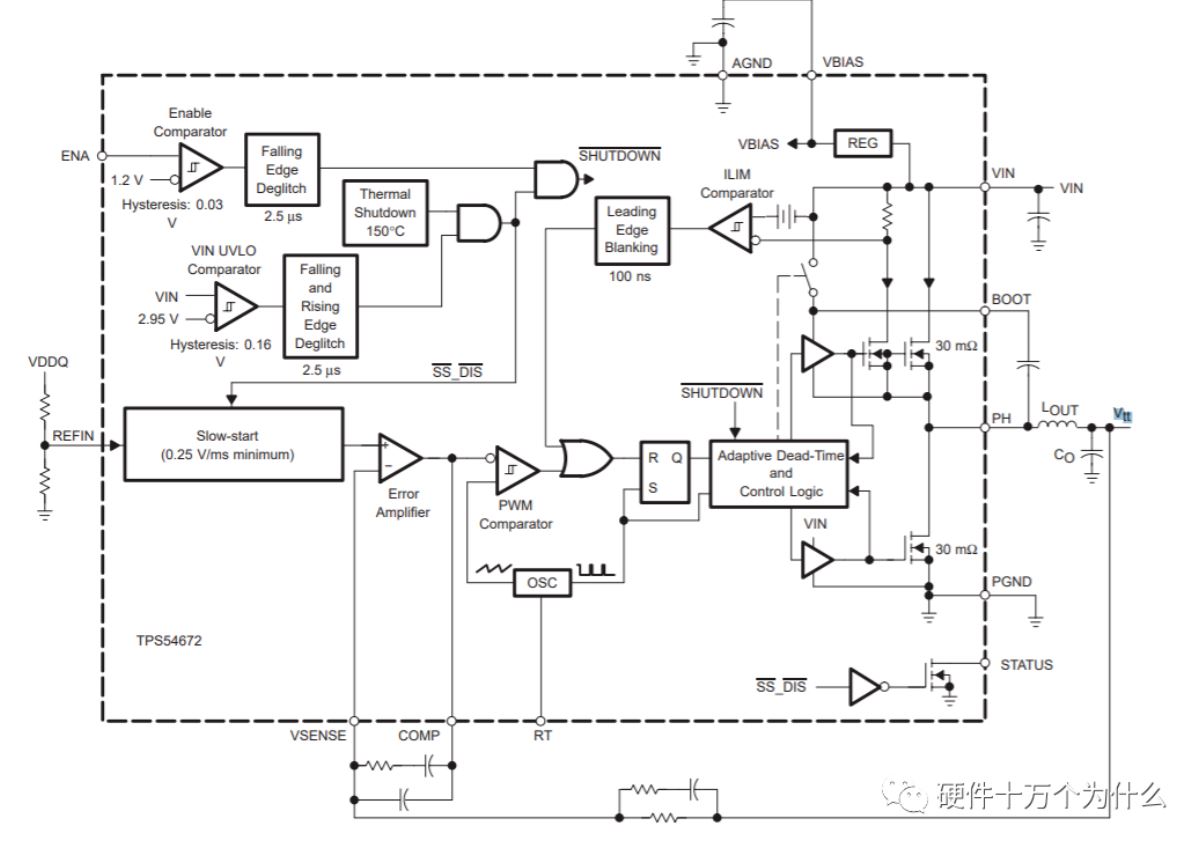

3、VTT电源工作原理

其中VFB为电压反馈端,SW为电压输出端;

结合DDR拓扑图来看,当VOUT为低的时候,由于a方向的电流处于增大的趋势,电感L会产生临时反向电动势,来抑制电流变化,这样导致VTT电压变小,上管导通,来补偿这个电流,直至流经电感的电流等于新的电流;

当VOUT为高的时候,由于b方向的电流处于增大的趋势,电感L会产生临时的反向电动势,来抑制电流变化,这样导致VTT处的电源变大,进而导致Vsense变大,上管关闭,下管导通,吸收电流;

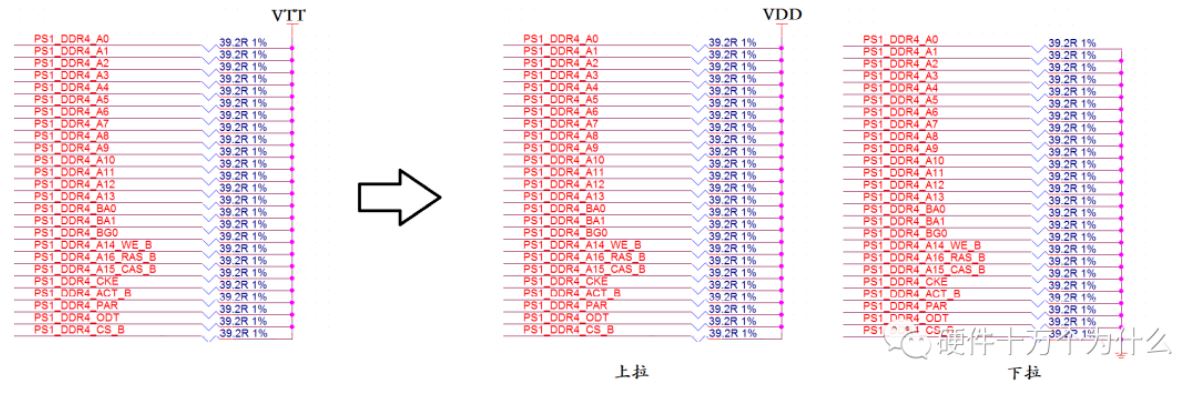

4、戴维南电路代替VTT

在一些设计中,在使用DDR颗粒的情况下,已经基本全部不使用VTT电源,全部采用电阻上下拉的戴维南电路(用上下拉电阻替代VTT电源),只有在使用内存条的情况下才使用VTT电源。需要进行信号完整性仿真之后,确定上下拉电阻的阻值。这个阻值一般比较小,虽然降低了设计复杂度,但是增大了整个系统的功耗。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。DDR2的地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T型的结构,所以常常需要使用VTT进行信号质量的匹配控制。DDR3可以采用Fly-by方式走线。

4、VTT电流预估

例如:VTT(0.6V)作为地址线/控制线(共25根)的上拉电源 ,上拉电阻39.2欧姆,最大电流计算公式:(0.6V/39.2)*25 = 0.38A。

最大电流就是所有信号同为高,或者同为低的时候,所有的信号线都是灌电流或者拉电流。如果有高有底,则会相互抵消,VTT的输出电流没有那么大。

审核编辑 黄宇

-

电源

+关注

关注

185文章

18985浏览量

264543 -

DDR

+关注

关注

11文章

761浏览量

69564

发布评论请先 登录

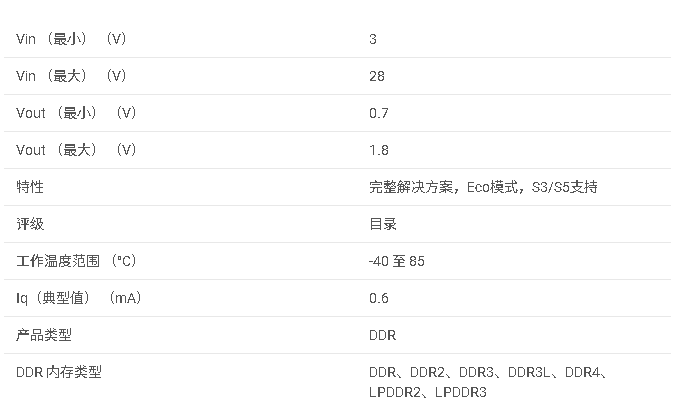

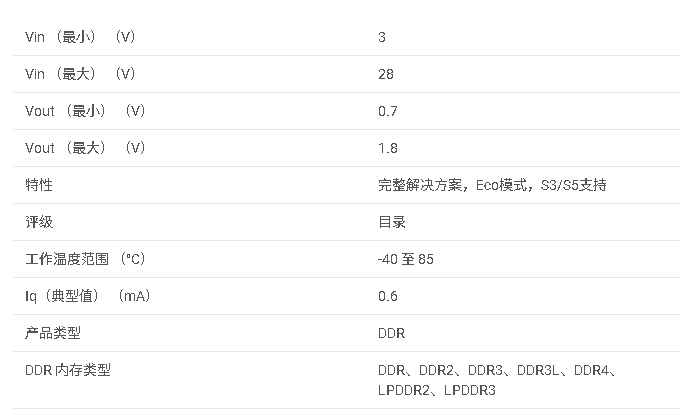

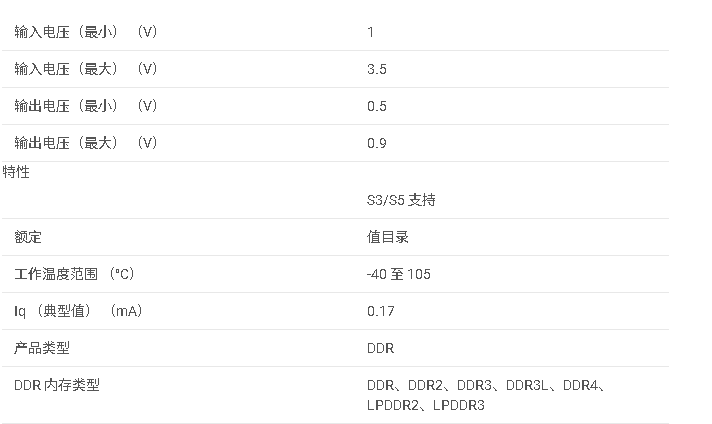

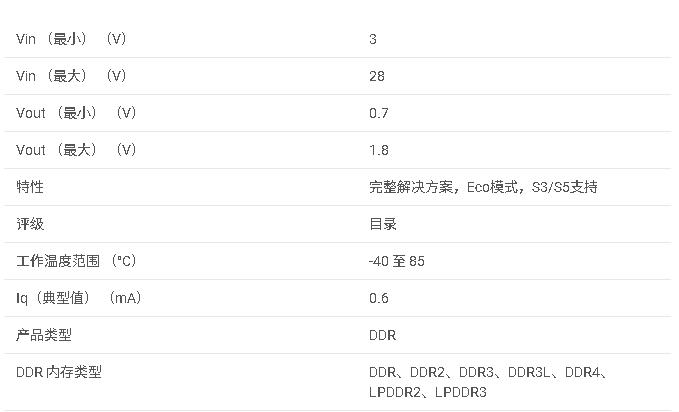

SATA/ DDR 接口的电源设计要点

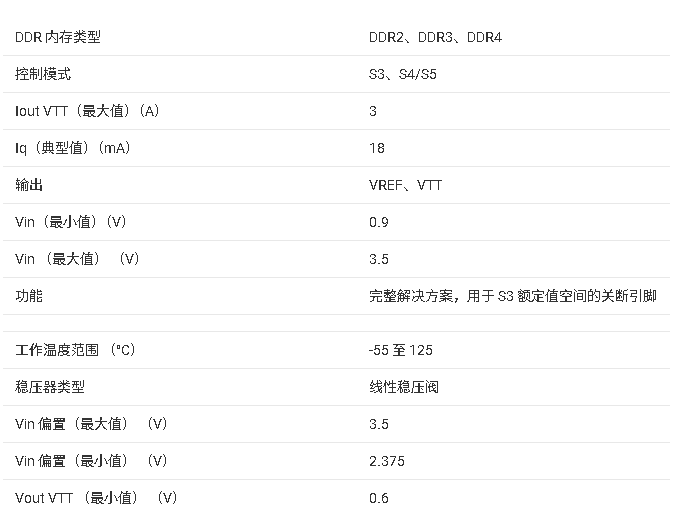

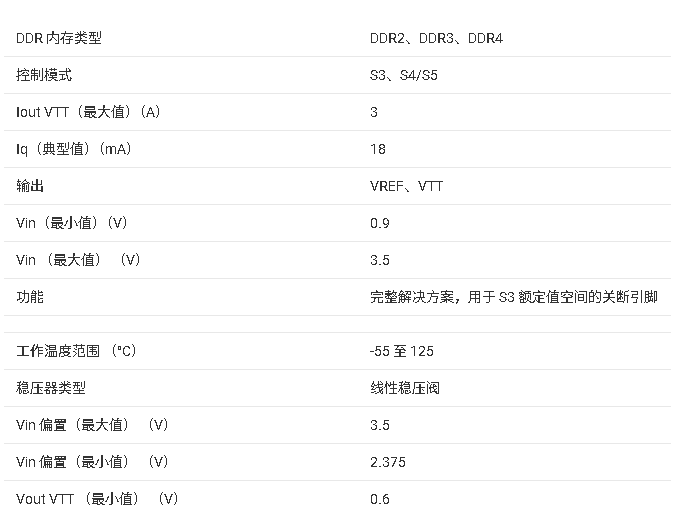

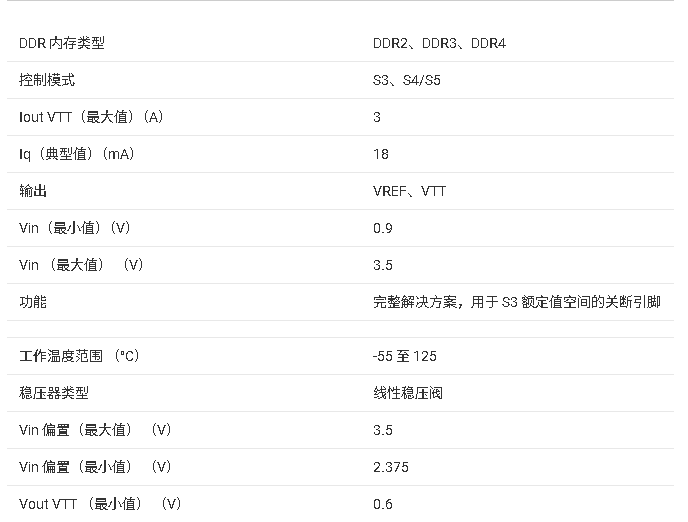

深入解析NCP5214:笔记本DDR电源控制的理想之选

MAX8550评估套件:DDR电源解决方案评估利器

MAX1917评估套件:DDR内存电源管理解决方案

MAX1917:DDR内存电源管理的理想选择

MAX17000:DDR2和DDR3内存电源管理解决方案的卓越之选

MAX17000A:DDR2和DDR3内存电源管理的理想之选

TPS51100 3A 拉/灌 DDR 端接稳压器数据手册

TPS51216 DDR2/3/3L/4 存储器电源解决方案同步降压控制器、2A LDO、缓冲基准数据手册

TPS51916 DDR2/3/3L/4 内存电源解决方案同步降压控制器数据手册

TPS51206 2A 峰值灌电流 / 拉电流 DDR 终端稳压器,带有 VTTREF 缓冲基准数据手册

TPS51716 完整的 DDR2/3/3L/4 存储器电源解决方案同步降压控制器数据手册

VTT电源对DDR有什么作用?

VTT电源对DDR有什么作用?

评论