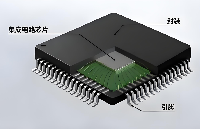

芯片合封是指将多个半导体芯片集成在一起,形成一个更大的芯片,以满足更高的功率、更高的效率和更高的可靠性等应用需求。芯片合封技术包括芯片堆叠、芯片封装等多种方式。

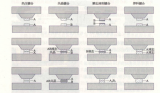

芯片堆叠技术可以分为多种类型,包括3D堆叠技术、2D堆叠技术和芯片级封装等。其中,3D堆叠技术是指在芯片或结构的 Z 轴方向上形成三维集成、信号连接以及晶圆级、芯片级和硅盖封装等功能,以实现更高的性能和更小的尺寸。2D堆叠技术是指在芯片或结构的 X 轴和 Y 轴方向上形成二维堆叠,以实现更高的性能和更小的尺寸。

芯片封装是指将多个芯片封装在一起,形成一个更大的芯片。这种方式可以实现更高的可靠性和更高的性能,但是需要更高的工艺和更复杂的设备。

芯片合封技术带来的效果也很明显,可以帮助企业降本增效,并且稳定性高,合封后同行也难抄袭,还可以进一步减少pcb面积。从企业的角度,合封芯片慢慢会成为消费级市场的首选芯片。在这方面,宇凡微坚持投入,研发合封芯片,目前在国内占有很大的市场,宇凡微还提供合封芯片定制,单片机供应,在mcu芯片上,帮助企业减少了大量成本。

审核编辑黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54475浏览量

469804 -

封装

+关注

关注

128文章

9341浏览量

149091

发布评论请先 登录

相关推荐

热点推荐

半导体封装引线键合技术:超声键合步骤、优势与推拉力测试标准

在半导体封装领域,引线键合是连接芯片与外部电路的核心工序,直接决定电子器件的可靠性与性能,而超声键合作为主流的引线键合技术,凭借高效、低温、可靠的优势,广泛应用于各类

NTC热敏芯片键合工艺介绍

随着半导体技术的持续创新及进步,NTC热敏芯片键合工艺也不断发展。目前,芯片键合工艺为顺应行业发展需求,正逐步往高度集成、低功耗、高可靠的方

热压键合工艺的技术原理和流程详解

热压键合(Thermal Compression Bonding,TCB)是一种先进的半导体封装工艺技术,通过同时施加热量和压力,将芯片与基板或其他材料紧密连接在一起。这种技术能够在微

引线键合的三种技术

微电子封装是芯片成为功能产品的最后一步。它不仅为芯片提供电气连接、散热通道,还承担物理支撑与保护作用。封装质量直接影响器件性能,其中,互连技术尤为关键。研究表明,25%~30%的半导体失效源于

IGBT 芯片平整度差,引发键合线与芯片连接部位应力集中,键合失效

一、引言 在 IGBT 模块的可靠性研究中,键合线失效是导致器件性能退化的重要因素。研究发现,芯片表面平整度与键合线连接可靠性存在紧密关联。当芯片表面平整度不佳时,键

芯片制造中的键合技术详解

键合技术是通过温度、压力等外部条件调控材料表面分子间作用力或化学键,实现不同材料(如硅-硅、硅-玻璃)原子级结合的核心工艺,起源于MEMS领域并随SOI制造、三维集成需求发展,涵盖直接键合(如SiO

Silicon PIN 二极管、封装和可键合芯片 skyworksinc

电子发烧友网为你提供()Silicon PIN 二极管、封装和可键合芯片相关产品参数、数据手册,更有Silicon PIN 二极管、封装和可键合芯片的引脚图、接线图、封装手册、中文资料

发表于 07-14 18:32

微流控芯片的封合工艺有哪些

微流控芯片封合工艺旨在将芯片的不同部分牢固结合,确保芯片内部流体通道的密封性和稳定性,以实现微流控芯片在医学诊断、环境监测等领域的应用。以下

什么是引线键合?芯片引线键合保护胶用什么比较好?

引线键合的定义--什么是引线键合?引线键合(WireBonding)是微电子封装中的关键工艺,通过金属细丝(如金线、铝线或铜线)将芯片焊盘与外部基板、引线框架或其他

芯片合封的技术有哪些

芯片合封的技术有哪些

评论