高效的超高压功率转换设备(电压>20kv)需要比硅的能隙大得多的半导体。宽带隙(WBG)半导体碳化硅(SiC)已经成熟成为电力电子的商业技术平台,但超宽带隙(UWBG)(带隙>4.5eV)半导体器件有可能实现更高电压的电子设备。候选UWBG半导体包括氮化铝(AlN)、立方氮化硼和金刚石,但在过去十年中,研究活动增加最多的可能是氧化镓(Ga2O3)。这种兴趣的部分原因是由于其4.85 eV的大带隙和晶体生长方面的突破,导致了2012年第一个Ga2O3晶体管的演示。Ga2O3有希望成为电力电子平台,但在未来十年将这种UWBG半导体投入商用存在挑战。

如果超高压电子技术渗透到下一代电网控制和保护、超快电动汽车充电器或具有尺寸、重量和功率优势的高效负载点转换器等应用领域,那么吸引了许多行业注意力的电气化进程可能会被颠覆性地加速。虽然碳化硅器件的成本比传统的硅电力电子产品高,但在系统级,由于电路要求更简单,预计这些成本将被节省的费用所抵消。

如果出现可行的UWBG技术平台,则可以实现超过20kV的非常高的电压和高开关速度的功率转换。即使在10kv下,也很难在不牺牲电路效率的情况下将功率转换器的开关频率提高到10khz以上。UWBG半导体本质上需要更薄的器件层,从而减少传导损耗(与通道电阻成正比)。通过较小的UWBG器件减少的载波传输时间也将减少开关损耗(与电容成正比),并在不牺牲输出功率的情况下为高速电子设备提供平台。这种高速功率晶体管在电力电子行业将是破坏性的,因为系统体积与频率成反比。

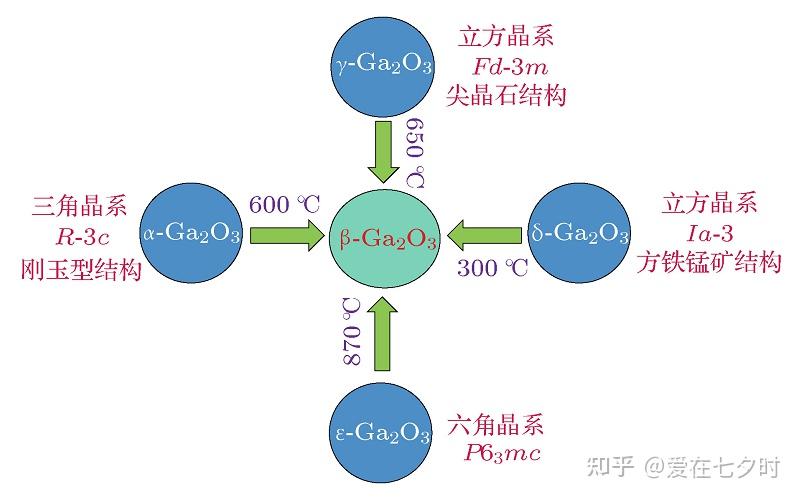

在六个结晶Ga2O3相中,低对称单斜β- Ga2O3由于其在高温(>650°C)下的热稳定性,在其发展周期中走得最远,下面的讨论涉及到该相。与其他WBG或UWBG半导体不同的是,最初为硅基片开发的熔体生长方法已经被用于商业化Ga2O3衬底。β- Ga2O3晶圆已达到4英寸(100毫米)的商业里程碑,并有望在2027年达到6英寸(150毫米)的尺寸。与此同时,高质量外延的基础设施正在扩大,以跟上不断增长的Ga2O3基片尺寸。Ga2O3外延生长的方法,如化学气相沉积(CVD)、分子束外延和卤化物气相外延等,正在被广泛研究,目的是生产最高质量的材料。

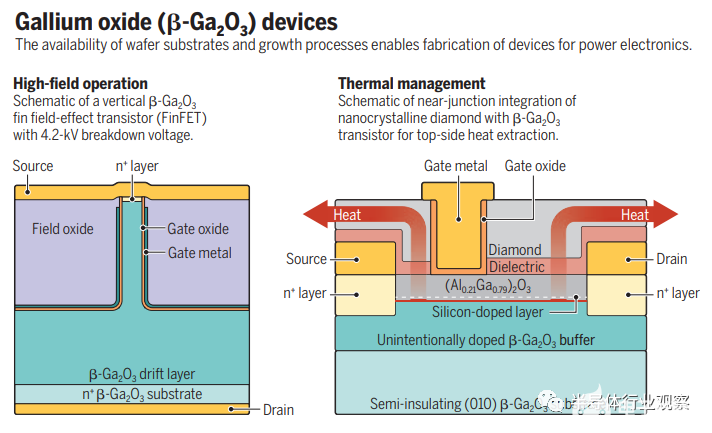

尽管UWBG技术的基本基础设施构建模块已经进入了开发周期,但研究人员仍在积极探索UWBG设备架构。垂直场效应晶体管(FET),如FinFET(见图左),理论上可以阻挡非常高的场,但更容易受到外延层扩展缺陷的影响。横向晶体管,如异质结FET(见图右),由于其更小的电容和更短的传输时间,有可能更快更有效地切换,而且它还可以使用Ga2O3三元合金,在这种情况下是β-(Al xGa1-x) 2O3,以进一步提高功率性能。

氧化镓(β-Ga2O3)器件

浅层能量供体和受体(带电杂质)的存在困扰着所有UWBG半导体,因为越来越宽的能隙通常会使外部杂质驻留在离传导带(或价带)更远的地方。然而,对于Ga2O3来说,硅是一种极好的外部浅供体,它能够实现从1014 cm-3以下到1020cm-3以上的广泛可控电导率。可控的n型电导率甚至延伸到三元合金(Al xGa1-x) 2O3,它有更宽的带隙,找元器件现货上唯样商城也可根据相和Al浓度调节。此外,CVD生长的同质外延β-Ga2O3的纯度只有硅超过。最近,通过无意受体(2×1013cm-3,~0.06%的给体补偿)的超低水平背景使同质外延CVD Ga2O3具有极高的低温迁移率(23000 cm2 V-1 s-1),这可能源于晶格中无意形成的点缺陷。

然而,要在这种纯度水平上生长非常厚(>30 μm)的外延β-Ga2O3是非常具有挑战性的,它的发展需要与SiC在超高功率开关应用领域竞争。在高压Ga2O3器件商业化之前,对Ga2O3外延缺陷的理解必须在未来几年内取得进展。点缺陷,如空位及其相关复合体(如空位-间质缺陷)以及厚外延层中的扩展缺陷,目前抑制Ga2O3器件尺寸。总的来说,Ga2O3中的缺陷表征有望成为一个丰富的研究领域,这也将使任何希望用有用的设备尺寸打破20kv障碍的Ga2O3电力电子商业企业能够实现这一目标。

对于电力电子来说,开发p型(空穴载流子)材料是必要的,因为Ga2O3中的空穴形成局域极化子,导致自俘获现象,限制了它们的传导。无论器件几何形状如何,Ga2O3中p型导电性的缺失对高电场管理提出了挑战,任何实际的解决方案都需要对先前开发的半导体所没有面临的异质集成进行创新。

不同于p型半导体,如SiC、氮化镓(GaN)或金刚石,WBG p型氧化镍(NiO)可以在室温下溅射,因此有利于与Ga2O3器件集成。最近的研究,如Zhang等人演示的8 kv NiO/Ga2O3 p-n二极管,已经表明,通过将异质结与这些器件中的场管理和电荷平衡相结合,可以潜在地管理Ga2O3中p型电导率的缺乏。如果开发出与p型WBG半导体(如GaN或AlN)的稳健异构集成,则Ga2O3作为电力电子材料的前景将大大增强。这样的发展可能导致可靠的结势垒肖特基整流器商业化,就像SiC的情况一样。

在实际高压电子器件中使用UWBG材料的关键要求是在表面上有效的电场终止。氮深受主在使Ga2O3几乎绝缘和产生可减小电场的有效介电层方面是有效的。选择性离子注入可以在器件制造过程中形成导电和绝缘表面区域。干蚀刻是制造这种图案的一个常见的加工步骤,它会引入影响器件可靠性的表面缺陷。如果图案可以完全通过离子注入来实现,那么干蚀刻可能完全被消除。与其他UWBG材料不同的是,Ga2O3甚至可以在磷酸中湿蚀刻,并使用气相Ga蚀刻,这两种方法都可以消除等离子蚀刻带来的化学和机械损伤,因为等离子蚀刻总是会在蚀刻表面引入缺陷。在开发Ga2O3专用制造工艺的同时,开发高质量厚外延层,可以在下一个十年中加速Ga2O3器件的商业化,至少可以达到双端器件(如二极管)的规模。

必须仔细考虑Ga2O3极低的导热系数(11到27 W m-1K-1)。Ga2O3晶体管的冷却甚至比GaN晶体管更关键,后者也有自热效应。尽管Ga2O3器件在运行过程中输出的功率与GaN器件相比仍然要低一个数量级,但为GaN开发的顶部和底部侧冷却方法可以应用于Ga2O3。事实上,用AlN或纳米晶金刚石覆盖横向晶体管可以实现Ga2O3 5-6w mm-1的直流输出功率,这与20世纪90年代GaN高电子迁移率晶体管的早期结果类似。具有高导热性的异质集成WBG p型半导体,如SiC, GaN,甚至金刚石,尤其适用于p-n和结势垒肖特基整流器。

回顾WBG半导体的早期商业化努力,SiC的成功在一定程度上是由大量的政府投资和持续创新的科研努力所驱动的。解决碳化硅微管和基面位错缺陷问题依赖于先进的表征技术,如紫外光致发光成像和光谱学。材料科学家们继续发展他们对直径更大的SiC晶圆缺陷的理解。

在厚(>30 μm)Ga2O3外延层中理解和控制点缺陷和扩展缺陷也需要类似的努力。政府的资金对于早期支持这些努力是至关重要的。美国海军研究办公室于2017年启动了小型企业技术转让项目,旨在启动β-Ga2O3 CVD的开发,该项目在项目结束前实现了该能力的商业化,凸显了该新技术的重要性。最近颁布的美国芯片和科学法案不仅将为芯片制造设施提供资金,还将向美国商务部和美国国防部提供130亿美元,用于半导体和微电子研究和开发。这些投资将在未来几年刺激UWBG半导体和相关材料研究的额外资金,期望异构集成半导体模块的多样化组合将克服使用特定半导体制造的芯片的缺点。此外,只有在无源器件能够跟上的情况下,更高频率的器件才会在系统级别上发挥作用。磁性材料的进步也有助于防止电感器和变压器等部件在更高频率下变得太过损耗。

-

变压器

+关注

关注

162文章

8106浏览量

148464 -

IC

+关注

关注

36文章

6471浏览量

186316 -

电感器

+关注

关注

20文章

2651浏览量

73925 -

电力电子

+关注

关注

32文章

736浏览量

51091 -

氧化镓

+关注

关注

5文章

91浏览量

10904

发布评论请先 登录

内置氮化镓成主流?AHB技术你又了解多少?

氧化镓器件新突破!光导开关击穿电压突破10000V

日本氧化镓技术再获突破:六项成果集中发布,低成本量产指日可待

四探针方阻仪高精度表征:铟镓锌氧化物/银/铟镓锌氧化物多层膜的光电性能

第四代半导体“氧化镓(Ga2O3)”材料的详解

电流密度1 kA/cm²,二极管耐压比SiC大3倍!氧化镓器件商业化!

氧化镓破局!江苏拓能半导体科技有限公司工业电机驱动系统著作权落地,解锁高效节能新范式

氧化镓射频器件研究进展

谈谈热门的氧化镓

谈谈热门的氧化镓

评论