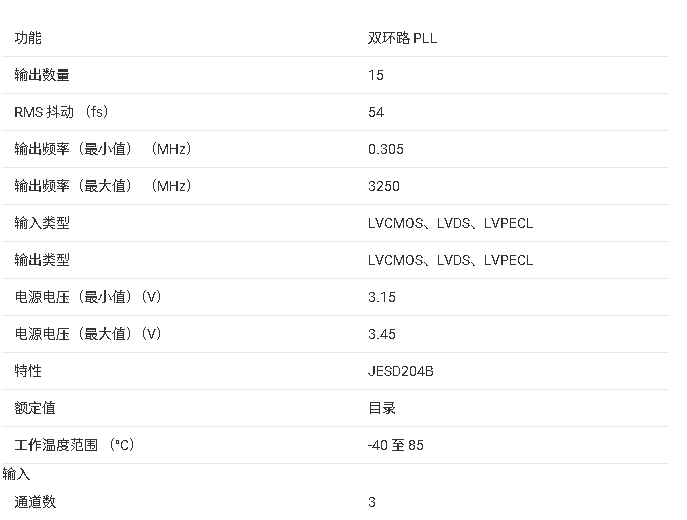

【问题11.31】如果我这里有两个9144芯片,他们之间如何同步呢?答:1. 时钟同步,采用同一个时钟芯片,由这个时钟芯片产生多路时钟给这些AD9144,由于时钟源是相同的,所以时钟都是一样的。这样可以保证时钟的同步。 2. 由于都是一个FPGA发数据,按照JESD204B排列数据分配给各条LANE,这样就可以了。【问题11.32】JESD课程是用Veriiog代码实现还是用XILINX的IP核?答:该课程使用了IP核来实现 |

【问题11.33】是否包含有高速AD/DA的项目?最高速率是多少?有多少路?

答:激光工程项目中,包含有高速ADC AD9684,速率是500M,目前是支持一路的实现。 精密仪器项目中,包含有高速的DAC AD9144,目前实现的最高速率是1G,支持2路输出。

【问题11.34】精密仪器项目中,AD9144的AD测量范围,DA输出的范围,以及采样率分别是多少?

答:AD9144是一款DAC芯片,所以没有AD测量范围。DA采样率我们实现的是1G,实质可达1.8G。DA输出范围以及更多信息,请参考以下数据手册。

AD9144-FMC-EBZ RevB Sch

【问题11.35】JESD204B课程中,是那种并口高速adc用的那种协议么?

答:不是高速并行口,而是高速串行口,即SERDES接口来实现,单根线的速率可达到10G。

【问题11.36】就业班企业项目里视频拼接MIPI项目有用到IP核吗?需要额外交IP核费用吗?

答:MIPI项目是用的lattice芯片,lattice的此IP是免费的,学习此项目无需额外缴费。

【问题11.37】申请JESD的临时License提示不符合出口规定,有没有什么其它办法?答:换了个企业邮箱账号就行了

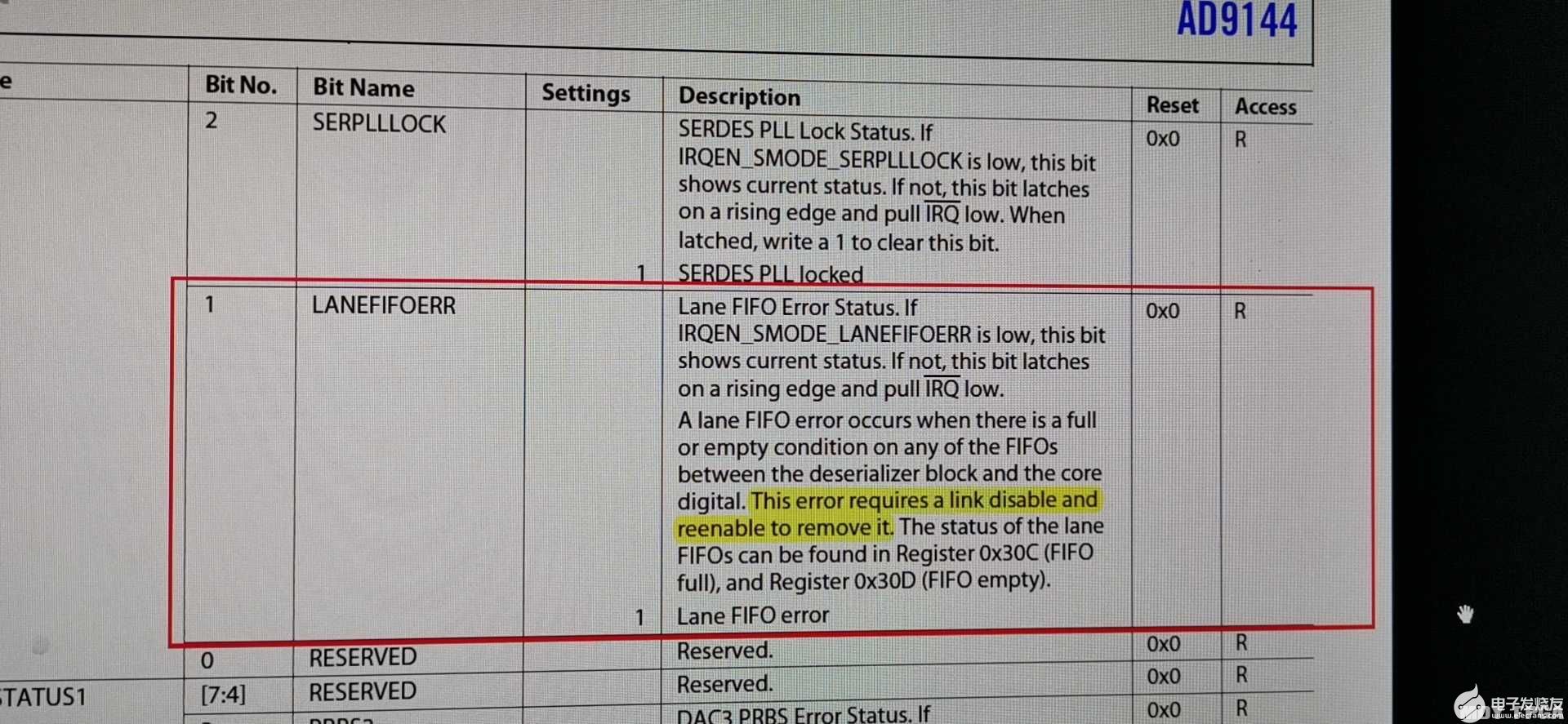

【问题11.38】一,首先我得读9156寄存器,二,我的读9154{我自己的dac}三,用 dpg..现在dpg软件驶不了,麻烦解答一下答:我们提供的例程,已集成在工程里面的,全部代码是FPGA代码。【问题11.39】请问9144用的是mose0,配置完后,CGS可以过,可以读到寄存器470是FF,8个lane都收到了k28.5,但是寄存器023的bit1一直在01之间不停的跳动,代表FIFO的读写一直有错误,查看30c和30d也能看到错误标记,此时发送sysref的话,ILAS也能过,但是470,471,472,473都在不停的跳动,sync标记也是忽高忽低,此时链路不稳定,给tx核送数据,在频谱仪上能看到9144的输出,但是因为链路不稳定,输出会不停的闪烁,理论上讲,链路稳定的话,470.471.472.473都应该回读FF才对,我想请教一下,是什么导致了9144配置完后fifo的读写标记一直报错呢?也就是寄存器023的bit 1

答:如果是自己做的硬件板,则有可能是硬件的稳定性问题。请检查硬件电路。【问题11.40】请教一个问题,204b时序不行。12.5g,312.5M的核时钟。一个dac时序违例不严重能工作,另一个不行,怎么处理答:解决时序违例,其思路是减少组合电路逻辑。如果确实无法减小,那就只能降低时钟频率了。您使用的315.5M是工作时钟的话,那确实是太高了,建议可以将工作时钟降为156.25M【问题11.41】请问按键是有4位., 但代码中只使用了0位和1位, 这按键有没有顺序要求, 先按哪个再按哪个? 然后这个这个按键信号作为使能信号, 是只持续一个时钟, 还是需要一直为高?

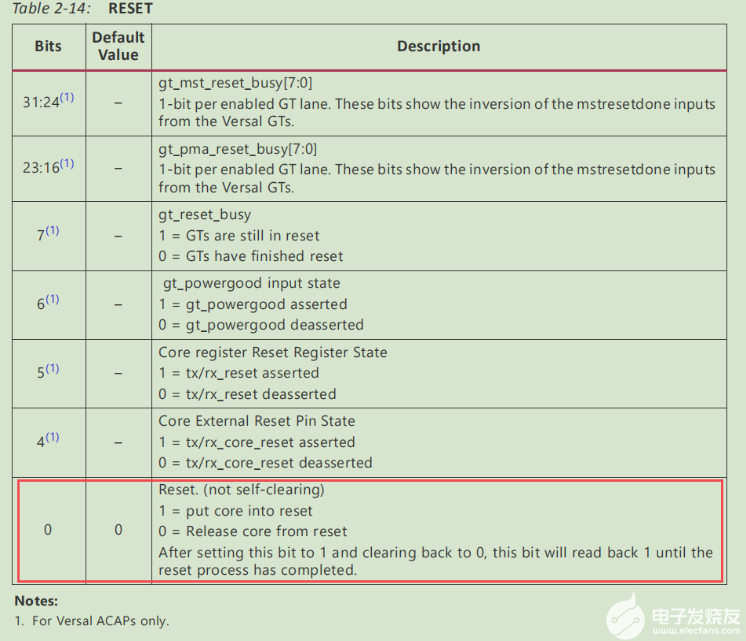

答:先按启动有效的按键,再按改变频率的按键,具体请看使用说明。【问题11.42】请问在给JESD204C IP核配置的时候,读取0x020 RESET寄存器的值,读到的值是0x081,说明这个IP一直处于复位状态,无法从复位状态退出,可能是什么问题呢?

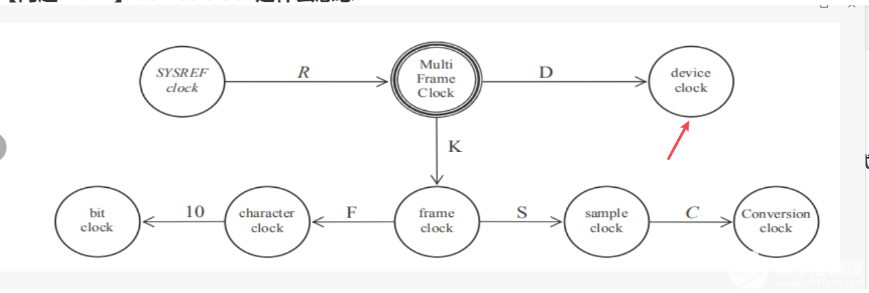

答:检查一下所有的时钟和复位信号,一般都是跟这些信号有关【问题11.43】请问FPGA中的204B IP核,其配置是在哪里定义?答:JESD204B的IP核配置,其地址在addr.coe文件中定义;其寄存器值在data.coe文件中定义。【问题11.44】device clock是什么意思?

答:可以认为是AD9516给FPGA的一个多帧时钟,用于同步多帧的,可以认为D个多帧就发一个上升沿,这样就好同步了。具体有一个视频,可以看JESD204B协议04_实践_协议各个时钟的关系。

审核编辑:符乾江

-

FPGA

+关注

关注

1656文章

22299浏览量

630574 -

芯片

+关注

关注

462文章

53581浏览量

459598

发布评论请先 登录

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

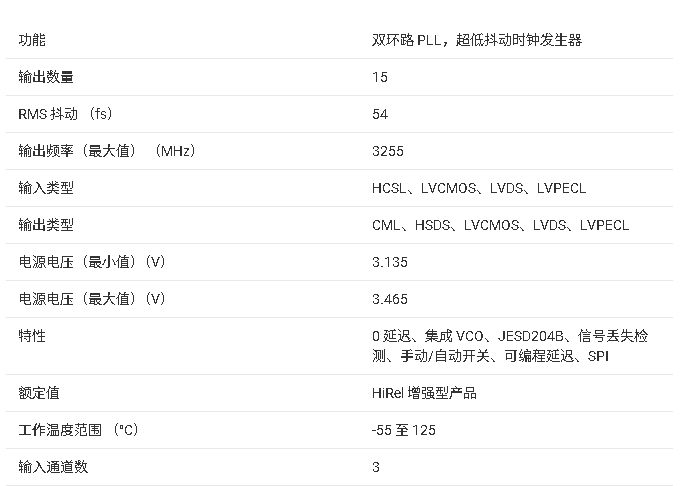

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册

AD9680 JESD204B接口的不稳定会导致较大的电流波动,怎么解决?

使用jesd204b IP核时,无法完成综合,找不到jesd204_0.v

JESD204B有专用于ADC/DAC和FPGA或ASIC的接口吗?

JESD204B使用说明

MDY专题课产品的问题解答汇总(JESD204B)

MDY专题课产品的问题解答汇总(JESD204B)

评论