在工艺节点进入了28nm之后,因为受限于硅材料本身的特性,晶圆厂和芯片厂如果还想通过晶体管微缩,将芯片性能按照之前的步伐提升,这是基本不可能的,为此各大厂商现在都开始探索从封装上入手去提升性能,台积电是当中的一个先驱。

首先,打入众多客户内部的台积电Bumping服务是台积电封装业务的一个基本以来。据介绍,超过90%的7nm客户都选择了台积电的bumping服务。

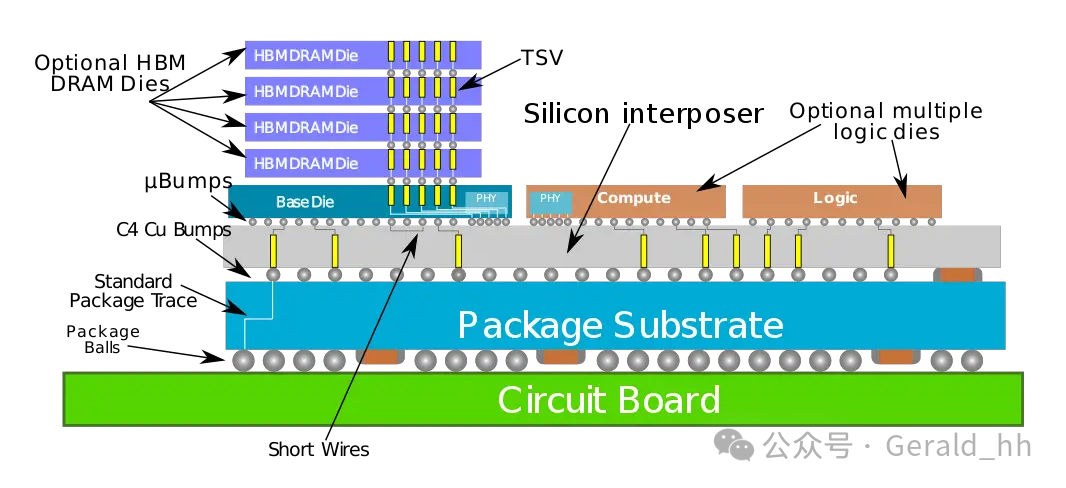

其次就是Cowos业务。八年前。在台积电2011 年第三季法说会上,台积电创始人张忠谋毫无预兆掷出重磅炸弹──台积电要进军封装领域。他们推出的第一个先进封装产品是CoWoS(Chip on Wafer on Substrate)。意思就是将逻辑芯片和DRAM 放在硅中介层(interposer)上,然后封装在基板上。

据介绍,自推出以来,台积电COWOS封装技术获得了超过50个客户的选用,公司在这个封装技术上也获得了业界最高的良率。在他们看来,COWOS将会在未来越来越重要,市场需求也会逐渐提升,台积电也会从各个角度来优化,简化客户COWOS设计流程,加快产品的上市速度。

这个封装技术也能为创新提供各种各样的支持。

除了bumping 和COWOS之外,InFO(Integrated Fan-Out)也是台积电封装武器库里的另一个杀手锏。所谓InFO,就是整合型扇出技术。这是一项非穿孔技术,是专为如移动及消费性产品等对成本敏感的应用开发出来的封装技术。

据介绍,这种技术分为三类:一种是InFO_oS(Integrated Fan-Out on substrate),另一种是InFO_mS( Integrated Fan-Out memory on substrate),还有一种是InFO_POP.

此外,台积电还推出了另类的InFO工艺SoW(System on Wafer)。

台积电方面表示,这两个封装技术将会在公司的先进封装布局中扮演重要角色,也能够为AI、服务器、网络、AI推理和移动等芯片提供全方位的支持。

根据台积电的划分,以上几种属于他们的后段3D封装。为了进一步推动芯片性能的提升,台积电也推出了前道3D封装工艺SOIC(system-on-integrated-chips)和全新的多晶圆堆叠(WoW,Wafer-on- Wafer)。

台积电方面进一步表示,通过后段3D封装的后果是获得了一个可以直接使用的芯片,而使用前道封装获得了则只是一个异构芯片,还需要我们进行封装才能获得可用的芯片。

所谓SoIC是一种创新的多芯片堆栈技术,能对10纳米以下的制程进行晶圆级的接合技术。该技术没有突起的键合结构,因此有更佳运作的性能。

具有革命性意义的工艺技术Wafer-on-Wafer (WoW,堆叠晶圆),就像是3D NAND闪存多层堆叠一样,将两层Die以镜像方式垂直堆叠起来,有望用于生产显卡GPU,创造出晶体管规模更大的GPU。据介绍,WoW技术通过10μm的硅穿孔方式连接上下两块die,这样一来可以在垂直方向上堆叠更多die,也意味着die之间的延迟通信极大地减少,引入更多的核心。

-

台积电

+关注

关注

44文章

5810浏览量

177053 -

CoWoS

+关注

关注

0文章

170浏览量

11536

原文标题:传感器专业微信群,赶紧加入吧!

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT Tsi578硬件设计指南:从信号到布局的全面解析

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

高通MWC2026全栈出击:从5G-A到AI原生6G布局,硬核产品震撼亮相

【深度报告】CoWoS封装的中阶层是关键——SiC材料

先进封装市场迎来EMIB与CoWoS的格局之争

CoWoS产能狂飙的背后:异质集成芯片的“最终测试”新范式

HBM技术在CowoS封装中的应用

TP-LINK技术解析:从路由器巨头到Wi-Fi 7布局

CoWoP能否挑战CoWoS的霸主地位

从InFO-MS到InFO_SoW的先进封装技术

普莱信成立TCB实验室,提供CoWoS、HBM、CPO、oDSP等从打样到量产的支持

HarmonyOS NEXT应用元服务布局合理使用布局组件

从选型到布局:MDDTVS二极管在ESD防护中的工程实战指南

TSMC:从COWOS到WOW的布局

TSMC:从COWOS到WOW的布局

评论