前言: 当台积电、日月光等企业头宣布加速扩张CoWoS先进封装产能,当资本市场以半导体设备股的上涨予以回应,一个明确的信号正在释放:异质集成(Heterogeneous Integration)的时代已全面加速。然而,在这场以“封装”为名的产能竞赛背后,一个更深刻、更棘手的挑战正浮出水面:我们如何确认,那些通过数万根微米级凸点(bump)和硅中介层(interposer)精密“焊接”在一起的不同芯粒(Chiplet),能够作为一个整体,可靠地工作数年之久? CoWoS将制造复杂度从晶圆前道推向了封装后道,也从根本上颠覆了芯片“最终测试”的定义与范式。在这里,一场关于“系统级可靠性”的终极考核,正决定着这些昂贵“微系统”的真正价值。

一、 趋势洞察:从“芯片测试”到“微系统认证”的范式迁移

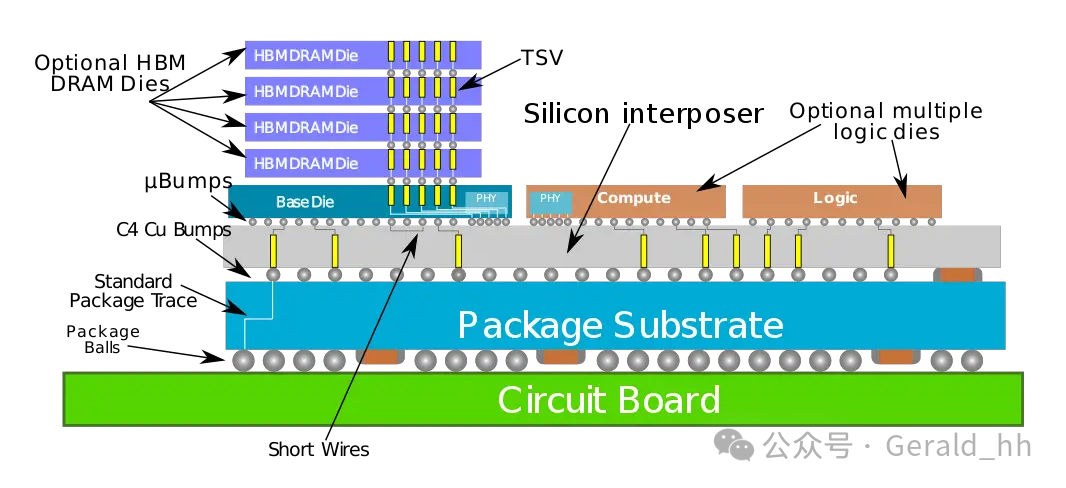

CoWoS产能的超预期需求,直接由GPU、ASIC等高性能计算芯片驱动。这些芯片将计算芯粒、高带宽内存(HBM)、I/O芯粒等异构单元集成于单一封装体内,实现了性能的飞跃。这一制造革命,使得传统的半导体测试金字塔——从晶圆测试(CP)到最终测试(FT)——出现了关键的“断层”。

封装不再是制造流程的终点,而是创造了一个全新的、更复杂的测试对象。测试的目标,从验证单个裸片(Die)的电性功能,跃升为认证这个由多个裸片、中介层、基板构成的 “微系统” 的整体行为。这包括:各单元间的电气互连是否完美无缺?在协同全速运行时,电源噪声和热量能否被有效管理?系统级的功能与长期可靠性是否达标?因此,系统级测试(System Level Test, SLT) 不再是一个可选项或补充项,而是成为决定CoWoS芯片能否出厂、能否赢得数据中心客户信任的强制性最终关卡。这标志着一场从“部件检查”到“整车路试”的范式迁移。

二、 技术挑战:异质集成“微系统”的四大考核难题

对CoWoS这类异质集成芯片进行终极考核,面临前所未有的复杂性,集中体现在四个相互关联的维度:

三维互连的“隐匿缺陷”筛查

芯粒间通过数以万计的微凸点连接,任何微小的空洞、虚焊或电迁移,都可能在高负载下引发间歇性故障。这些缺陷在静态或低速测试中难以暴露。挑战在于设计高频、高覆盖率的互连测试向量,能够在封装后有限的可访问性下,精确诊断出个别失效的互连通道或潜在弱连接,这需要与设计阶段协同规划的可测试性设计(DFT)作为基础。

系统级的“功耗-热-性能”协同验证

计算芯粒与HBM在协同工作时,会产生瞬间的极高功耗峰值,导致复杂的电源噪声和局部热点。测试必须模拟最严苛的真实工作负载(如AI训练中的矩阵运算),同时监测整个封装体的电压稳定性、电流纹波、热分布以及由此引发的时钟抖动和性能波动。单一芯片的测试环境无法复现这种多芯片耦合的“系统级工作态”。

异构单元的“协同启动”与烧录

CoWoS芯片在首次上电前,需要为一个包含CPU、GPU、HBM控制器等在内的“多核系统”进行初始化配置。烧录流程必须能够并行或有序地为不同架构、不同指令集的芯粒,载入正确的固件、微码、训练参数和安全密钥。这不仅要求烧录设备支持多协议,更需要一个顶层的“配置管理引擎”,确保所有组件能协调一致地启动,避免因配置冲突导致系统“死锁”。

封装后诊断与可追溯性的物理限制

一旦芯片被密封在封装体内,传统的物理探针诊断手段几乎失效。当SLT测试失败时,如何快速、低成本地定位故障是位于某个芯粒、互连还是中介层?这要求测试系统能提供极其丰富的数字诊断日志和性能遥测数据,并与前道晶圆测试数据、封装工艺数据进行关联分析,构建覆盖芯片全生命周期的“数字孪生”,以实现精准的根因分析。

解决方案:构建面向“微系统”的智能认证体系

应对上述挑战,需要构建一套全新的、贯穿设计、制造与测试的智能认证体系,其核心支柱如下:

设计-测试协同(DfT for SI/PI):推动在芯片与封装设计阶段,就将系统级的信号完整性(SI)和电源完整性(PI) 可测试性纳入规划。例如,在互连网络中植入监测电路,为关键电源网络提供可观测的测试点,从而在最终测试时能够“看见”封装内部的状态。

基于仿真的复合验证平台:建立一个结合 “电-热-力”多物理场仿真 的测试环境。在SLT阶段,不仅运行软件工作负载,更能根据仿真预测的“最坏情况场景”,动态调整测试向量的电压、频率和负载模式,主动激发并捕捉潜在的系统级边际失效。

高吞吐、多协议的协同配置与烧录站:开发新一代烧录解决方案,它应能理解整个CoWoS芯片的拓扑结构,像“交响乐指挥”一样,同步管理流向不同芯粒的数据流,并确保配置的原子性和一致性。同时,将每一次烧录操作与芯片的最终序列号、生产批次深度绑定,形成不可篡改的“系统出生证明”。

数据闭环与智能诊断:将SLT过程中采集的海量功耗、性能、温度数据,与CP测试数据、封装工艺参数进行大数据关联分析。利用机器学习算法,建立良率预测模型和早期失效预警系统,将测试从“事后筛选”部分转变为 “过程质量监控与优化” 的前瞻性工具。

结语:

CoWoS产能的狂飙,标志着半导体性能竞赛的主场,正从前道制程工艺逐步转向后道系统集成能力。而这场竞赛的终极裁判,正是那个能够确保这些复杂“微系统”在现实世界中万无一失的 “最终测试”新范式。

在您看来,推动CoWoS等异质集成技术大规模落地的最大测试瓶颈是什么?是高昂的系统级测试成本、缺乏统一的互连测试标准,还是故障定位与分析的极端困难? 欢迎在评论区分享您的专业见解与实践挑战。当芯片的“大脑”、“内存”与“神经网络”被封装进同一个“颅腔”,我们需要的,是一套能够透视其协同生命力的全新“体检”标准。在这一前沿领域,与具备从芯片级到系统级全面验证视野、并拥有深度数据整合能力的伙伴合作,正从可选项变为确保投资回报与产品成功的必选项。

审核编辑 黄宇

-

封装

+关注

关注

128文章

9330浏览量

149044 -

芯片测试

+关注

关注

6文章

181浏览量

21178 -

烧录

+关注

关注

8文章

325浏览量

37184 -

CoWoS

+关注

关注

0文章

170浏览量

11535

发布评论请先 登录

国产芯片出海狂飙:单月暴增近85%

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

芯粒设计与异质集成封装方法介绍

AI芯片发展关键痛点就是:CoWoS封装散热

CoWoS产能狂飙下的隐忧:当封装“量变”遭遇检测“质控”瓶颈

HBM量价齐飞,UFS加速普及:存储狂飙下的“最后质检”攻坚战

高算力低功耗背后的半导体革新

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

【2025九峰山论坛】破局摩尔定律:异质异构集成如何撬动新赛道?

HBM技术在CowoS封装中的应用

CoWoP能否挑战CoWoS的霸主地位

普莱信成立TCB实验室,提供CoWoS、HBM、CPO、oDSP等从打样到量产的支持

CoWoS产能狂飙的背后:异质集成芯片的“最终测试”新范式

CoWoS产能狂飙的背后:异质集成芯片的“最终测试”新范式

评论