由中国科学院微电子所、华进半导体共同出资成立的江苏中科智芯集成科技有限公司的晶圆级扇出型(FO)封装项目即将于2019年11月投产。

2018年3月,江苏中科智芯集成科技有限公司成立,承接华进半导体晶圆级扇出型封装产业化项目。中科智芯半导体封测项目位于徐州经济技术开发区凤凰湾电子信息产业园,占地50亩,投资20亿元,项目分两期建设。

2018年9月一期开工建设,投资5亿元,建成后将可形成年月能为12万片12英寸晶圆。主厂房于2018年11月底封顶;其他辅助建筑于2019年1月封顶,2019年7月净化装修施工基本完成,动力车间设备正在安装,预计8月份开始设备安装,9、10月份进行设备调试,11月初部分生产线投产。

中科智芯产品定位中高密度集成芯片扇出型(FO)封装与测试,高频率射频芯片封装的设计与制造。11月将陆续投产12英寸晶圆级扇出型封装,逐步实现单芯片扇出型封装、2D多芯片扇出型封装、3D多芯片扇出型封装量产。

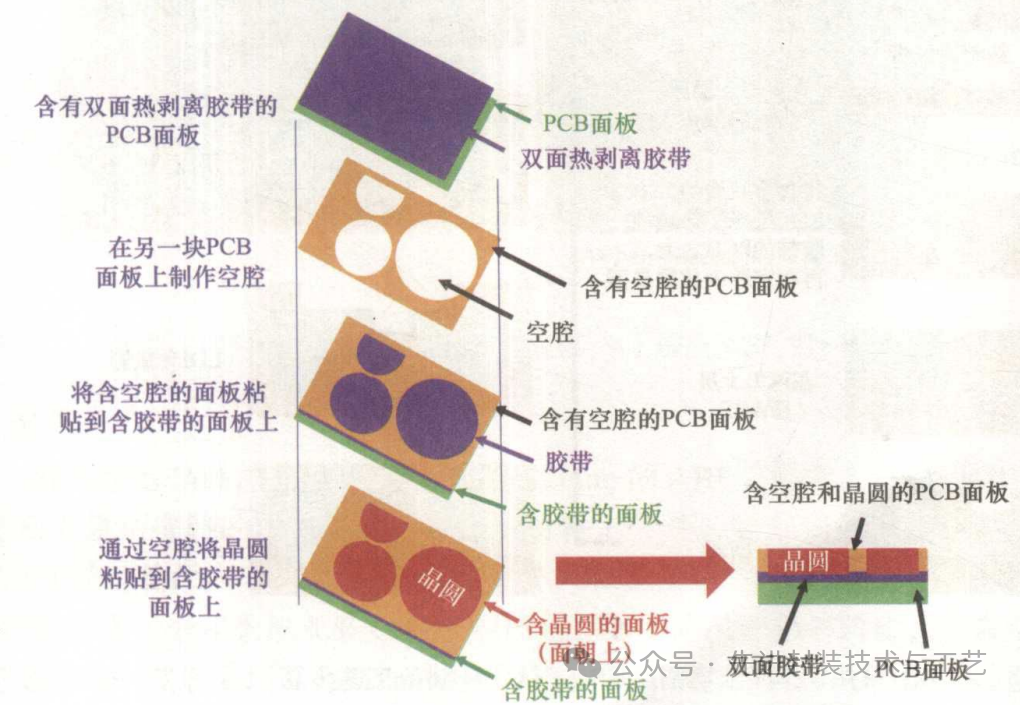

华进半导体相关人员表示,晶圆级扇出型封装是最高性价比的集成电路封装技术,无须使用印刷电路板,可直接在晶圆上实现芯片封装。具体来说,第一,结合内嵌式印刷电路板技术的系统级封装,虽符合移动设备小型化需求,然而供应链、产品良率(成本)存在很多问题;第二,硅穿孔(TSV)封装技术可以实现产品良率的问题,但设计难度较大、制造成本极高。与上述两种方案不同的晶圆级扇出封装(Fan-Out)技术,可在单芯至多芯片的封装中做到更高的集成度,而具有更好的电气属性,不仅降低封装成本,并且让系统计算速度加快,产生的功耗更小,更为重要的是,该技术能够提供更好的散热性能,并可以整合射频元件,使网络基带性能更加优良。

凤凰湾电子信息产业园内在中科智芯集成电路晶圆级封装项目外,还引入了联立LCD驱动芯片封装、爱矽封测等项目。联立LCD驱动芯片封装项目拟建设具有月产能2.4万片之8英寸芯片(晶圆凸块及测试)、封装(COG、COF)5千万颗集成电路生产能力的生产线厂房正在进行内部装修与机电安装,预计年内投产;爱矽封测项目规划年产5.4亿个产品,正在进行机电安装,预计年内投产。

中科智芯、联立、爱矽等封装项目投产后,将进一步补强徐州半导体封测产业链。

本文来源:麦姆斯咨询

-

中科智芯

+关注

关注

2文章

4浏览量

1961

发布评论请先 登录

什么是晶圆级扇入封装技术

中科智芯晶圆级扇出型封装即将投产,补强徐州短板

中科智芯晶圆级扇出型封装即将投产,补强徐州短板

评论