Altera的Cyclone V FPGA目前是业界系统总成本和功耗最低的FPGA,那我们该怎样为自己的设计选择Altera Cyclone V FPGA?参考本文...

2013-02-26 10:34:36 2680

2680 做芯片设计的各位,在某个时刻,你也许会产生一个想法,“为什么不自己设计一个处理器呢?”或许是手头的处理器并不好用;或许是想用的处理器贵的离谱;或许是你希望做出差异化的产品;又或者仅仅因为它是个诱人的挑战,你想尝试一下。。.既然如此,我很高兴能和你讨论一下怎么完成这个任务。

2017-05-17 10:51:43 4967

4967 本应用笔记介绍了FPGA (现场可编程门阵列)及其如何保护系统的关键功能和知识产权(IP)。本文探讨了IP保护的各种途径。SHA-1质询-响应认证被认为是最安全的方法。本文提出了一种能够保护基于SRAM的FPGA设计IP的高性价比认证方案。介绍了DS28E01和DS28CN01器件的特性。

2013-04-07 10:18:16 7539

7539

FPGA 对绝大多数的人来说相对有些陌生。经常有朋友问我,你们成天搞的这个 FPGA 到底是什么东西。 我想很难用一两句通俗易懂的语言解释什么是 FPGA ,因为当今的 FPGA 已经是一个非常复杂

2018-03-31 08:20:01 26705

26705 最近,我接手一个项目,这个项目不仅要求我使用FPGA,而且还要求我使用功能更强大的ARM。这都是我从未接触过的领域。在这个系列博客中,我将介绍我是如何将自己现有的MCU知识和经验运用到FPGA中

2018-09-25 07:44:00 6040

6040 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 8964

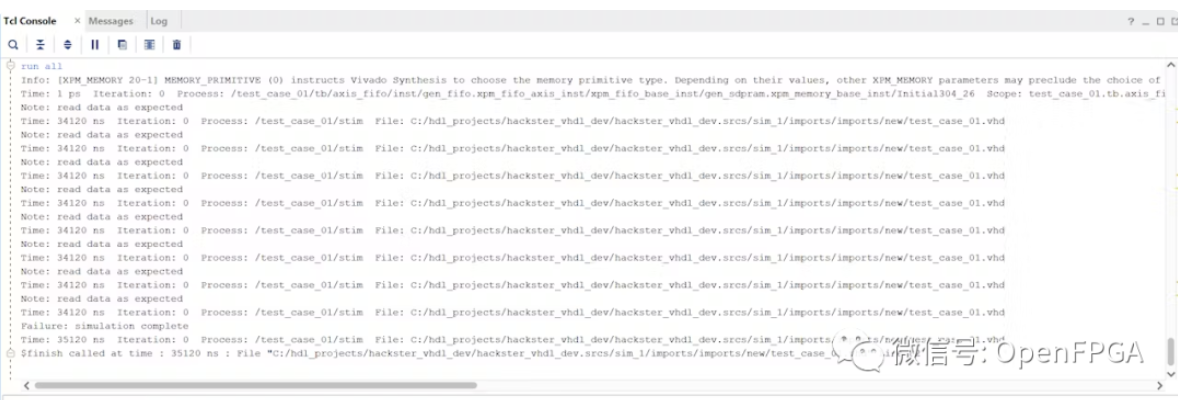

8964

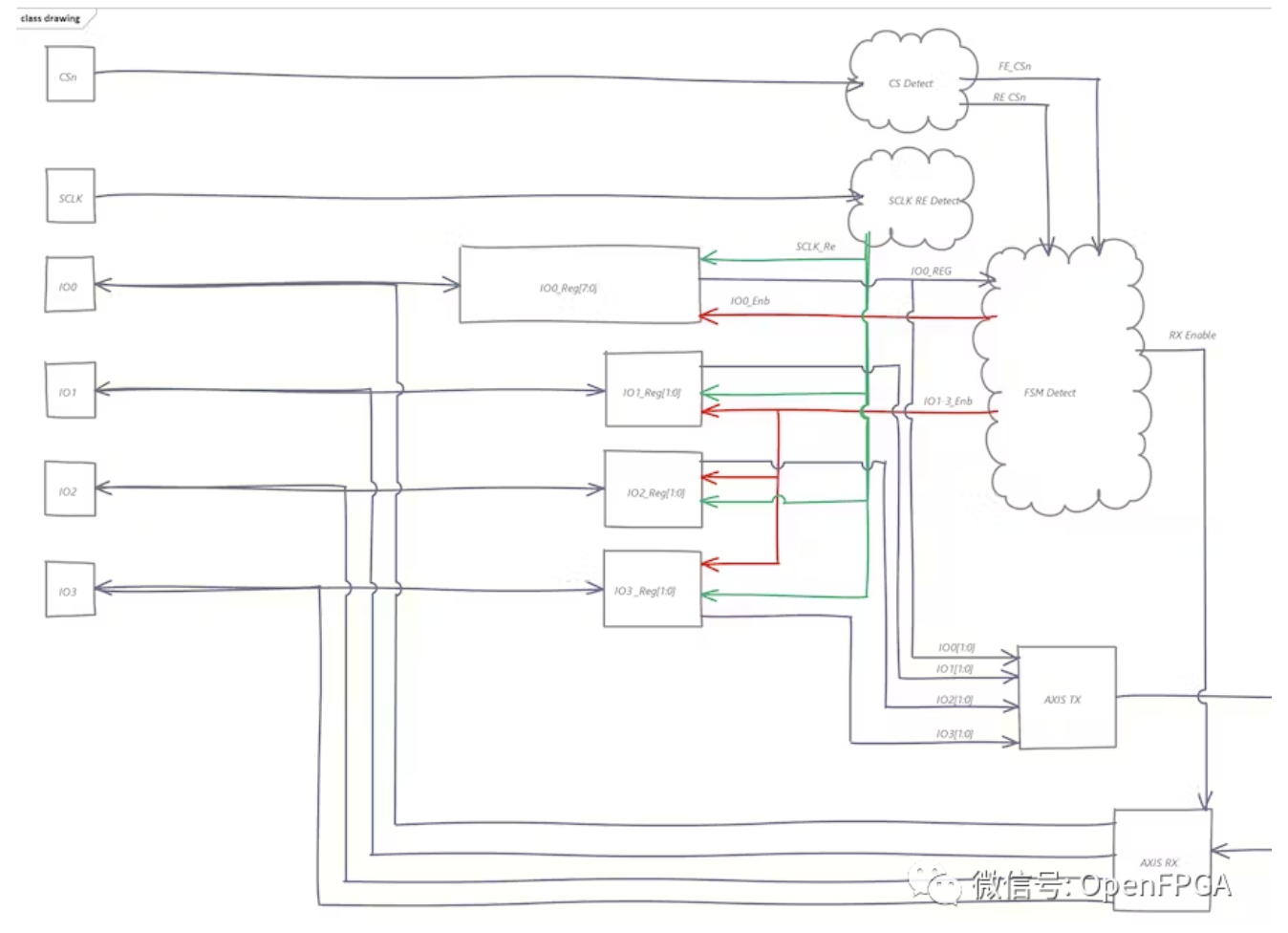

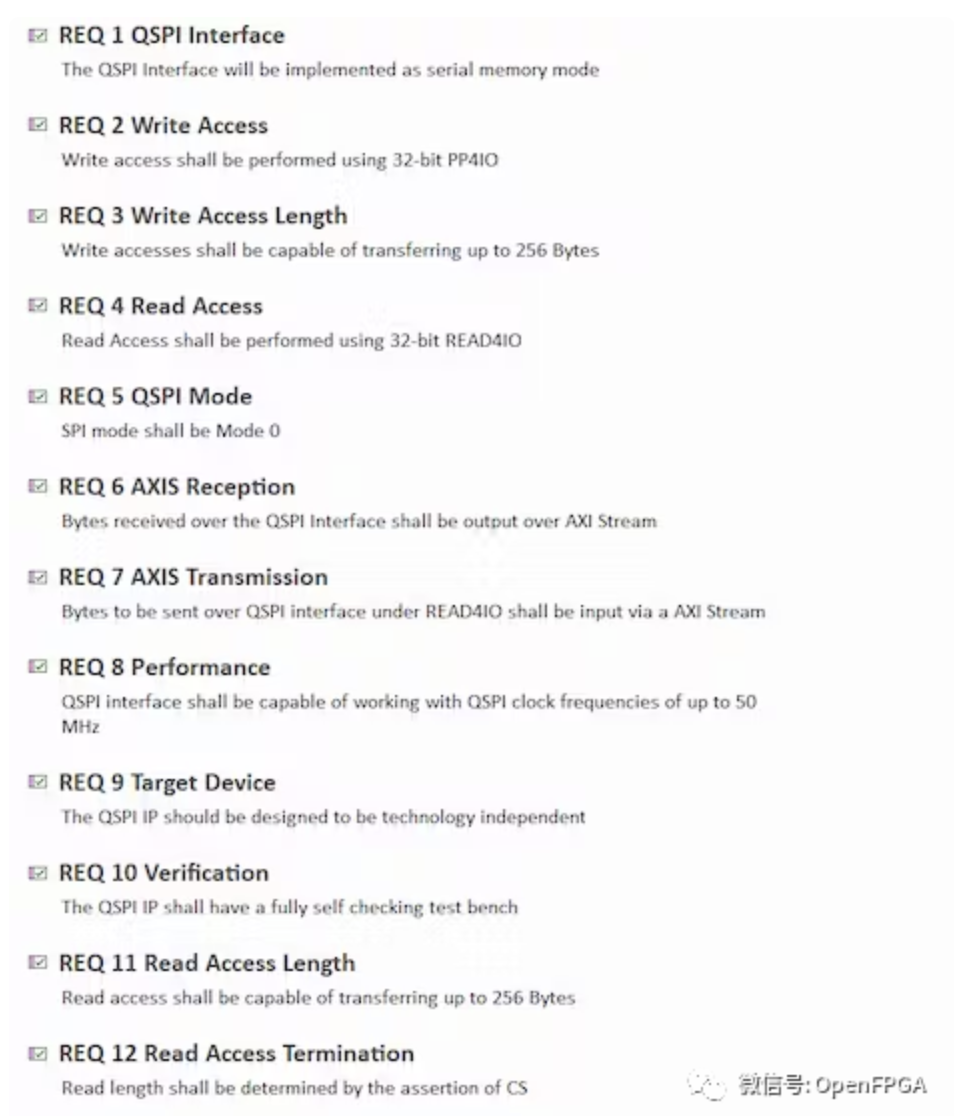

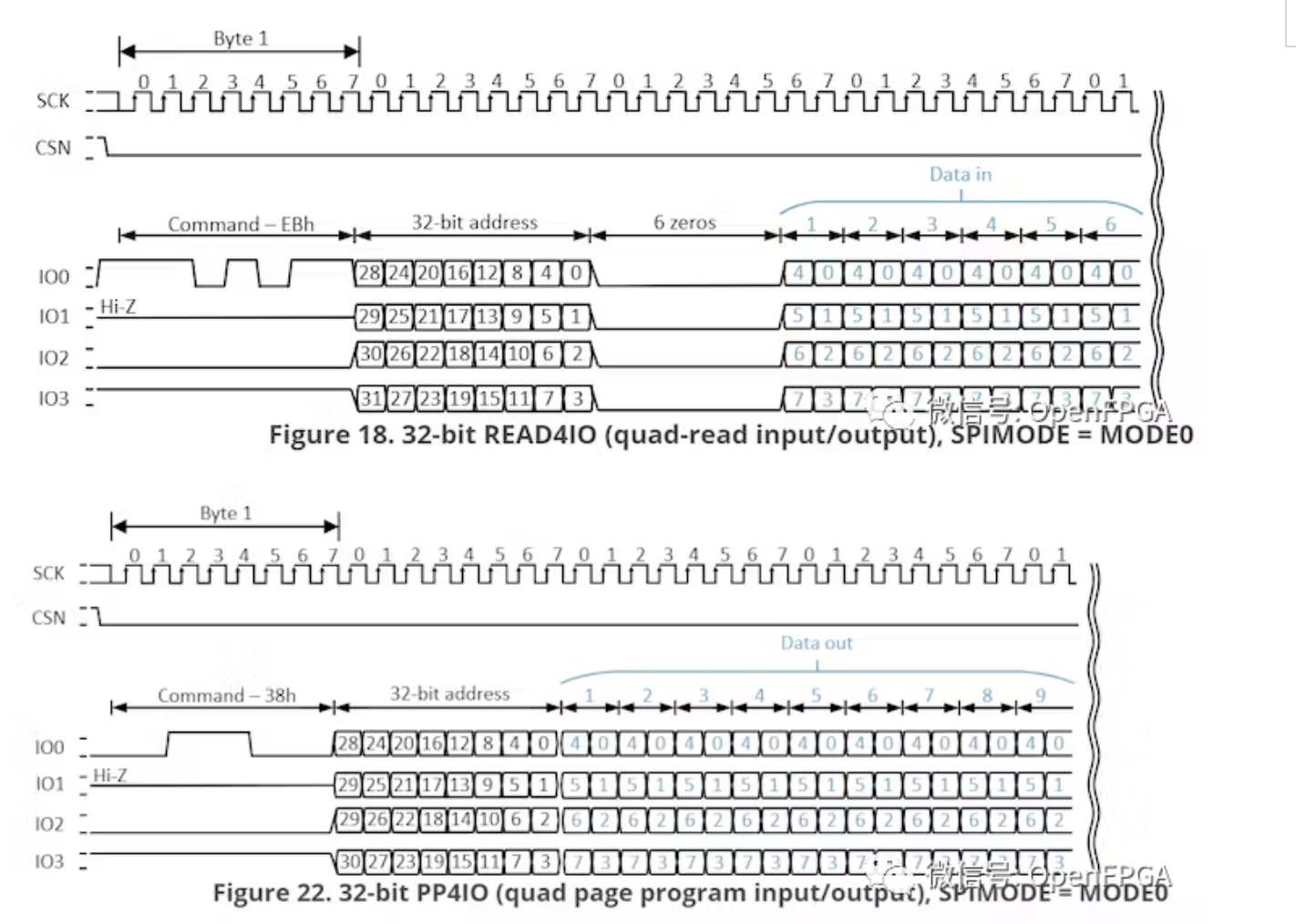

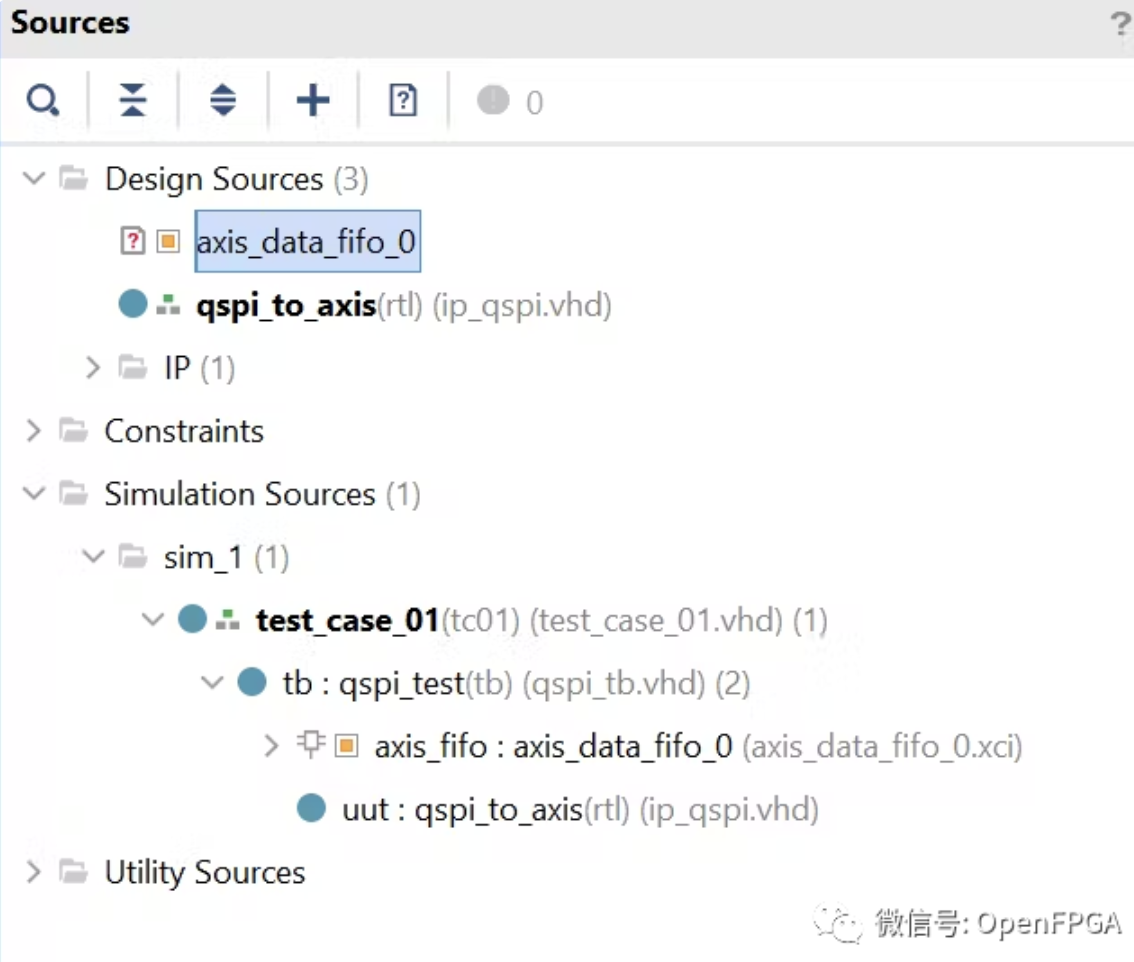

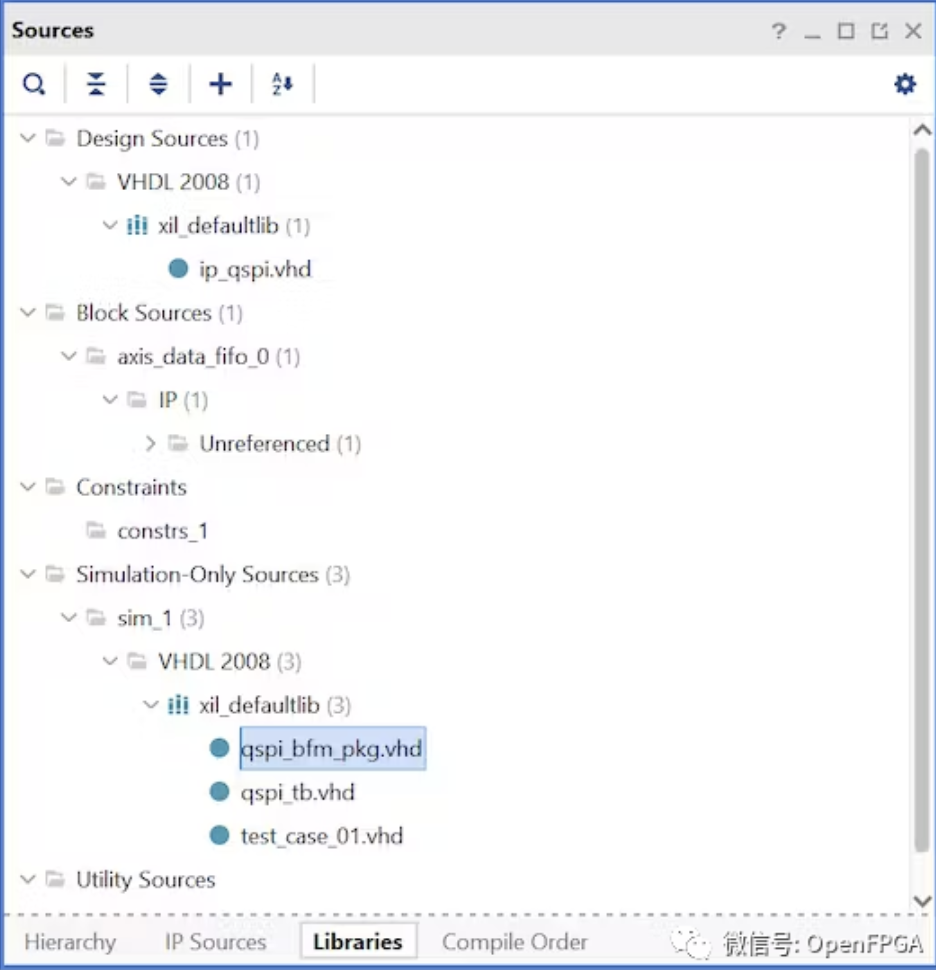

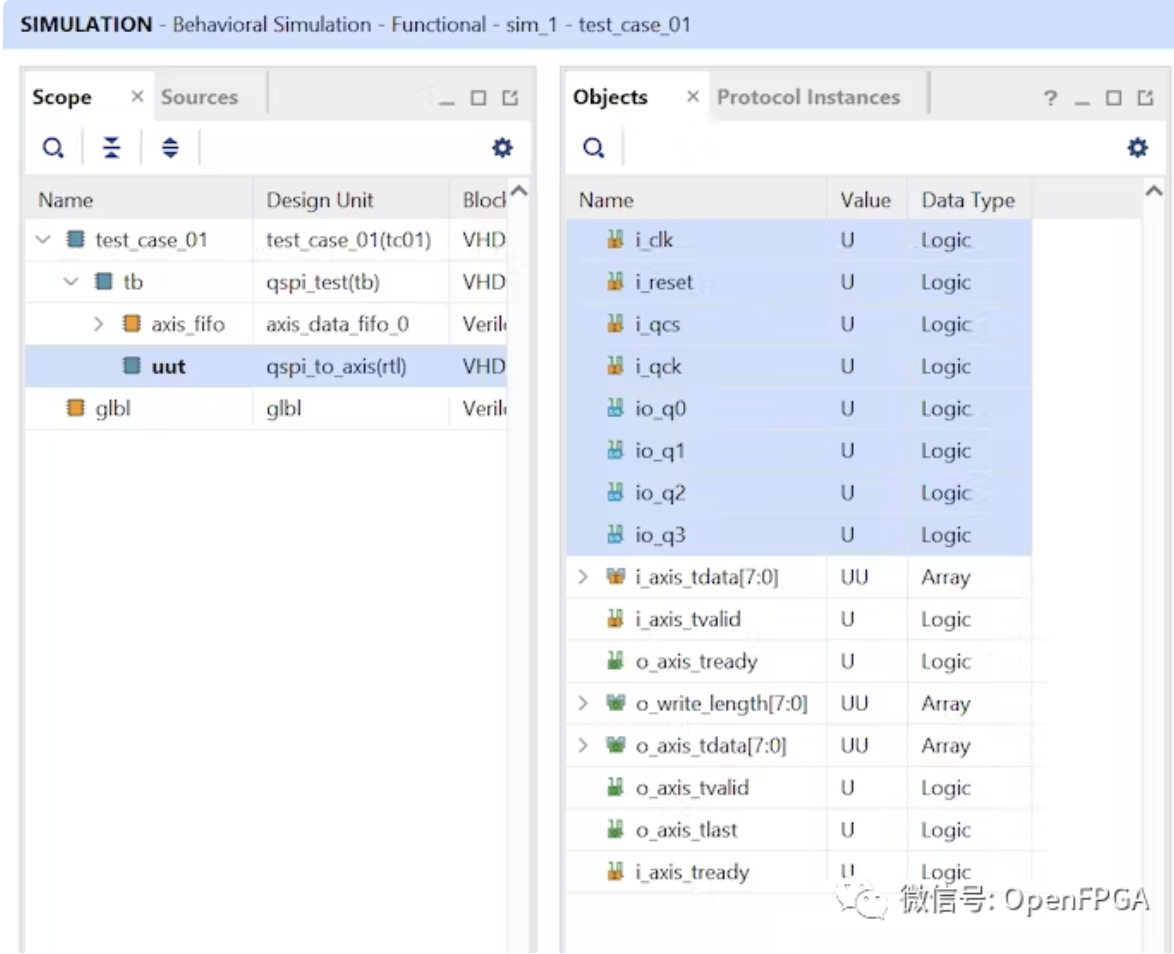

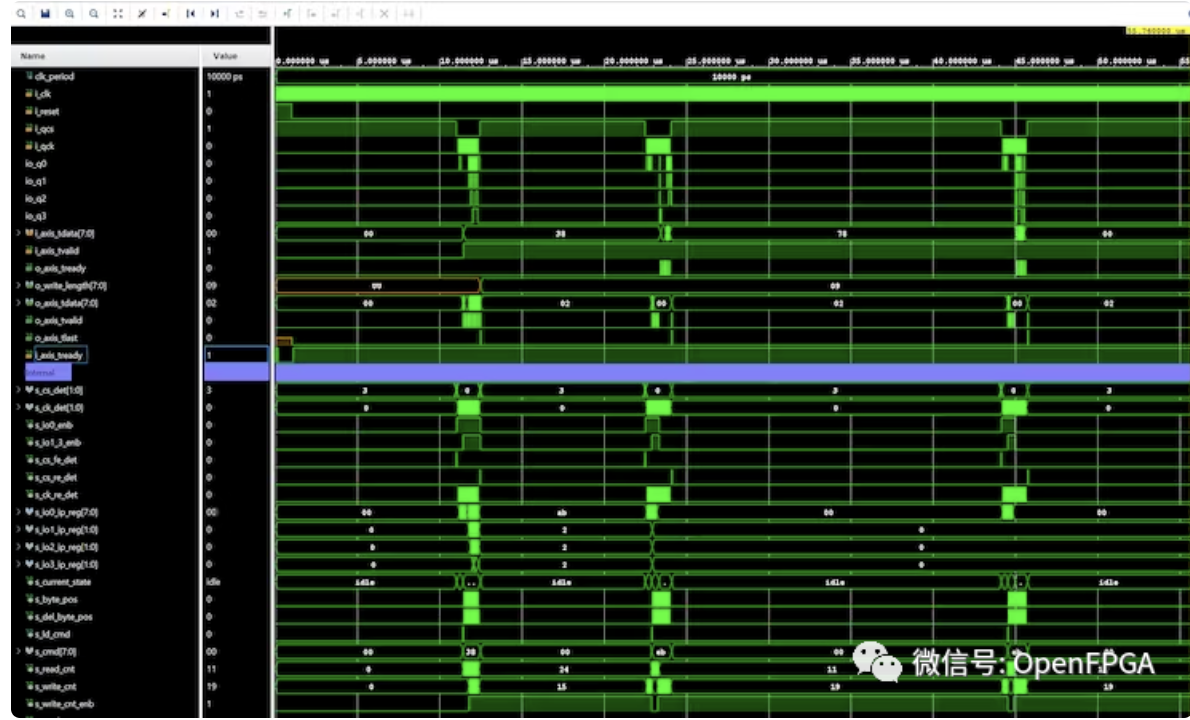

开发和验证 FPGA IP 不仅仅是编写 HDL,而是需要更多的思考。让我们来看看如何做吧!

2023-10-17 09:57:19 1911

1911

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 3688

3688

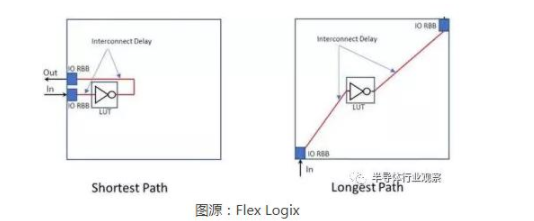

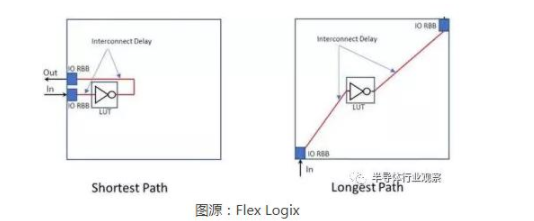

,工程师必须要解决空间、I/O延迟和带宽之类的问题。 而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA IP放入自己的定制IC产品内,无论是

2021-11-16 10:03:16 6423

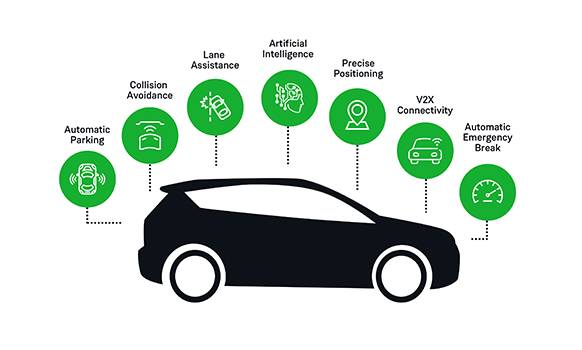

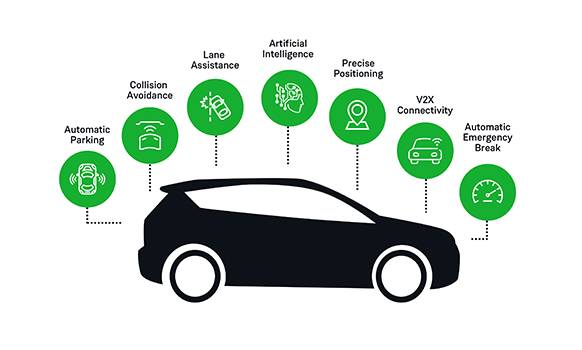

6423 汽车电气化和自动驾驶的一个主要方面是先进驾驶辅助系统(ADAS)的普及。如今,这些系统正迅速应用于市场上几乎所有的车辆,而且随着技术的成熟,这一趋势只会持续下去。然而,随着技术的发展,ADAS设计人员面临的硬件挑战变得越来越复杂。在本文中,我们将介绍ADAS的硬件需求,FPGA如何填

2023-04-26 15:20:24 1781

1781

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

容易就可以在某一个平台上升级IP特性,甚至根据需求,随时更换成其他协议的编解码功能。FPGA的可扩展性也是GPU不可比拟的,能非常容易的在同一块FPGA上pipeline部署编解码相关的上下游应用;同时

2019-03-08 10:47:22

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

有谁知道现在国内外有哪些公司卖FPGA的图像处理相关的IP核?

2015-04-28 21:34:24

FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块.pdf(1012.86 KB)

2019-04-24 13:33:04

FPGA详细教程_IP复用

2012-08-16 20:36:05

,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用。话不多说,上货。 IP

2023-03-15 16:19:35

多个蝶形处理器并行运算,能对较高的数据采样率进行运算,但其硬件规模较大,当在FPGA上要实现较大点数的FFT时较为困难。(2)串行方法,采用一个蝶形处理器完成运算,使用的逻辑资源较少,但运算速度较慢

2019-07-03 07:56:53

本帖最后由 eehome 于 2013-1-5 09:49 编辑

想自己做一个fpga的开发板,有谁有这方面经验的,拿出来分享一下!(有哪些外设)

2012-09-04 20:36:00

本帖最后由 elecfans跑堂 于 2015-9-2 13:43 编辑

最近,工作总算轻松了点,根据自己6年的FPGA产品研发经验,做了一块FPGA验证板,打样了20片,焊接了5片,各个功能

2015-09-02 11:33:41

ARM是应用,FPGA是芯片设计,前者是软件,后面是硬件,ARM就像单片机,但是它本身的资源是生产厂家固定了的,可以把它看成一个比较优秀的单片机来使用。而 FPGA 需要通过自己编程,让它具备一切你想让他具备的功能。比如,你想让它是一个计数器,或者...

2021-07-16 06:54:03

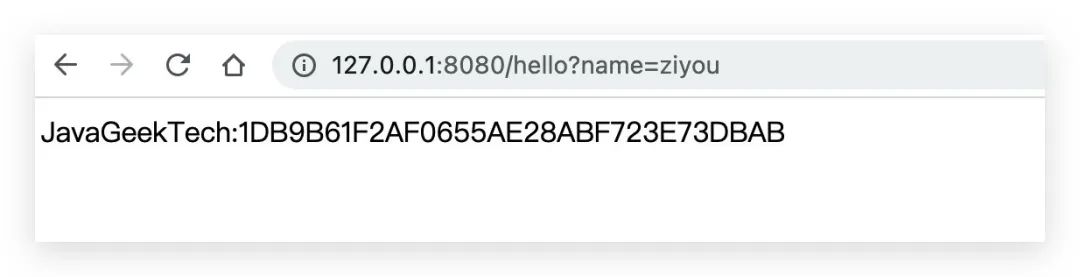

使用LabVIEW FPGA模块中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一个输入。我参考网上VHDL CORDIC IP核,说是将XY合并了,高位X低位Y。不知道在LabVIEW中如何将两个值X、Y合并成一个(X、Y均为定点数)。具体情况如下图:

2019-09-10 20:07:07

你好,我目前正在为我的Zynq 7020 FPGA做一个RTL引脚规划。我有一个非常基本的问题。我在PL EMI上的PS和AXI EMC v3.0 ip核心上只有很少的接口。在合成之前,我可以为此IP核进行引脚规划吗?另请告诉我针脚规划的整个步骤。

2020-04-10 10:21:22

通过Quartus II 软件创建PLL IP核。首先,要新建一个工程,这个方法在之前的帖子中已经发过,不会的可以查看前面的相关帖子。创建好自己的工程:打开如下的菜单

2016-09-23 21:44:10

为什么推出Virtex-5LXT FPGA平台和IP解决方案?如何打造一个适用于星形系统和网状系统的串行背板结构接口FPGA?

2021-04-29 06:18:31

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已经不足以担当这一新的角色。那么我们就需要弄明白,什么是IP开发及FPGA建模?

2019-08-01 07:41:01

在这段视频中,我们通过使用一个FPGA构建自己的GameBoy虚拟卡带,来破解GameBoy的卡带保护机制!

2023-09-26 07:13:16

Block RAMFPGA中的内存。在 Z-7010 FPGA上,有 120 个,每个都是 2KiB(实际上是 18 kb)。Latency延迟设计产生结果所需的时钟周期数。循环的延迟是一次迭代所需

2022-09-09 16:45:27

对于深入学习使用FPGA的小伙伴们,特别是一些复杂的、大规模的设计应用,适宜的IP核对开发能起到事半功倍的作用。IP核的概念与我们sdk里库的概念相似。IP即电路功能模块,用户可以直接调用这些模块

2024-04-29 21:01:16

关于全IP分体式干线微波你想知道的都在这

2021-05-24 06:26:44

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

飞舞,这里就不赘述了,以免有凑字数的嫌疑。下面我们就Matlab和FPGA两个工具双管齐下,比对Vivado的FFT IP核生成的数据。2 Matlab产生测试数据,绘制cos时域和频域波形

2019-08-10 14:30:03

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

是IDS/IPS中一个必不可少的操作。由于采用软件实现IP碎片重组的速度很低,很难达到高速接口的线速处理要求,所以在高速IDS/IPS上应采用硬件处理的机制。本文实现了一个基于Altera FPGA的IP

2008-10-07 11:00:19

如何自己设计一个基于RISC-V的SoC架构,最后可以在FPGA上跑起来

2025-11-11 08:03:32

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

什么是FPGA (现场可编程门阵列)?如何保护系统的关键功能和知识产权(IP)?

2019-08-26 08:25:51

训练一个神经网络并移植到Lattice FPGA上,通常需要开发人员既要懂软件又要懂数字电路设计,是个不容易的事。好在FPGA厂商为我们提供了许多工具和IP,我们可以在这些工具和IP的基础上做

2020-11-26 07:46:03

大神们求助啊,我是一只菜鸟~我有一个以太网转WIFI的嵌入式模块RM04,用网线一头连接模块的网口,一头连接FPGA的网口,模块会给FPGA分配IP地址,但是我该如何才能获知这个IP地址及与其对应

2014-10-29 16:03:59

怎么修改别人的fpga 51ip内核的代码配套自己的能用 我下的51内核的代码和我自己fpga的型号不匹配 不能用 ,然后修改后全是错误这怎么办

2013-08-03 09:50:06

设计。本人刚刚接触FPGA,对IP核的理解也是一知半解,是说比如我在verilog中,不能使用+,-,*,/,而必须自己亲自设计,只可以用& ,|,!,^这些运算是么?当然我知道IP核远远不止我提到的这些,但是最基本的+,-,/,*肯定都不可以使用是吧。谢谢大家了!

2018-04-06 20:46:11

基于FPGA 视频α 混合IP 的设计(合肥工业大学微电子设计研究所 485 信箱 邮编:230009)摘要:本文阐述了视频α 混合IP 的设计和实现方法。为了改善电路的性能, 在设计中不仅

2009-12-14 11:16:23 13

13 如何建立一个属于自己的AVR的RTOS

自从03 年以来,对单片机的RTOS 的学习和应用的热潮可谓一浪高过一浪.03 年,在离开校园前的,非典的那几个月,在华师的

2010-03-11 09:02:16 45

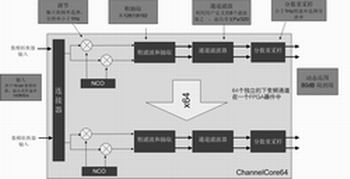

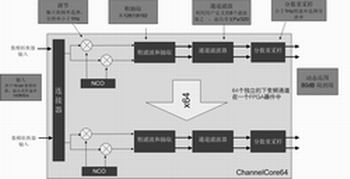

45 使用一个FPGA便可实现的64通道下变频器

RF Engines公司的ChannelCore64使设计者能够用一个可对FPGA编程的IP核来替代多达16个DDC(直接下变频器)ASIC,可显著减少PCB面积

2010-01-18 16:34:34 1451

1451

通过将第三方IP集成到NI LABVIEW软件中,您可以使用许多为XILINX现场可编程门阵列(FPGA)精调过的算法实现高性能,并且提高代码重用度。LABVIEW FPGA模块为导入外部IP提供了两个方法:组件级知识产权(CLIP)节点和结合XILINX核心生成器的IP集成节点。本技

2011-03-15 13:25:58 98

98 本文侧重于介绍IP 模块中组件控制器的设计和实现。一个基于FPGA 的LCD 控制器设计作为例子被介绍。这个组件控制器设计属于固核IP 设计,也就是软硬结合的方法。设计内容主要包括电

2011-12-22 14:00:11 1634

1634

基于FPGA的SD卡控制器IP,以验证可用。

2015-11-06 09:50:50 10

10 This is a VHDL implementation of a UDP/IP core that can be connected to the input and output ports

2015-11-12 14:45:16 8

8 FPGA中IP核的生成,简单介绍Quartus II生成IP核的基本操作,简单实用挺不错的资料

2015-11-30 17:36:15 12

12 FPGA的IP核设计技术的系列资料,大家可以收集看下,这些都是我看过过滤后留下的,感觉不错,希望对大家有帮助

2015-11-30 17:49:01 6

6 利用FPGA的IP核设计和实现FFT算法

2016-05-24 14:14:47 37

37 引入IP核的三维FPGA结构研

2017-01-07 20:32:20 2

2 的代名词了。想想当时有心学FPGA还是因为学长对FPGA神乎其神的夸赞,当然现实也是这样,FPGA确实非常强大,他说“FPGA就是堆积木,你可以建造你想要建造的任何房子”,当时觉得这样的描述表明FPGA肯定相当的高端,而且FPGA还没有一个比较朗朗上

2017-02-09 06:43:11 356

356 如何在EDK中使用自己的 IP核呢? 这是很多人梦寐以求的事情。然而在EDK以及ISE的各种文档中对此却遮遮掩掩,欲语还休。

2017-02-11 13:35:11 2452

2452 一个合格的FPGA工程师需要掌握哪些知识?这里根据自己的一些心得总结一下,其他朋友可以补充啊。

2017-02-11 13:47:12 5448

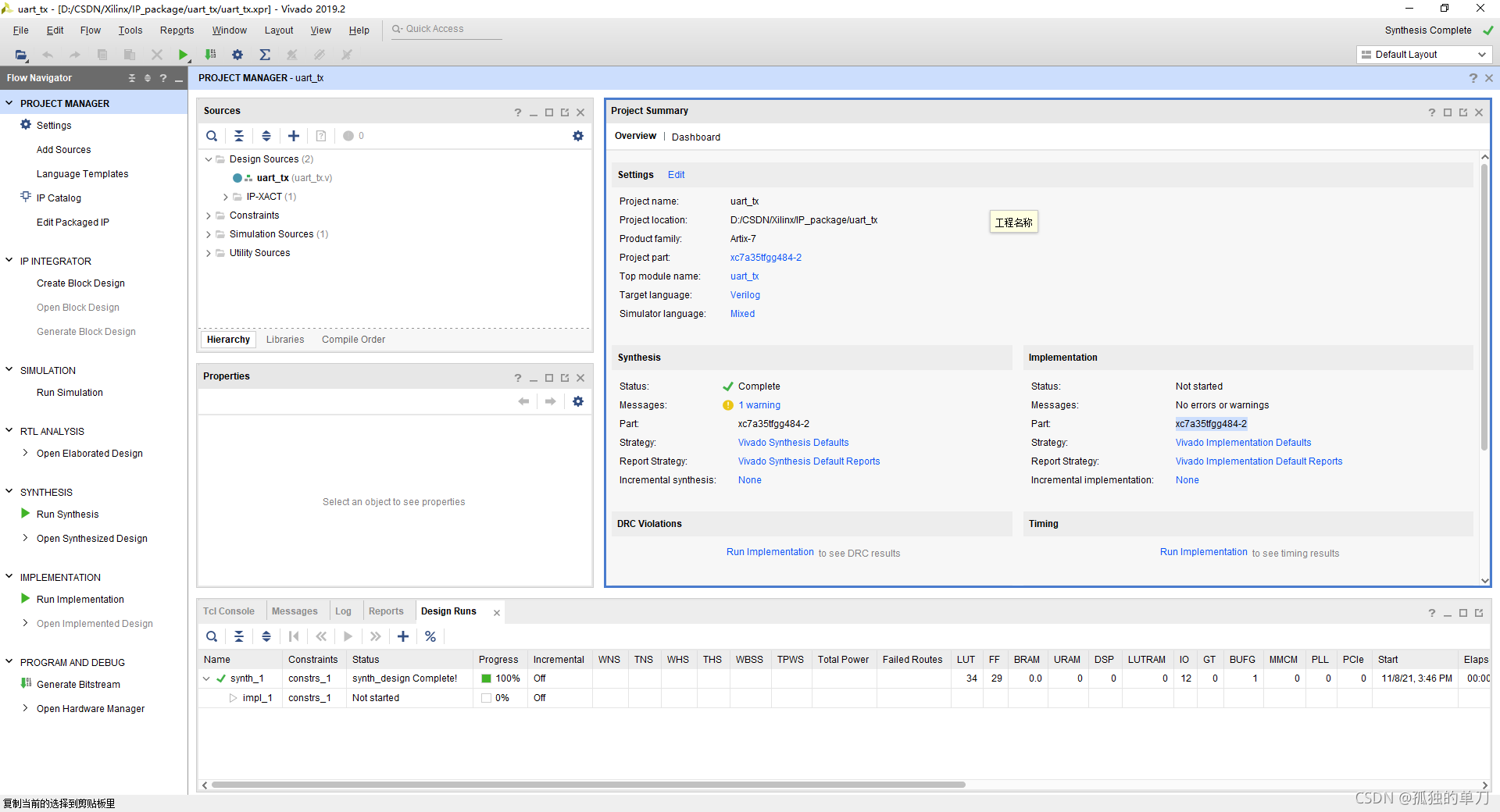

5448 有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 16

16 编译FPGA VI至FPGA应用前必须创建一个程序生成规范。

2017-11-18 02:46:52 971

971 LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI

2017-11-18 05:56:22 2433

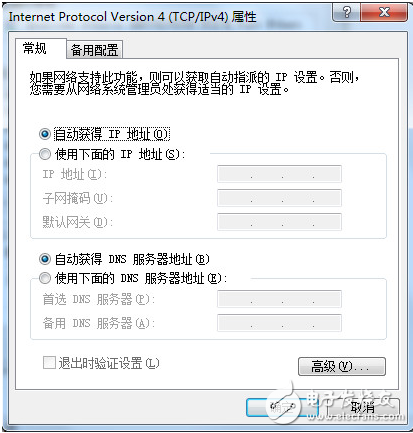

2433 P地址是IP协议提供的一种统一的地址格式,互联网上的每一个网络和每一台电脑都有一个逻辑地址,说的通俗一点IP地址就是给互联网上的电脑进行编号,那么如何要查询自己的IP地址呢?今天小编给大家介绍通过DOS命令查看本地IP的方法。

2018-01-17 15:50:21 13220

13220

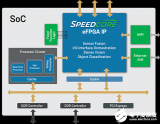

嵌入式FPGA(eFPGA)是指将一个或多个FPGA以IP的形式嵌入ASIC,ASSP或SoC等芯片中。

2018-06-29 15:03:00 2619

2619

本文档内容介绍了建立用户自己的IP核的操作步骤,供参考

2018-04-03 11:26:51 4

4 最近,我接手一个项目,这个项目不仅要求我使用FPGA,而且还要求我使用功能更强大的ARM。这都是我从未接触过的领域。在这个系列博客中,我将介绍我是如何将自己现有的MCU知识和经验运用到FPGA中

2018-05-08 15:41:00 4247

4247 在过去两年间快速增长,2017年,已经占到Achronix FPGA整体营收的20%,而2018年,凭借其显着的功耗和成本优势,eFPGA IP授权业务比重进一步

2018-12-23 16:29:40 5164

5164 本文档的主要内容详细介绍的是FPGA视频教程之怎样开始一个简单的FPGA设计。

2019-03-20 14:35:37 8

8 复旦大学微电子学院某国家重点实验室内部教学视频:基于ZYNQ FPGA与PC的IP设计与验证方案。

关键词:IP设计,IP验证,AXI总线协议,ARM,UDP传输,PYTHON

2019-08-06 06:16:00 2714

2714

IP地址是每一个连接到网络中的设备都需要的一个逻辑性的地址,正常情况下,两个设备连接普通的命令并无法获得对端的IP地址,如果我们连接的是一个未知IP的摄像头,那么应该怎么办?

2020-02-15 13:08:08 10680

10680

在产品交付方面,Socionext将提供用于IP测试的FPGA评估板、启动手册和Linux开源驱动程序,帮助用户快速评估和开发。Socionext在工业ASIC开发领域拥有丰厚的设计开发经验,公司期望通过提供IP组合,助力客户开发设计属于他们自己的ASIC芯片。

2020-04-27 16:27:43 3490

3490 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270 FPGA是有门槛的,零基础并不是你想的那样,而且门槛不低的! 本篇给非电子类专业或者非技术行出身想要转行FPGA的大侠们,做个参考,各位大侠可根据自己情况,自行避坑。 本人FPGA百度贴吧吧主

2020-11-20 09:58:27 3052

3052 本文接续上一篇《FPGA杂记基础篇》,继续为大家分享IP例化和几个基于FPGA芯片实现的Demo工程。IP例化IP即是一个封装好的模块,集成在相应的开发环境里面,以安路的TD软件为例,不同系列的芯片集成了不同的IP模块,可以通过软件例化调用

2020-12-24 12:58:51 1803

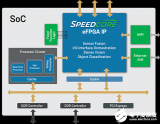

1803 Achronix Speedcore eFPGA IP使客户公司能够将FPGA功能集成到其ASIC或SoC器件中。 Speedcore eFPGA具有可变换的架构,它可让客户根据需求去定义eFPGA IP的FPGA逻辑阵列、存储器和DSP处理能力。

2021-03-26 10:18:54 2333

2333 基于FPGA的TCP/IP协议的实现说明。

2021-04-28 11:19:47 54

54 Q1 一个synplify综合得到的.edf,和vivado生成的RAM IP,(synplify综合的RTL代码里,使用RAM IP的地方注明了blackbox) 希望能用一个vivado工程把

2021-06-18 10:21:01 3485

3485

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核,可实现重复利用,避免重复造轮子,大幅提高我们的开发效率。

2022-02-16 16:21:28 3653

3653

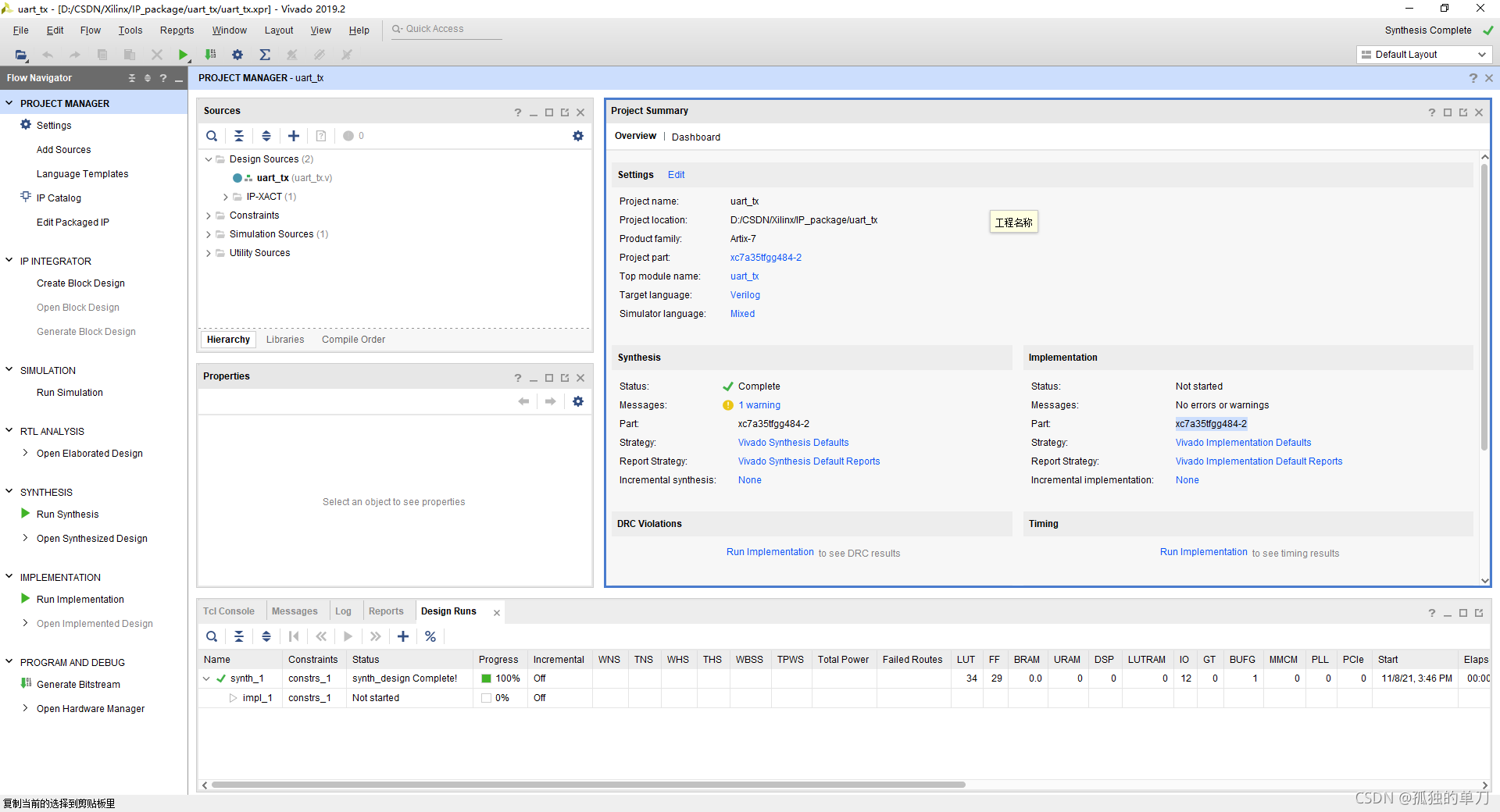

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

2022-04-21 08:58:05 7941

7941 ARTIX-xlinx 版本FPGA 串口通信模块(含IP核)

2022-06-20 11:07:28 16

16 电子发烧友网站提供《Gowin SecureFPGA IP用户指南.pdf》资料免费下载

2022-09-20 17:11:45 2

2 这里面最重要的是发送端和接收端的IP地址。这个IP地址就像是一个门牌号一样,有了它,数据包就能在这个纷繁复杂的网络世界里找到该由谁来接收这个数据包。

2022-11-04 14:21:15 1794

1794 本人是一个纯FPGA小白,就连FPGA这个名词我都是最近才知道,所以如果你也正想入门学习FPGA的话,请耐心看下去吧,相信你看完绝对不会后悔。

2022-12-15 11:06:44 2536

2536 Opencores是一个开源的数字电路设计社区,它提供了免费的开源IP(知识产权)核心,让工程师和爱好者们可以使用这些IP核心来构建自己的数字电路设计。Opencores的IP核心包括处理器、总线接口、视频、音频和其他数字电路组件

2023-04-03 10:39:53 2585

2585 FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 8969

8969 了解eFPGA IP的基础知识,它的优点,以及为什么它将成为未来先进驾驶辅助系统(ADAS)技术的关键要素。

2023-07-10 10:26:38 937

937

一个好的产品,必须不断地改进,不断地否定自己,不断地革命,不断地优化自己,才能做到最好。以国产易灵思的FPGA工具链:Efinity为例,Elitestek(易灵思)公司几乎每个月,甚至每周都在更新自己的软件,他也许可以磨出一个好的产品。

2023-07-12 00:26:30 1170

1170

其实用FPGA做的示波器有很多,开源的相对较少,我们今天就简单介绍一个使用FPGA做的开源示波器:

2023-08-14 09:03:18 1701

1701 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数

2023-09-07 18:31:35 3352

3352

要实现一个域名对应多个 IP 地址的效果,只需要在 DNS 解析操作平台,添加一条解析记录,将网站的域名指向服务器的 IP 地址。一般情况下,一个域名对应一个 IP 地址,也就只需添加一条解析记录即可。

2023-09-19 17:05:19 1846

1846

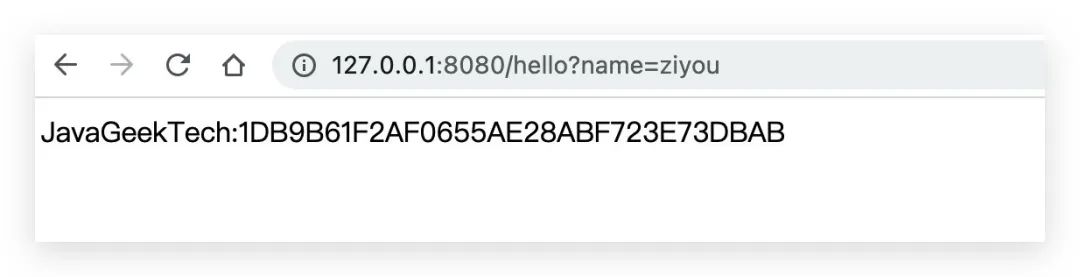

前面给大家介绍了 SpringBoot 的自动装配功能,相信大家对自动装配都有了很好的理解,那么今天阿粉通过一个示例来给大家演示一下如何编写一个自己的 starter 。 再编写 starter

2023-10-08 14:42:19 1625

1625

核心CPU是XX32FXXX,在工业控制领域其实FPGA占比也很大,所以能不能用FPGA做一个ODrive呢?答案是肯定的。

2023-10-20 11:15:27 1885

1885

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 如何自己搭建一个服务器?自己搭建一个服务器涉及到硬件和软件两个方面。下面是一个简单的指南,涵盖了基本的步骤。请注意,这是一个概述,实际步骤可能因你的需求和硬件选择而有所不同。

2023-12-12 16:52:09 5718

5718 从零到一搭建属于自己的海外IP代理池是一个复杂但具有挑战性的任务,它涉及多个步骤和考虑因素。

2024-11-15 08:15:56 1834

1834 /prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。 为此,很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法。

2025-01-15 10:47:37 1246

1246

上一期小编给大家介绍了和MediaPipe的相遇之路,本期小编将带着大家一起来动手,如何打造一个属于自己的手势识别应用。

2025-07-29 10:12:14 1029

1029

电子发烧友App

电子发烧友App

评论