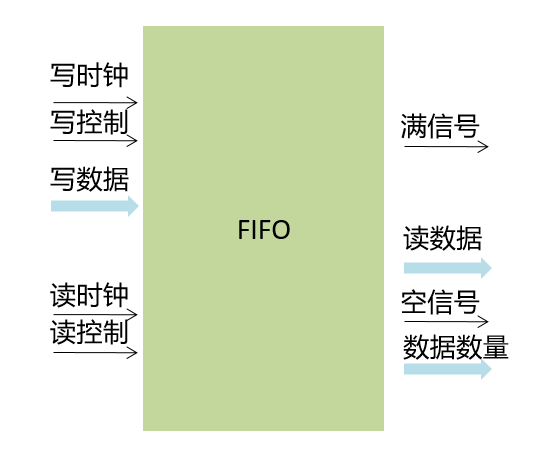

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

首先了解一下FIFO读写位宽不一致时数据的摆放方式:

读数据位宽是写数据位宽的4倍的情况下的写如何读出数据摆放方式如下:

写数据位宽是读数据位宽的4倍的情况下的写如何读出数据摆放方式如下:

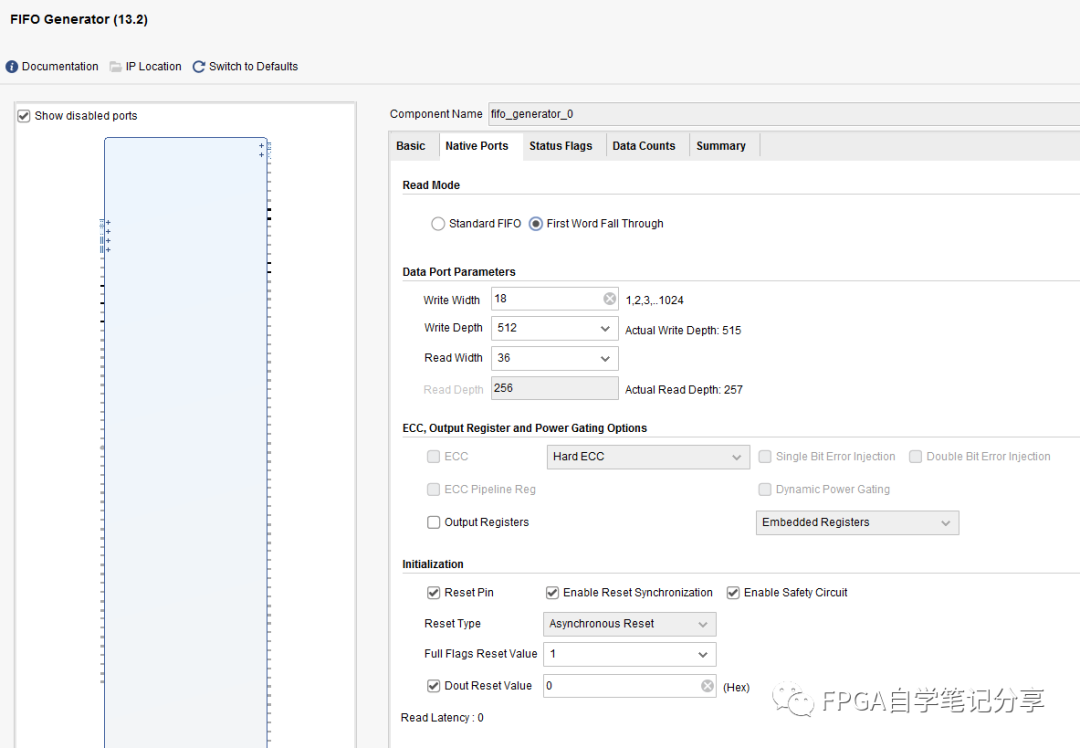

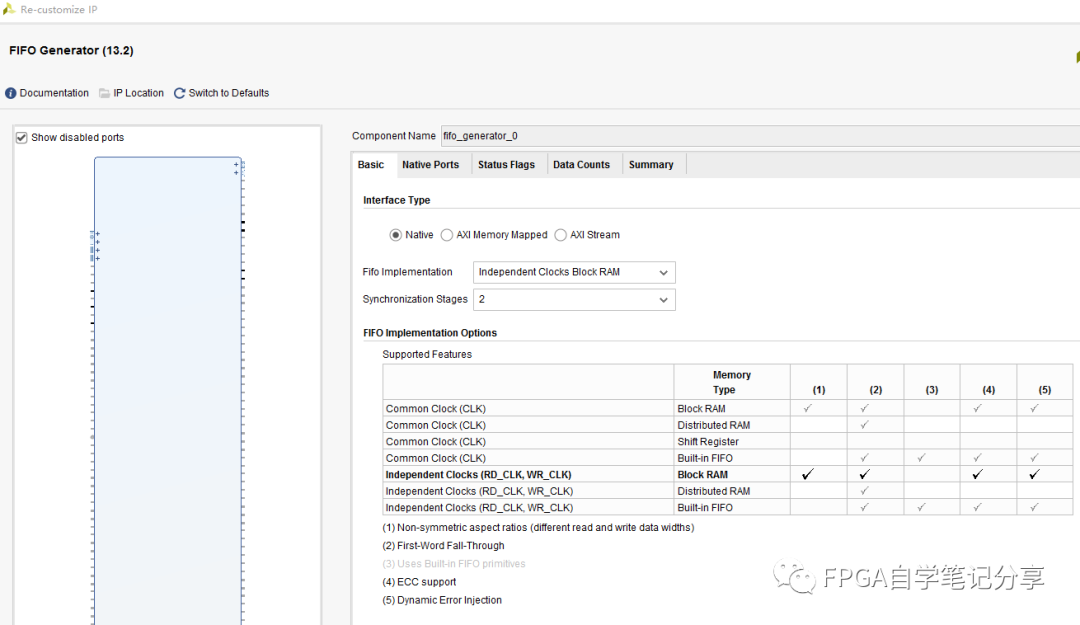

然后,开始例化IP,生成一个FIFO,使用BRAM搭建,两个独立时钟:

写位宽18bit,读位宽36bit,读写数据位宽比为1:2.

例化的总结为:

例化的端口为:

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

fifo_generator_0 your_instance_name (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [17 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [35 : 0] dout

.full(full), // output wire full

.almost_full(almost_full), // output wire almost_full

.empty(empty), // output wire empty

.almost_empty(almost_empty), // output wire almost_empty

.rd_data_count(rd_data_count), // output wire [7 : 0] rd_data_count

.wr_data_count(wr_data_count), // output wire [8 : 0] wr_data_count

.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy

.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);

根据这个端口,编写tb,如下。设置读写时钟频率比为2:3。写侧:复位释放后,即拉高写使能,写入自加数,直到1000后停止写入。读侧:只要非空就开始一直读取数据。

// ============================================================

// File Name: tb_fifo_generator

// VERSION : V1.0

// DATA : 2023/7/23

// Author : FPGA干货分享

// ============================================================

// 功能:xilinx fifo_generator ip 代码仿真

// delay :

// ============================================================

`timescale 1ns/100ps

module tb_fifo_generator ;

reg rst ='d1 ;

reg wr_clk ='d1 ;

reg rd_clk ='d1 ;

reg [17 : 0] din ='d1 ;

reg wr_en ='d0 ;

reg rd_en ='d0 ;

wire [35 : 0] dout ;

wire full ;

wire almost_full ;

wire empty ;

wire almost_empty ;

wire [7 : 0] rd_data_count ;

wire [8 : 0] wr_data_count ;

wire wr_rst_busy ;

wire rd_rst_busy ;

initial

begin

rst = 1'b1;

#1000;

rst = 1'b0;

end

always #2 wr_clk = ~wr_clk;

always #3 rd_clk = ~rd_clk;

// ==================wr_clk======================//

always @(posedge wr_clk )

if(din >= 'd1000)

wr_en <= 1'b0;

else if(~wr_rst_busy&&~rst)

wr_en <= 1'b1;

else

wr_en <= 1'b0;

always @(posedge wr_clk)

if(wr_en)

din <= din + 1'b1;

else

din <= din;

// ==================rd_clk======================//

always @(posedge rd_clk)

rd_en <= (!empty)&&(!rd_rst_busy);

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

fifo_generator_0 fifo_generator_0 (

.rst (rst ), // input wire rst

.wr_clk (wr_clk ), // input wire wr_clk

.rd_clk (rd_clk ), // input wire rd_clk

.din (din ), // input wire [17 : 0] din

.wr_en (wr_en ), // input wire wr_en

.rd_en (rd_en ), // input wire rd_en

.dout (dout ), // output wire [35 : 0] dout

.full (full ), // output wire full

.almost_full (almost_full ), // output wire almost_full

.empty (empty ), // output wire empty

.almost_empty (almost_empty ), // output wire almost_empty

.rd_data_count (rd_data_count ), // output wire [7 : 0] rd_data_count

.wr_data_count (wr_data_count ), // output wire [8 : 0] wr_data_count

.wr_rst_busy (wr_rst_busy ), // output wire wr_rst_busy

.rd_rst_busy (rd_rst_busy ) // output wire rd_rst_busy

);

endmodule

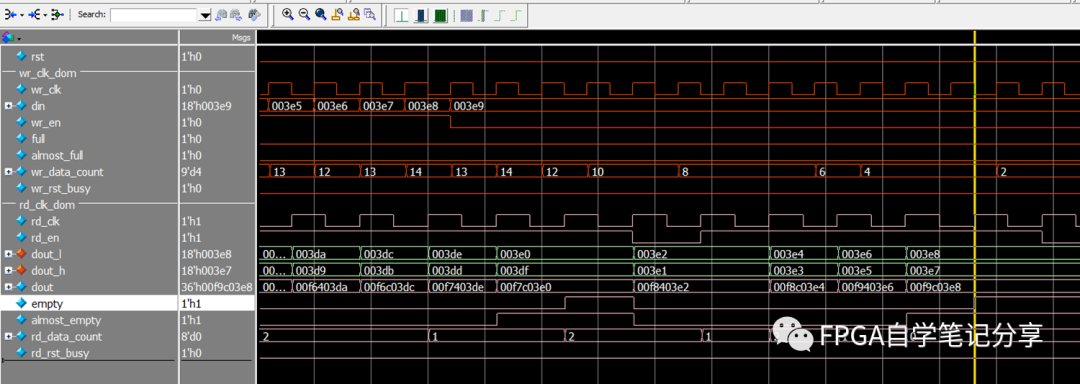

仿真结果如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21320浏览量

593195 -

Xilinx

+关注

关注

70文章

2121浏览量

119373 -

仿真

+关注

关注

50文章

3872浏览量

132161 -

fifo

+关注

关注

3文章

369浏览量

43069 -

时钟域

+关注

关注

0文章

49浏览量

9455

发布评论请先 登录

相关推荐

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析

`Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

发表于 12-09 12:22

Xilinx FPGA入门连载51:FPGA片内FIFO实例之功能概述

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察

发表于 02-26 10:26

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套

发表于 02-29 13:35

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套

发表于 02-29 13:35

Xilinx FPGA入门连载55:FPGA 片内异步FIFO实例之功能概述

概述该工程实例内部系统功能框图如图所示。我们通过IP核例化一个异步FIFO,这个FIFO的读写时钟频率不同,并且读写位宽也不同。定时对这个异

发表于 03-07 11:32

Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置

`Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置特权同学,版权所

发表于 03-09 10:49

Xilinx FPGA入门连载59:FPGA 片内ROM FIFO RAM联合实例之功能概述

模块划分本实例工程模块层次如图所示。●Pll_controller.v模块产生FPGA内部所需时钟信号。●onchip_mem_test.v模块例化FPGA片内ROM、

发表于 03-16 12:43

【正点原子FPGA连载】第十三章IP核之FIFO实验-领航者ZYNQ之FPGA开发指南

图所示。图 13.4.12 “fifo_generator _0_synth_1”run在其Out-of-Context综合的过程中,我们就可以进行RTL编码了。首先打开IP核的例化模

发表于 09-23 17:27

IP CORE 之 FIFO 设计- ISE 操作工具

不多说,上货。IP CORE 之 FIFO 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的

发表于 04-11 20:50

XILINX FPGA IP之FIFO Generator例化仿真

XILINX FPGA IP之FIFO Generator例化仿真

评论