写在前面

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核,可实现重复利用,避免重复造轮子,大幅提高我们的开发效率。

接下来将之前设计的串口接收模块和串口发送模块打包成IP核,再分别调用这两个IP核,构成串口接收--发送循回,依次验证IP核打包及调用是否成功。

源码在这:串口(UART)的FPGA实现

Vivado版本:Vivado 2019.2

开发板:xc7a35tfgg484-2

打包

打包串口发送模块uart_tx

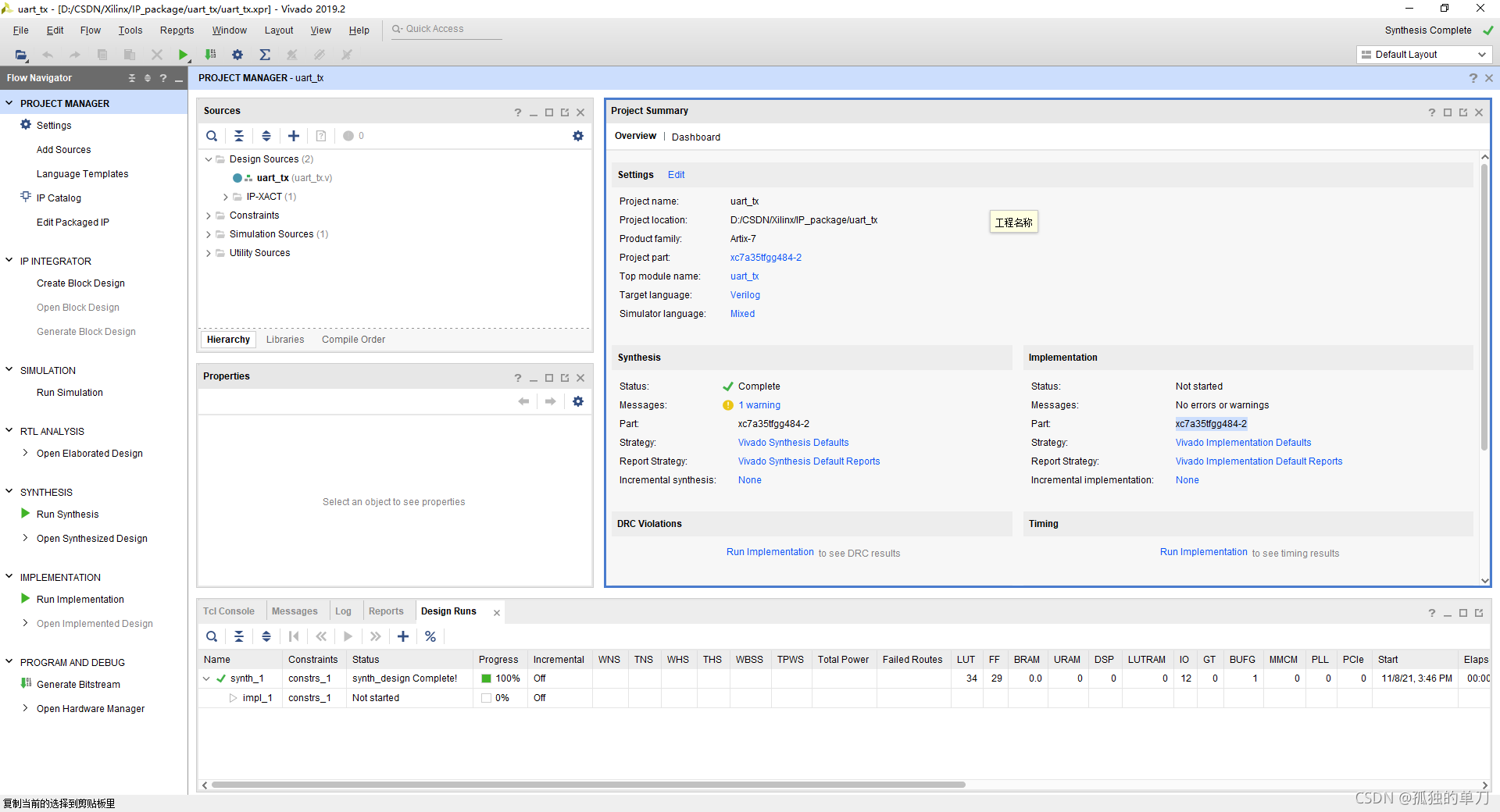

1、首先打开发送模块的VIVADO工程,确保其编译无误(最好进行仿真验证、上板验证保证其功能正确性),如下:

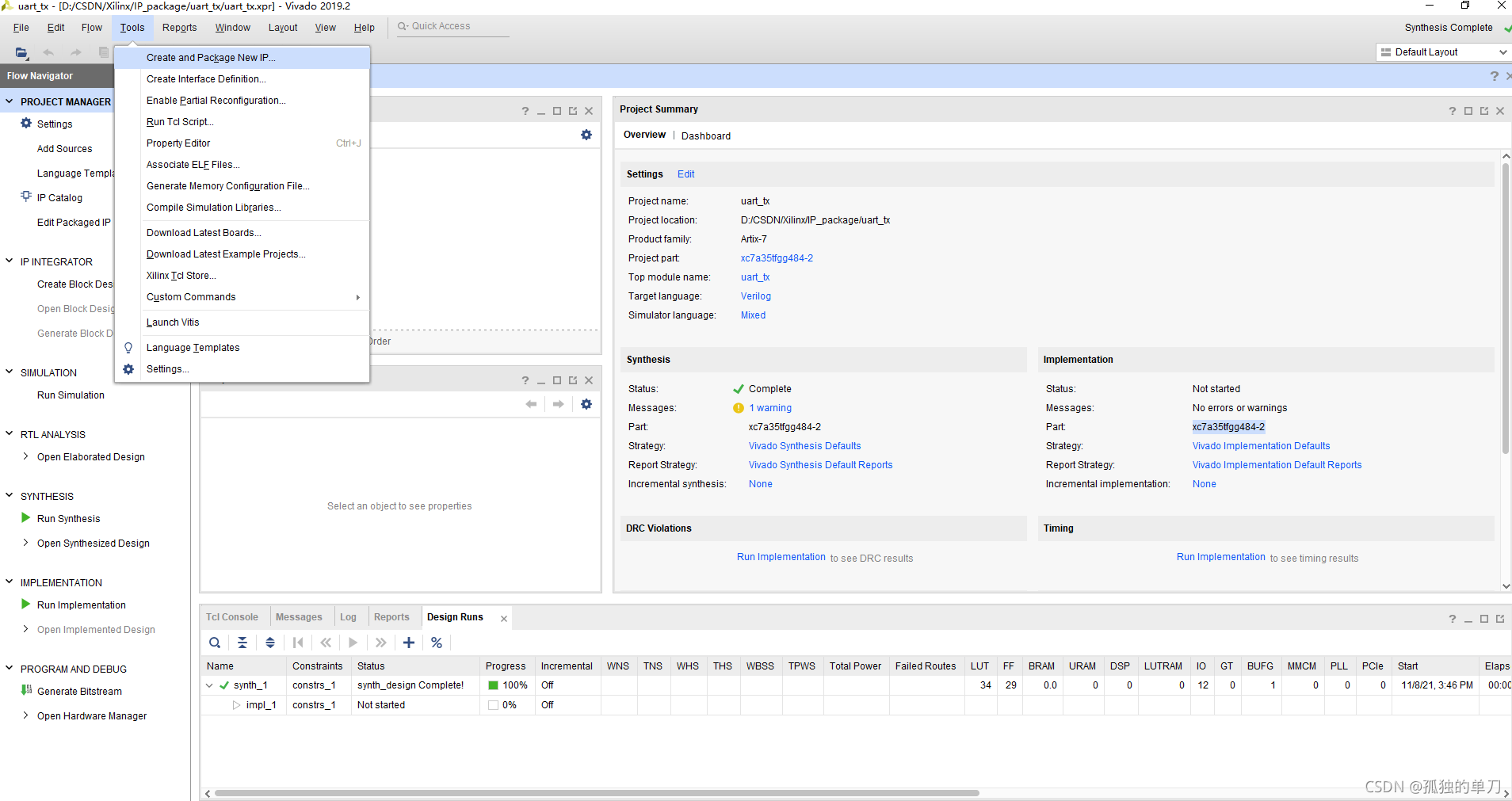

2、点击Tools-----create and package new ip

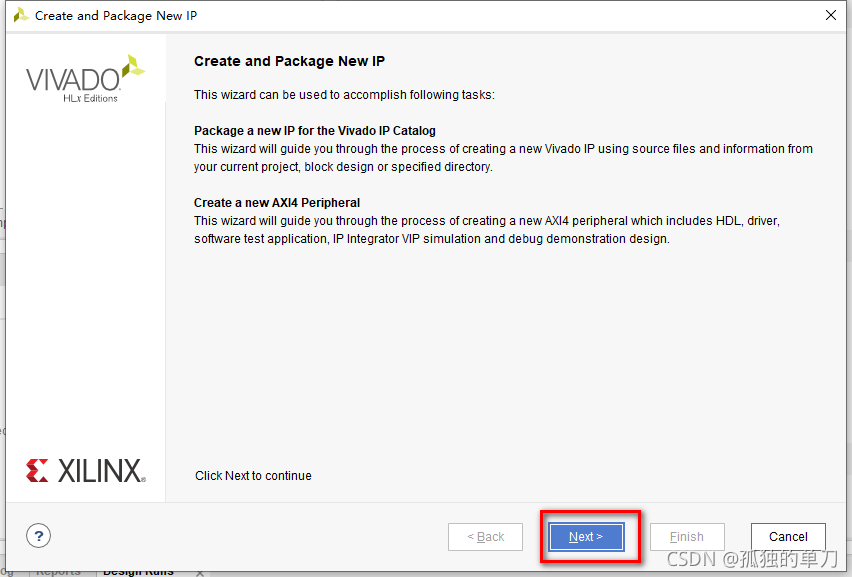

3、点击Next

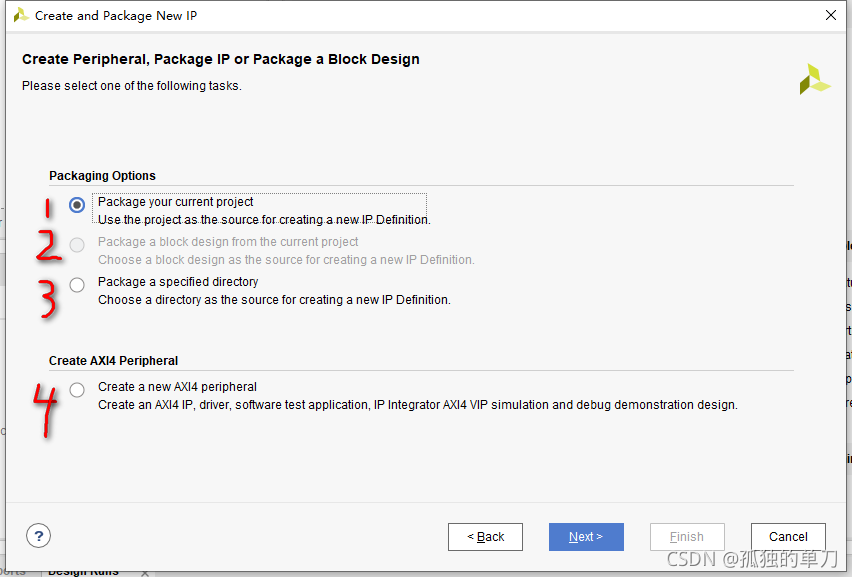

4、选择选项1,点击Next,各选项含义:

1---将当前工程打包为IP核

2----将当前工程的模块设计打包为IP核

3----将一个特定的文件夹目录打包为IP核

4----创建一个带AXI接口的IP核

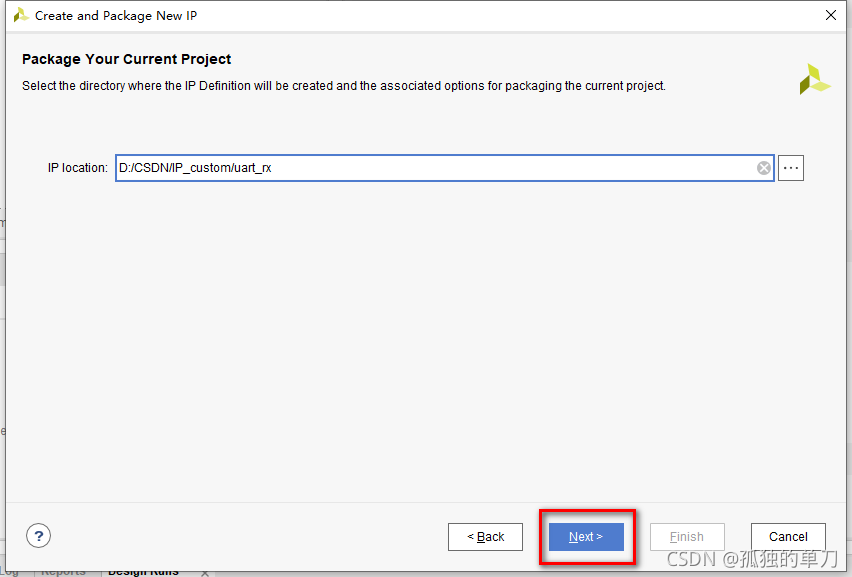

5、选择IP存放路径,建议专门建一个文件夹来管理所有建立的IP核,然后点击Next

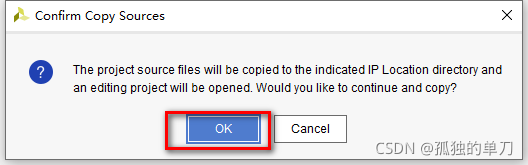

6、点击OK,然后点击NEXT,会自动创建一个新工程,用来生成IP核

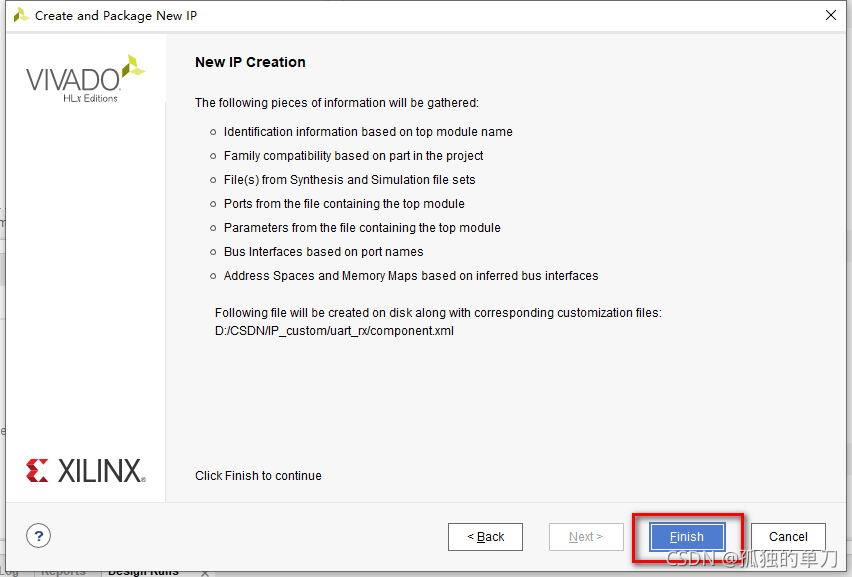

7、新生成的IP核打包工程如下:

在右边的界面可以配置一系列参数:

Identification:主要是一系列信息,如IP名字,开发者、版本号等。因为本文仅作示范,所以我这边所有信息都没改

compatibility:兼容的系列,这里根据自己需求添加所需要的系列芯片就好了。我这边保持默认

file groups:IP核的文件架构,可以添加或删除文件。比如添加仿真文件、例化文件,说明文件等。我这边保持默认

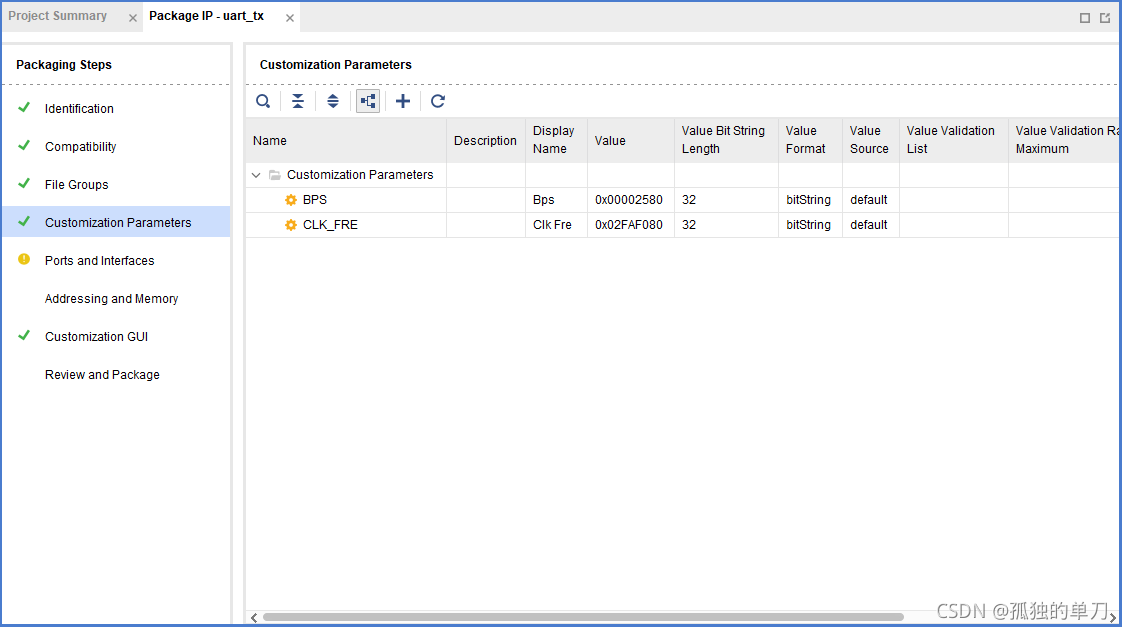

Customization Parameters:定制化参数。可对参数进行自己的配置,如参数名称啊,类型啊,自定义区间,可选列表等。

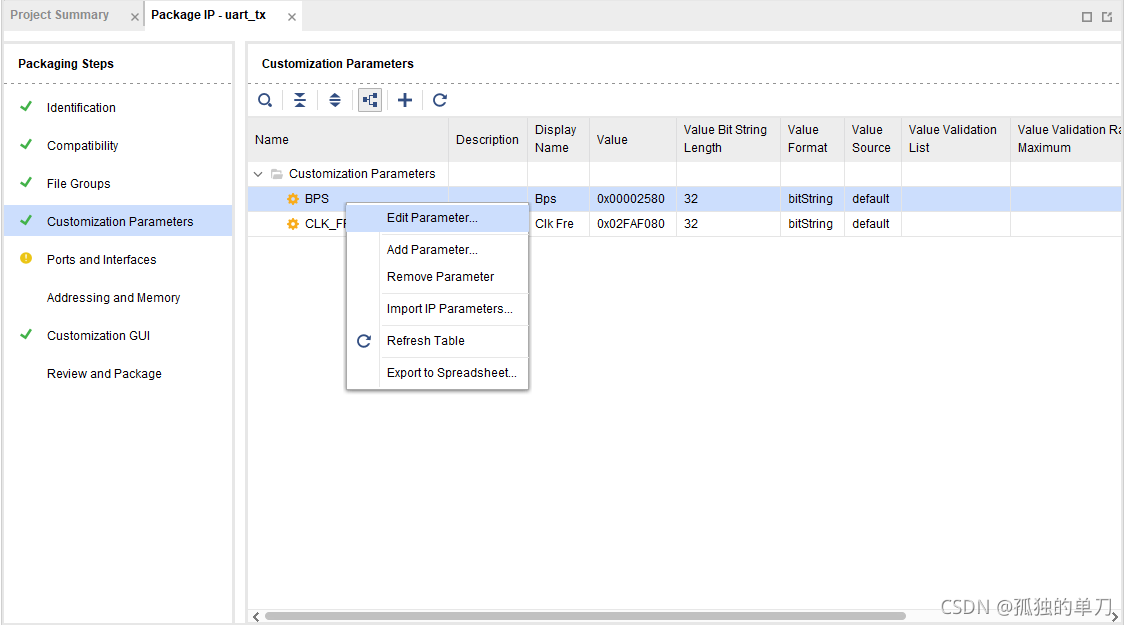

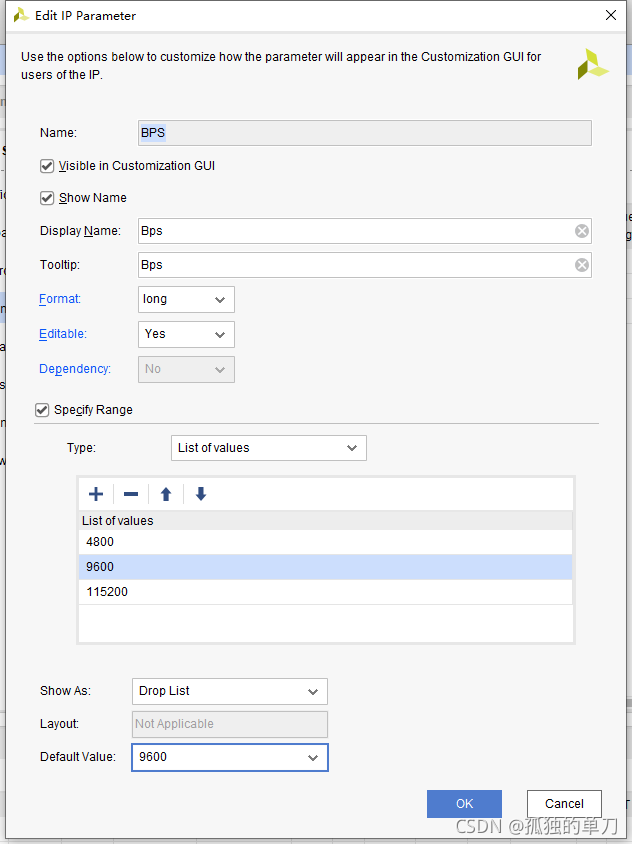

点击BPS----edit parameter,对参数进行配置(该参数为串口模块的波特率)

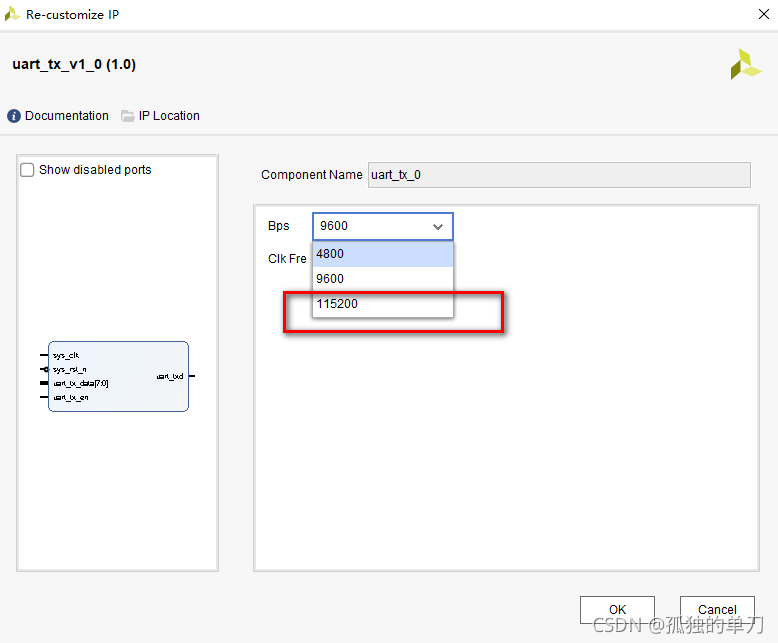

将格式Format改为long类型,再勾上Specify Range,Type改成List of values,再添加3个参数(仅作示范)--4800、9600、115200。再将默认值Default value改为9600。这样就将该参数配置成了可选参数,默认9600,可选值:4800、9600、115200。

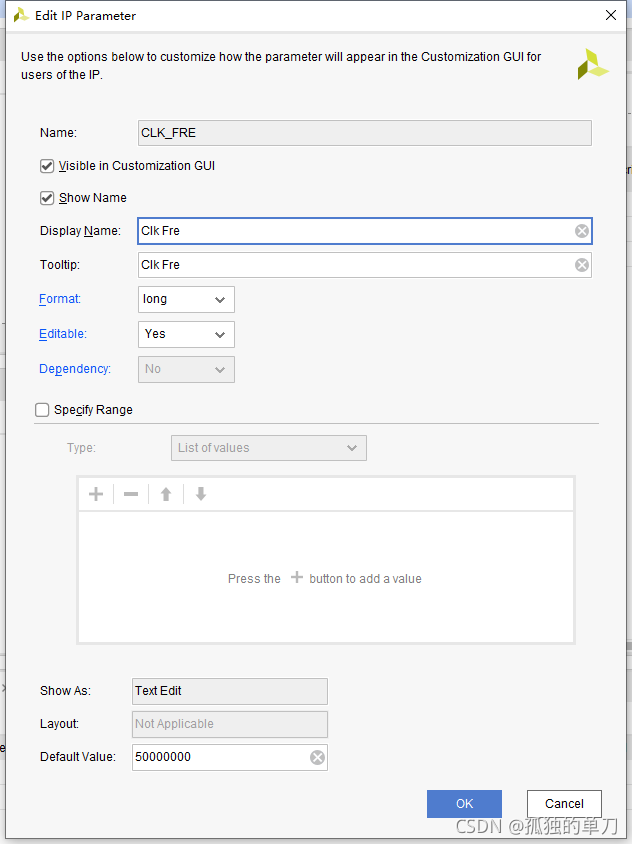

再使用同样的方法将参数CLK_FRE(模块时钟频率)改为long类型,默认50000000.

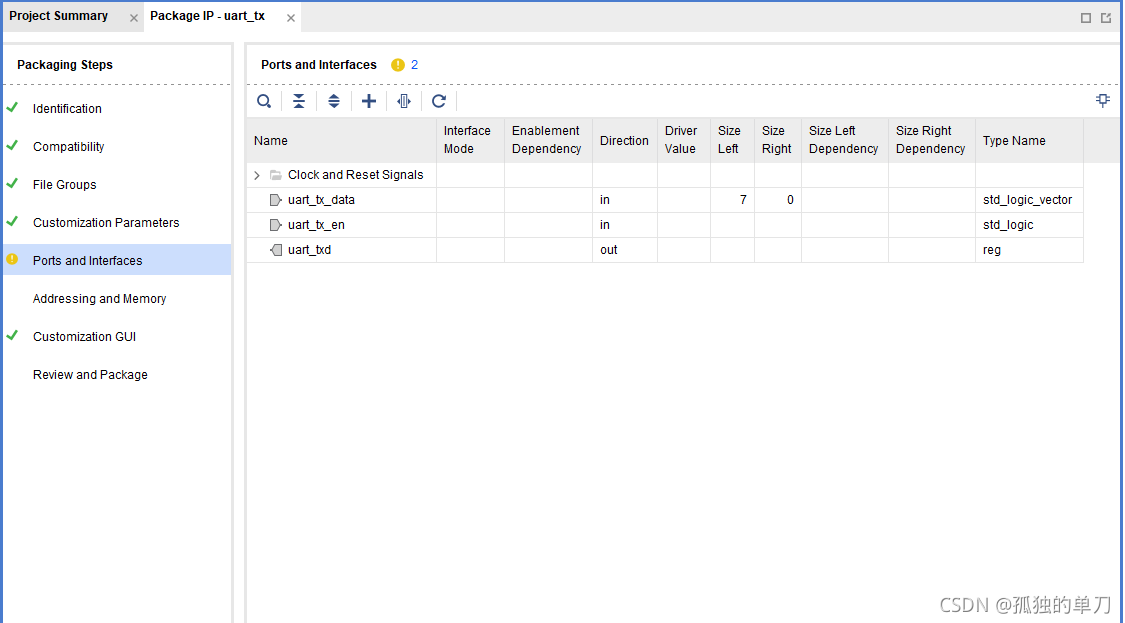

Ports and Interfaces:这里展示了IP的接口,可根据需求添加、删除接口或者总线。

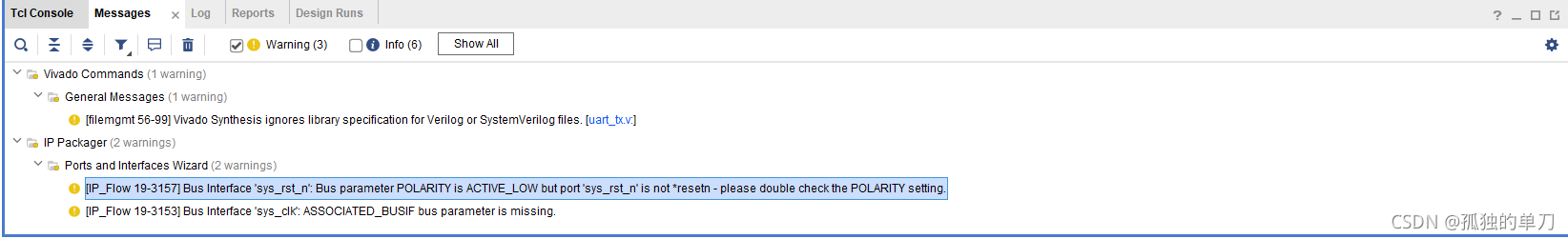

需要说明的是,这里很容易报警告:

这个警告是因为IP核打包器在设计中推断出了时钟端口或是复位端口。例如:如果信号名称包含以下任何一种:[ ]clk,[ ]clkin, [ ]clock[ ], [ ]aclk 或 [ ]aclkin,那么IP打包器就会为将其判断成为时钟接口。被自动判断出的接口,IP打包器会倾向于认为你使用AXI接口来处理这个信号,因为IP打包器工具主要是针对于AXI接口。所以如果你的IP中并不使用AXI总线,这两条警告可以直接忽略,在实际的IP中不会有任何的影响。

Addressing and Memory:地址分配和储存映射。本设计用不到,直接跳过,感兴趣的可以看XILINX的手册UG1118。

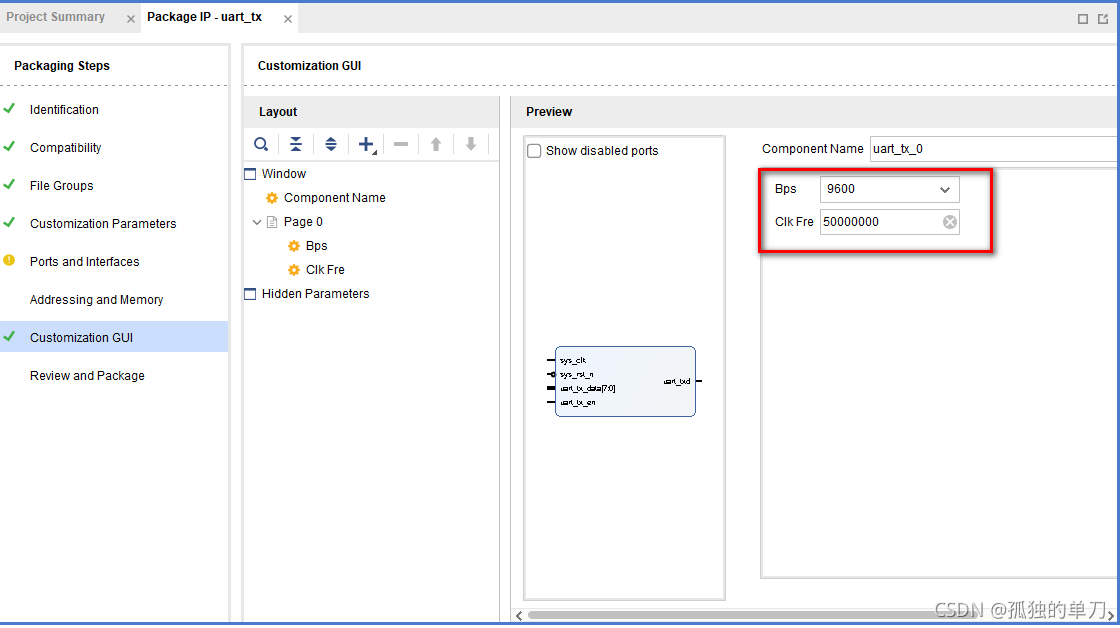

Customization GUI:参数设置的GUI界面。可以对以后配置IP核的界面做一个修改。可以看到,红框内的参数都是我设置好的默认值。

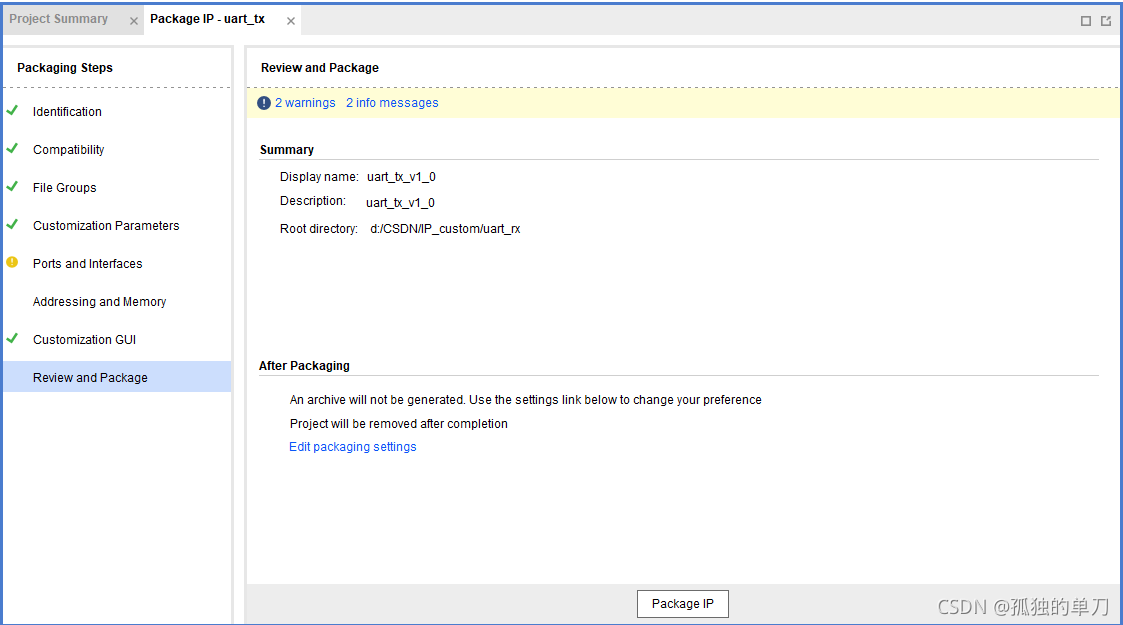

Review and Package:IP核总览及生成界面。点击Package IP完成IP打包

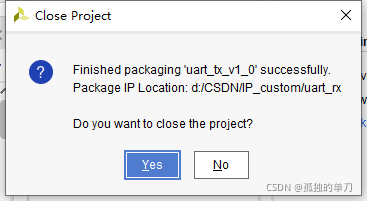

IP核成功打包,如下:

打包串口接收模块uart_rx

使用同样的方法把串口接收模块也打包成IP。

调用

接下来分别调用这两个IP核,构成串口接收--发送循回,依次验证IP核打包及调用是否成功。

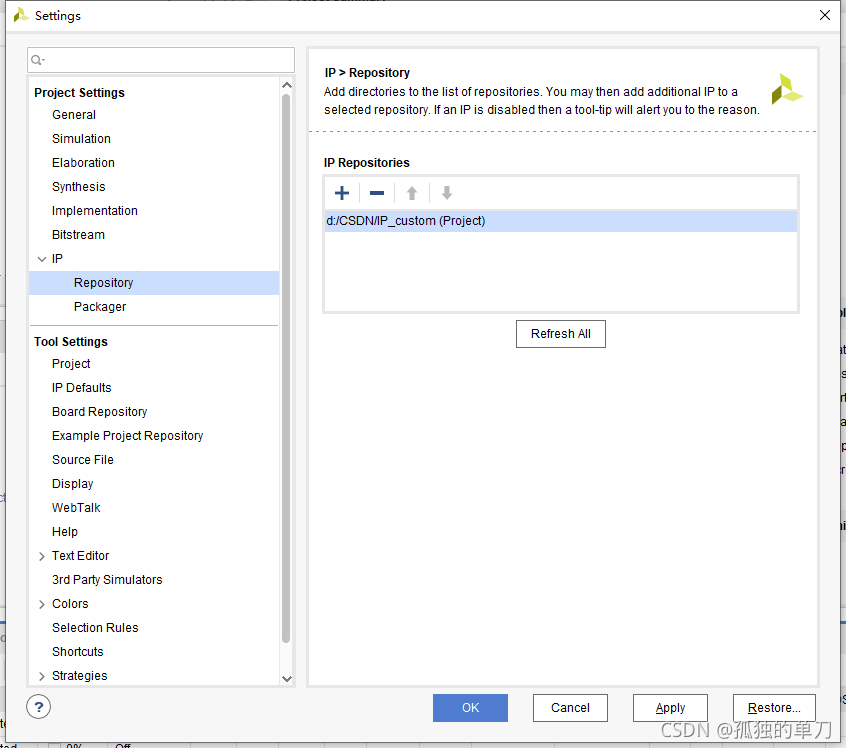

首先新建一个工程,点击Settings----IP----Repository, 添加IP核所在路径:

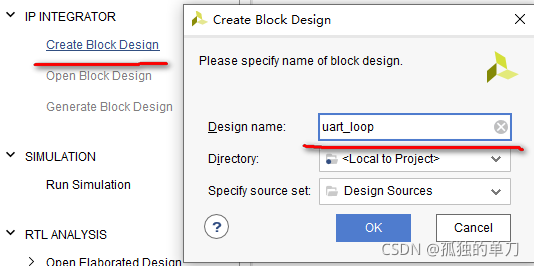

点击 create block design,新建一个BD模块,建议名称与项目名称一致。

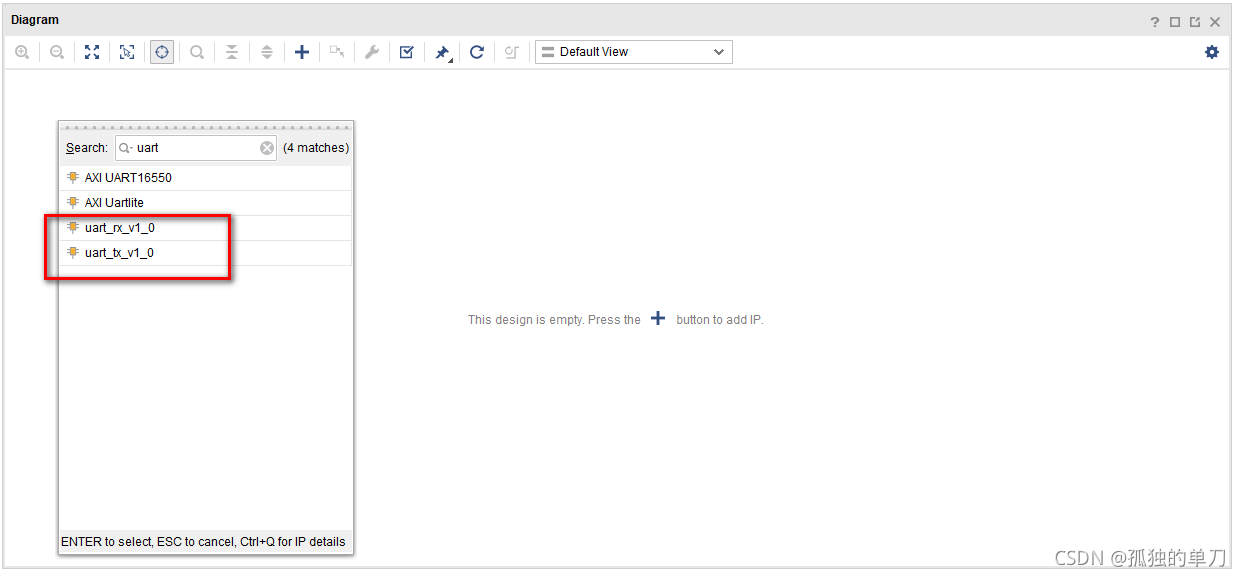

在BD编辑窗口添加IP,搜uart就出现了我们打包的两个IP核:

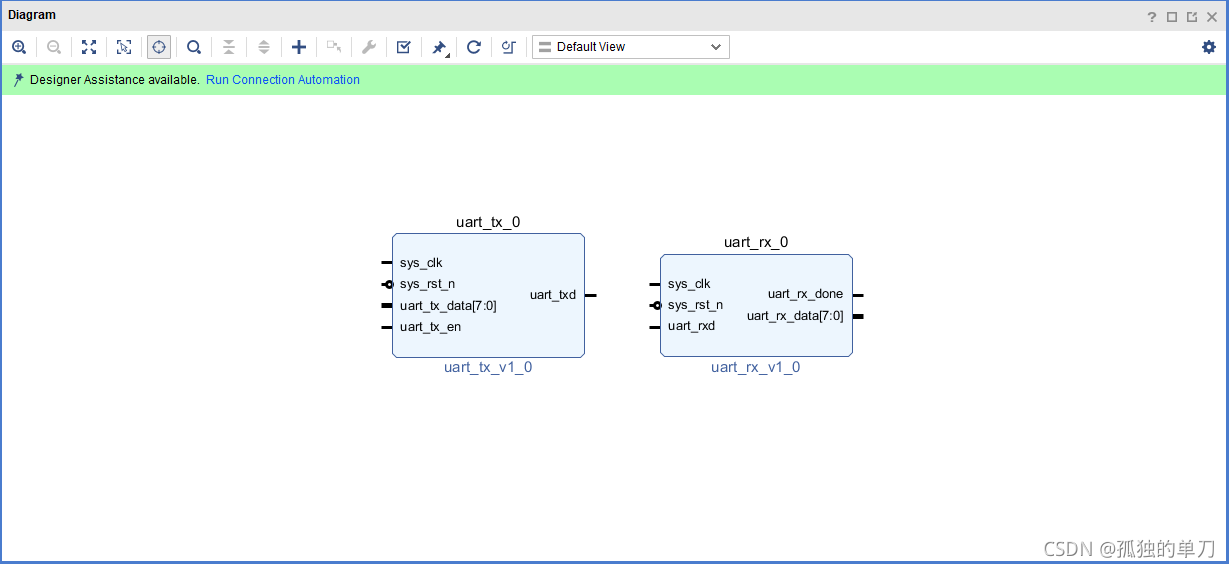

分别添加串口发送模块和串口接收模块:

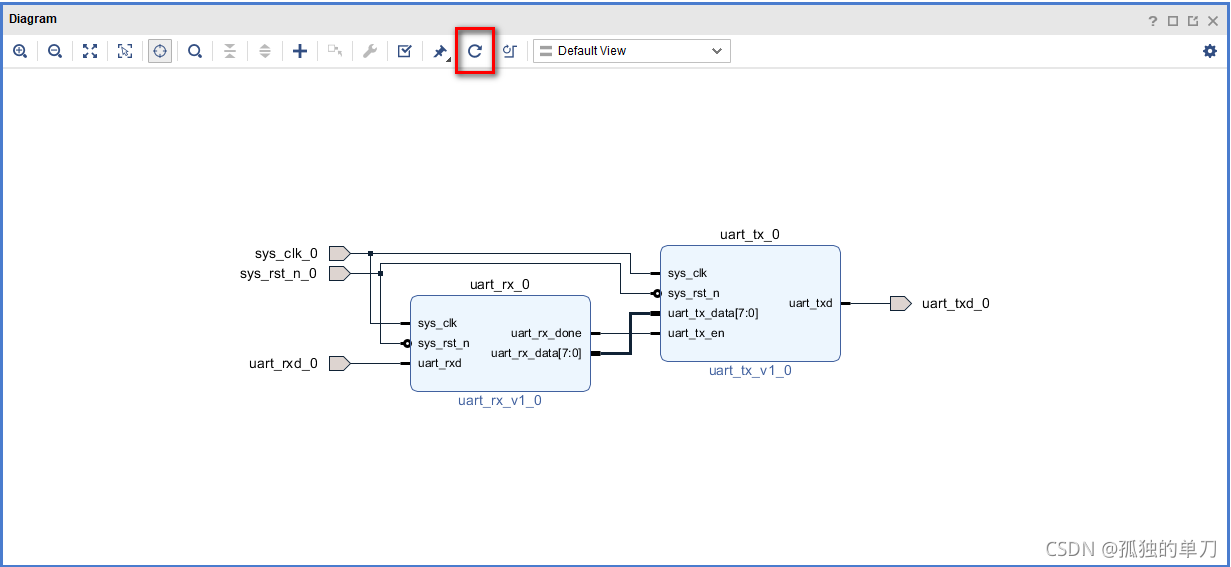

把对外的四个端口(clk,rst,txd,rxd)引出来,右击sys_clk,点击make external ,其他三个端口操作一致;再把对应的线连接,然后点击regenerate layout:

这里我们的 Block Design 就设计完成了,在 Diagram 窗口空白处右击,然后选择“Validate Design” 验证设计。验证完成后弹出对话框提示“Validation Successful”表明设计无误,点击“OK”确认。最后按 快捷键“Ctrl+S”保存设计。

接下来在 Source 窗口中右键点击 Block Design 设计文件“system.bd”,然后依次执行“Generate Output Products”和“Create HDL Wrapper”。

然后添加管脚约束,生成bit流文件。

测试

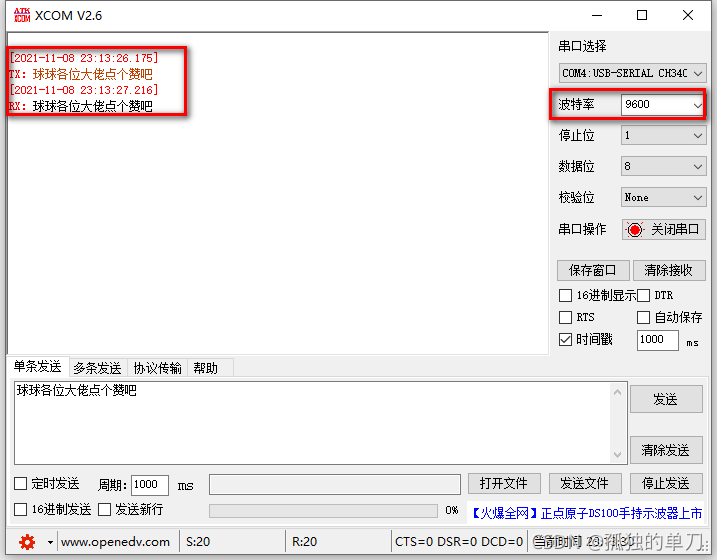

下载bit流文件,使用串口调试助手发送一包数据给FPGA,理论上FPGA马上回相同的信息给串口调试助手(此时串口波特率9600):

返回设计阶段,点击IP核框图,将波特率改为115200,如下:

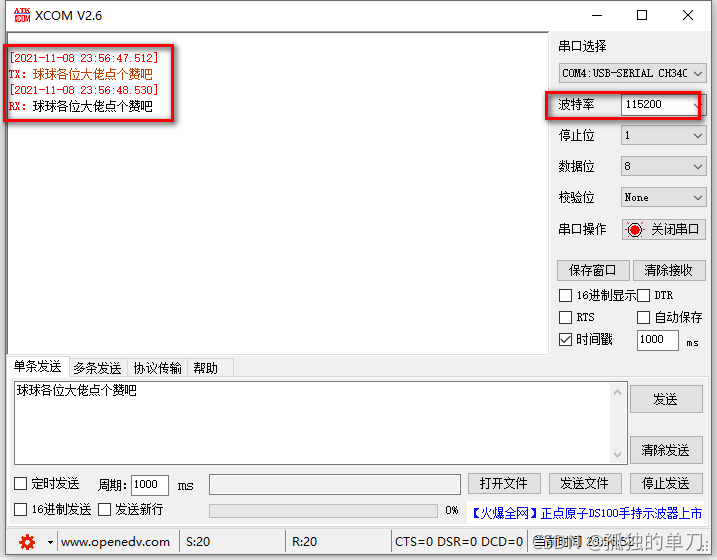

重新生成并下载bit流文件,使用串口调试助手发送一包数据给FPGA,理论上FPGA马上回相同的信息给串口调试助手(此时串口波特率115200):

参考资料:

UG1118----Creating and Packaging Custom IP

米联客----XILINX 7 系列 FPGA 基础入门

审核编辑:符乾江

-

IP核

+关注

关注

4文章

339浏览量

51706 -

Vivado

+关注

关注

19文章

846浏览量

70462

发布评论请先 登录

使用AXI4接口IP核进行DDR读写测试

Windows环境下用Vivado调试E203

利用vivado实现对e200_opensource 蜂鸟E203一代的仿真

VDMA IP核简介

E203移植genesys2(差分时钟板)生成比特流文件全过程

vcs和vivado联合仿真

Vivado浮点数IP核的握手信号

ram ip核的使用

VIVADO自带Turbo译码器IP核怎么用?

一文详解Video In to AXI4-Stream IP核

Vivado FIR IP核实现

教你打包一个自己的Vivado IP核

教你打包一个自己的Vivado IP核

评论