FPGA 器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21320浏览量

593192 -

集成电路

+关注

关注

5320文章

10732浏览量

353369 -

IP

+关注

关注

5文章

1404浏览量

148272

发布评论请先 登录

相关推荐

用于 Xilinx FPGA Zynq 7 的电源解决方案

描述该参考设计采用多种 TPS54325 和其他 TI 电源器件,是适用于 Xilinx Zynq FPGA 的全套电源解决方案。输入电压达到 12V 后,该参考解决方案可提供

发表于 04-14 09:46

Xilinx FPGA Zynq 7全套电源解决方案包括BOM及原理图

描述该参考设计采用多种 TPS54325 和其他 TI 电源器件,是适用于 Xilinx Zynq FPGA 的全套电源解决方案。输入电压达到 12V 后,该参考解决方案可提供

发表于 09-11 09:14

Xilinx Zynq FPGA电源设计方案包括BOM及层图

序列。主要特色专为 Xilinx Zynq FPGA 应用而设计采用 TPS84A20 和 TPS84320 降压稳压器模块的紧凑型解决方案和易于使用的设计受控的加电和断电序列要作为“插件”模块使用,假定在外部 PCB 上使用额

发表于 09-12 08:50

使用教程分享:在Zynq AP SoC设计中高效使用HLS IP(一)

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq

发表于 02-07 18:08

•3257次阅读

用于 Xilinx FPGA Zynq 7 的电源解决方案

该参考设计采用多种 TPS54325 和其他 TI 电源器件,是适用于 Xilinx Zynq FPGA 的全套电源解决方案。输入电压达到 12V 后,该参考解决方案可提供

发表于 02-11 09:39

•3023次阅读

Zynq-7000 AP SoC提供业经验证的IP及参考设计

HLS(高

层次综合)工具特别感兴趣,这是一个非常强大的工具,可以帮助设计者快速地找到Zynq-7000设计架构的平衡点,并开发出高度优化的系统.Zynq平台支持目前最流行的所有软件设计

环境,领先竞争对手整整一代发货,赛灵思还提供了一整套的业经

如何使用Zynq-7000 VI进行IP仿真验证和调试

本视频将向您讲解如何使用Zynq-7000 VIP(验证IP)来高效地验证基于Zynq-7000处理系统的设计。另外,视频还介绍了如何配置,

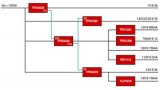

基于ZYNQ FPGA与PC的IP设计与验证方案(7)

Zynq-7000系列的可编程结构经定制可以最大化系统级性能,满足特定应用的各种需求。该套件提供了包括开发工具、AMB4AXI4即插即用IP核和总线功能模型(BFM)等在内的完整硬件开发环境,有助于加速设计和验证工作。

基于ZYNQ FPGA与PC的IP设计与验证方案(6)

赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双ARMCortex-A9MPCore处理器系统作为“主系统”,结合低功耗28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。

基于ZYNQ FPGA与PC的IP设计与验证方案(5)

应用开发人员利用可编程逻辑强大的并行处理能力,不仅可以解决多种不同信号处理应用中的大量数据处理问题,而且还能通过实施更多外设来扩展处理系统的特性。系统和可编程逻辑之间的高带宽AMBA®-AXI互联能以极低的功耗支持千兆位级数据传输,从而解决了控制、数据、I/O和存储器之间的常见性能瓶颈问题。

基于ZYNQ FPGA与PC的IP设计与验证方案(4)

Zynq-7000嵌入式处理平台系列的每款产品均采用带有NEON及双精度浮点引擎的双核ARMCortex-A9MPCore处理系统,该系统通过硬连线完成了包括L1,L2缓存、存储器控制器以及常用外设在内的全面集成。

基于ZYNQ FPGA与PC的IP设计与验证方案(2)

赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台Zynq系列。旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。

基于ZYNQ FPGA与PC的IP设计与验证方案(1)

AXI总线是一种多通道传输总线,将地址、读数据、写数据、握手信号在不同的通道中发送,不同的访问之间顺序可以打乱,用BUSID来表示各个访问的归属。主设备在没有得到返回数据的情况下可发出多个读写操作。读回的数据顺序可以被打乱,同时还支持非对齐数据访问。

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

仿真和验证是开发任何高质量的基于FPGA的RTL编码过程的基础。在上一篇文章中,我们介绍了面向实体/块的仿真,即通过在每个输入信号上生成激励并验证RTL代码行为是否符合预期,对构成每个IP

基于ZYNQ FPGA与PC的IP设计与验证方案

基于ZYNQ FPGA与PC的IP设计与验证方案

评论