大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16:45 17573

17573 在确定了算力的基础上,尽量最大化硬件的计算和带宽性能。经历了一年多的理论学习,开始第一次神经网络算法优化的尝试。之所以从一个FPGA开发者转向算法的学习,有几个原因: 第一是神经网络在AI芯片上的部署离不开算法的优化。一个

2020-09-29 11:36:09 5773

5773

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-10-24 14:52:00 1224

1224 在数字IC/FPGA设计的过程中,对PPA的优化是无处不在的,也是芯片设计工程师的使命所在。此节主要将介绍performance性能的优化,如何对时序路径进行优化,提高工作时钟频率。

2025-12-09 10:33:20 2961

2961

不断地更新。 就控制而言,FPGA可以应用在分散控制的小节点上,也可以在大节点上应用更高效能的FPGA SoC。区别于MCU,通过FPGA控制的系统最明显的优势点就是驱动反应时间会大大缩短,整个系统的运行速度会有一个较大提升。毕竟MC

2022-08-01 07:26:00 2782

2782 :使用已知的库(cuBLAS)或框架(Torch with cuDNN)FPGA:使用Quartus Early Beta版本和Power Play图3:GEMM测试结果。GEMM是DNN中的关键操作在低

2017-04-27 14:10:12

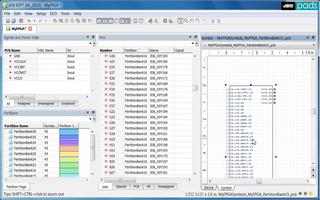

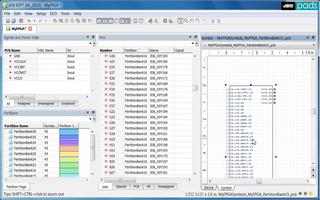

,即将 HDL 合成和先进的 FPGA-PCB I/O 优化添加到 PADS Professional 中,便可应对这些挑战。HDL 设计环境和 PCB 上物理实施之间的这一接口大大缩短了产品的上市

2018-09-20 11:11:16

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

了一系列优化算法,但是用户仍有必要遵循一定的编码风格去引导 综合工具在特定 FPGA 架构上达到最优结果。 设计规划用于指导用户把设计更好地适配到所选用的 FPGA上并合理地 平衡面积和速度的要求,目的

2022-09-29 06:12:02

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

本文介绍一种基于FIFO结构的优化端点设计方案。

2021-05-31 06:31:35

介绍一种嵌入式框架模板的构建方案

2022-02-22 06:25:45

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

2024-08-16 19:56:07

上是最优的。

简单易用是指播放框架提供了两种接口形式:JS和结合ArkUI提供的UI控件接口,便于开发者使用。

灵活扩展是指播放框架针对服务类目的引擎,可增强、可扩展、可替换。

2 、播放框架介绍

2023-01-03 16:36:59

本章提要最优化问题广泛存在于国民经济各部门和工程应用各领域中。在所有可能的方案中搜索出最合理的、边到事先预定的最优目标方案(即最优方案〉的方法称为最优化方法。本章简要介绍了优化问题的分类及工程背景

2012-03-06 14:53:54

目录STM32硬件框架介绍IIC初始化STM32硬件框架介绍首先我们来看IIC通信的硬件架构可以看出,可以分为以上4部分。第一部分:通信接口SDA信号和SCL信号由此产生或输入第二部分:时钟部分

2021-08-24 06:18:53

系列文章目录嵌入式开发|嵌入式软件框架《一》常用的软件框架介绍与选择文章目录系列文章目录前言一、cola os程序框架1.cola_init2.cola_device3.cola_os task任务

2021-11-08 08:17:44

的发行版不是很多,比如DKhadoop,可以说是目前国内自主做hadoop商业版比较好的了。下面就以大快搜索DKhadoop为例来给大家介绍一下hadoop框架结构! 图示:DKhadoop技术技术架构图

2018-10-15 15:59:43

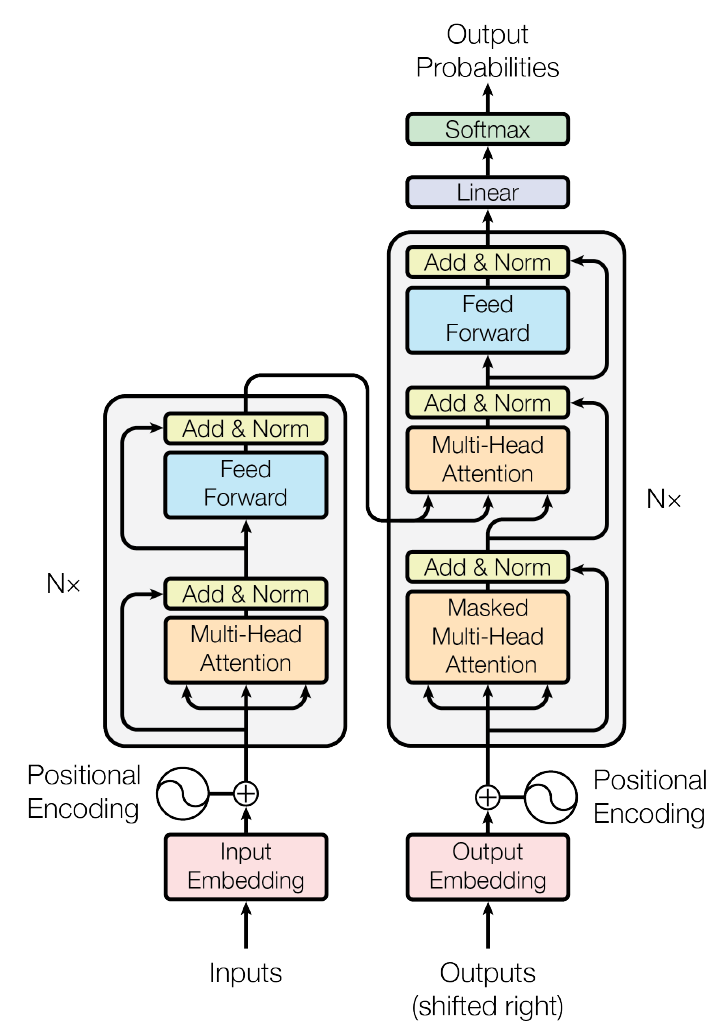

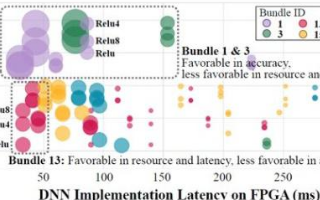

AI等方面。在许多领域中,DNN目前的准确性已经超过人类。与早期的专家手动提取特征或制定规则不同,DNN的优越性能来自于在大量数据上使用统计学习方法,从原始数据中提取高级特征的能力,从而对输入空间进行

2017-06-14 21:01:14

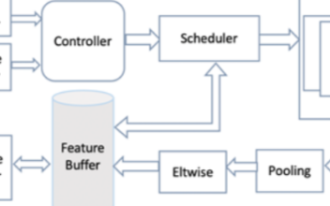

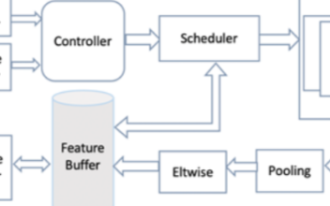

和CPU映射的系统架构;在FPGA上实现并优化的NPU软核和指令集。下图展示了使用脑波项目进行DNN加速的完整流程。对于一个训练好的DNN模型,工具会首先将其表示为计算流图的形式,称为这个模型的“中间表示

2019-08-11 04:00:00

模块可以作为任何初学者进入基于深度学习的计算机视觉领域的一个完美起点。OpenCV DNN模块对于Intel CPU有深度的优化,性能不错,在ARM上的表现就比较一般了。我们使用的人脸检查模型

2023-01-11 22:06:56

一个简单实用的MCU程序框架(非操作系统,简单调度任务) - 总体介绍 单片机程序,总体上可分为跑操作系统的和没操作系统,对于无MMU的小单片机,操作系统通常是UCOS、RTOS等实时操作系统

2022-02-11 06:21:42

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

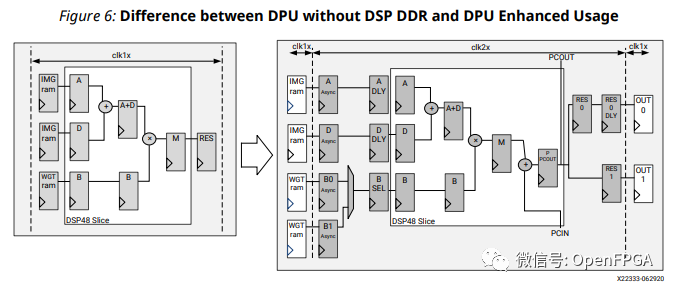

本文阐述了Spartan-3 FPGA针对DSP而优化的特性,并通过实现示例分析了它们在性能和成本上的优势。

2019-10-18 07:11:35

FPGA实现。易于适应新的神经网络结构深度学习是一个非常活跃的研究领域,每天都在设计新的 DNN。其中许多结合了现有的标准计算,但有些需要全新的计算方法。特别是在具有特殊结构的网络难以在 GPU 上

2023-02-17 16:56:59

方案如图4所示。这是一个功能正确的应用实现方案,但没有进行任何性能优化或为充分利用FPGA架构的功能进行考虑。因此该代码在SDAccel中编译完成后,在Alpha Data卡上运行得到的最大吞吐量仅为

2019-06-19 07:27:40

我想知道基于FPGA出租车计价系统实现的技术框架是什么?

2016-04-26 10:36:46

机智云物联网开源框架App工程(Eclipse工程)介绍:机智云开源框架(GizOpenSource_AppKit_Android) 是开源的适用于物联网的软件框架,用于无缝的支持设备到设备的互联

2017-02-15 17:56:40

机智云物联网开源框架App工程(Eclipse工程)https://git.oschina.net/dantang/GizOpenSource_AppKit_Android 介绍:机智云开源框架

2016-12-27 15:47:27

CPU优化深度学习框架和函数库机器学***器

2021-02-22 06:01:02

DNN:关于神经网络DNN的知识点总结(持续更新)

2018-12-26 10:41:47

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

《Altera FPGA/CPLD设计(高级篇)》结合作者多年工作经验,深入地讨论了Altera FPGA/CPLD的设计、优化技巧。在讨论FPGA/CPLD设计指导原则的基础上,介绍了Altera器件的高级应用;引领读者

2009-02-12 09:19:12 4807

4807 本文简要介绍了MPEG4-SP在DSP TM1300上的实现和优化过程。分析了其性能优化原理,给出了性能优化中使用到的几个技巧,最终取得了满意的优化效果。

2009-05-09 14:14:45 13

13 针对某航空望远镜主结构的重量过高的问题,提出了对航空相机望远镜主框架进行拓扑优化设计的方法。基于拓扑优化理论,在重力过载的工况下对望远镜主框架拓扑优化,以整

2010-01-18 12:04:48 19

19 本文讨论了MELP混合线性码激励的FPGA实现的硬件构成,介绍了硬件主要组成芯片及MELP编解码的主要框架,可以用于下一步软件程序的编制。

2011-12-29 09:38:13 1736

1736

基于FPGA的SM3算法优化设计与实现的论文

2015-10-29 17:16:51 5

5 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 ST MCU选型框架介绍,感兴趣可以看看。

2016-07-25 18:52:51 10

10 基于FPGA的可堆叠存储阵列设计与优化

2017-01-07 21:28:58 0

0 SC15大会Alpha Data宣传的是基于Xilinx Virtex-7 690T FPGA运行Auviz DNN(Auviz公司开发的在赛灵思 FPGA 上实现卷积神经网络的函数库)算法,并且演示

2017-02-08 18:10:29 720

720

引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49:00 11898

11898 参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行

2017-02-09 06:24:11 320

320 MapReduce框架下的Skyline结果优化算法_马学森

2017-03-19 11:41:51 0

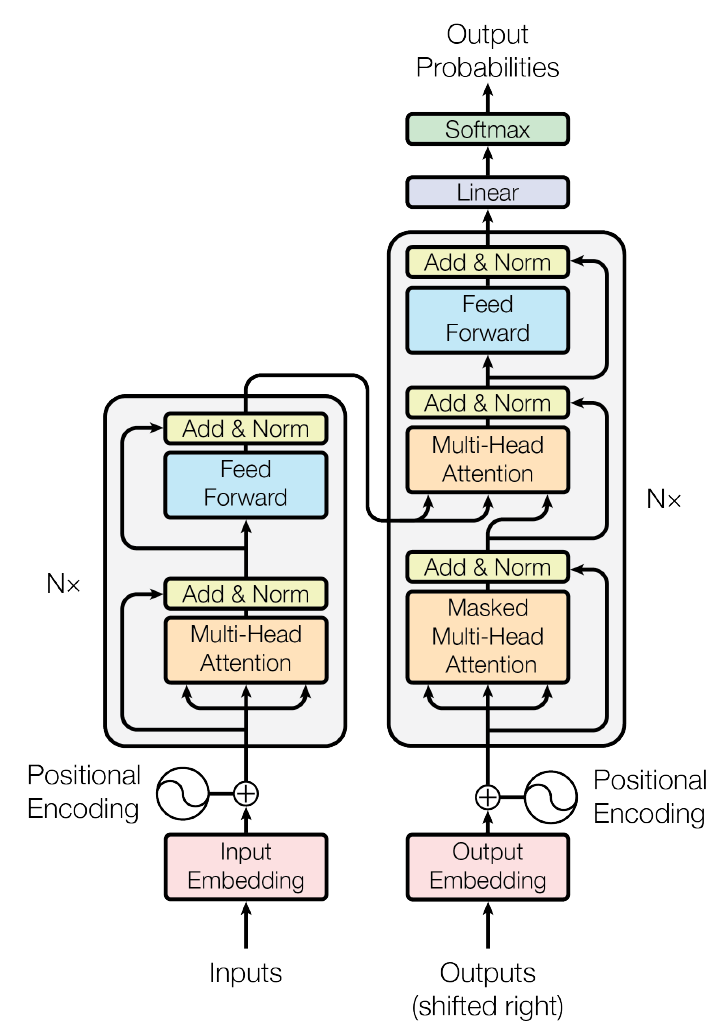

0 AI等方面。在许多领域中,DNN目前的准确性已经超过人类。与早期的专家手动提取特征或制定规则不同,DNN的优越性能来自于在大量数据上使用统计学习方法,从原始数据中提取高级特征的能力,从而对输入空间进行有效的表示。

2018-07-08 06:45:00 23278

23278

android框架与应用开发介绍

2017-10-24 09:35:00 7

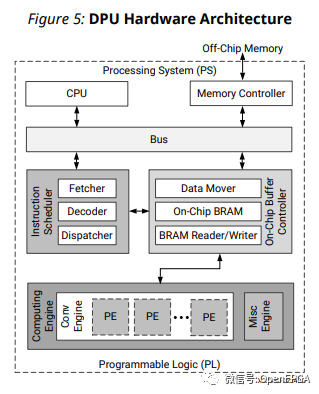

7 基于FPGA的通用CNN加速器整体框架如下,通过Caffe/Tensorflow/Mxnet等框架训练出来的CNN模型,通过编译器的一系列优化生成模型对应的指令;同时,图片数据和模型权重数据按照优化规则进行预处理以及压缩后通过PCIe下发到FPGA加速器中

2017-10-27 14:09:58 10618

10618

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 7860

7860 现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 3842

3842 算法选择的目的是从众多可用优化算法中自动地选出最适用于当前问题的算法。针对算法选择问题提出了基于元学习推荐的优化算法自动选择框架。依据此框架,以多模式资源受限的项目调度问题为实证数据集,设计实现了

2017-12-04 15:28:43 0

0 谷歌用深度学习分析电子病例的重磅论文给出了一个意外的实验结果,DNN与逻辑回归效果一样,引发了热烈讨论。

2018-06-28 16:01:33 7311

7311

深度神经网络在很多任务上都已取得了媲美乃至超越人类的表现,但其泛化能力仍远不及人类。德国蒂宾根大学等多所机构近期的一篇论文对人类和 DNN 的目标识别稳健性进行了行为比较,并得到了一些有趣的见解

2018-10-19 00:48:01 6750

6750 可是,设计一个基于FPGA的高性能DNN推理加速器还是充满了困难,它需要寄存器传输级(RTL)编程技巧,硬件验证知识和丰富的硬件资源分配经验等硬件设计相关知识,对于在算法层面关注深度学习的研究人员来说是非常不友好的。

2018-11-16 10:39:17 6538

6538 在本演示中,来自IBM的Bruce Wile讨论了新推出的CAPI SNAP框架,该框架支持FPGA加速。

“SNAP”框架是“存储,网络和分析编程”的缩写,可以在数据流动时加速对数据的分析

2018-11-29 06:09:00 3862

3862 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着从 C

2018-12-16 11:19:28 1903

1903

FPGA I/O 优化功能提供了自动化 FPGA 符号生成流程,该流程与原理图设计和 PCB 设计相集成,可节省大量创建 PCB 设计的时间,同时提高原理图符号的总体质量和准确性。

2019-05-20 06:16:00 3867

3867

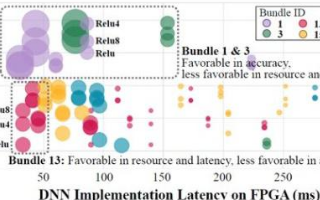

UIUC、IBM 和 Inspirit IoT, Inc(英睿物联网)的研究人员提出 DNN 和 FPGA 加速器的协同设计方案(DNN/FPGA co-design),通过首创的「Auto-DNN

2019-06-10 14:39:30 1613

1613

DNN是去中心化新闻网络的简称,是一个政治新闻平台,结合去中心化网络与新闻制作,传递社区制作的最真实有效的内容。

当今的新闻报道充斥着博人眼球的头条新闻和错误信息,导致虚假新闻和信息不对称的报道。DNN提供了一个公开世界的蓝图,制作和消费新闻的同时通过激励保证新闻的准确性。

2019-08-20 14:26:11 2580

2580 浪潮宣布开源发布基于FPGA的高效AI计算框架TF2,这一框架的推理引擎采用全球首创的DNN移位计算技术,结合多项最新优化技术,可实现通用深度学习模型基于FPGA芯片的高性能低延迟部署。

2019-09-09 14:17:53 1358

1358 浪潮宣布开源发布基于FPGA的高效AI计算框架TF2,这一框架的推理引擎采用全球首创的DNN移位计算技术,结合多项最新优化技术,可实现通用深度学习模型基于FPGA芯片的高性能低延迟部署,这也是全球首个包含从模型裁剪、压缩、量化到通用模型实现等优化算法的完整方案的FPGA上AI开源框架。

2019-09-23 15:04:56 2350

2350 简要介绍了遗传算法的基本原理, 建立了弧形闸门主框架优化数学模型, 探讨了各种寻优算法的优劣及约束问题的处理方法, 并结合MAT LAB 语言将遗传算法应用于该主框架优化设计中。结果表明, 遗传算法对闸门优化设计是有效的、可行的。

2019-09-23 17:10:00 2

2 信号销任务之间可以自动优化PCB上的多个fpga同时尊重pin-specific规则和约束。减少路由层,减少跨界车和整体跟踪PCB上的长度,并减少信号完整性问题较高的毕业率和更短的FPGA路线时间。

2019-10-14 07:06:00 3662

3662 在北京举行的2019人工智能计算大会(AICC2019)上,浪潮宣布开源发布基于FPGA的高效AI计算框架TF2,这一框架的推理引擎采用全球首创的DNN移位计算技术,结合多项最新优化技术,可实现通用深度学习模型基于FPGA芯片的高性能低延迟部署。

2019-12-17 15:22:00 1276

1276

互联;每片FPGA使用PCIE X8与板上CPU Intel XEON互联;每片FPGA使用20对LVDS互联;CPLD控制FPGA上电时序/CPU启动/FPGA加载;每片FPGA挂载2路4GB

2021-01-07 10:15:31 5788

5788

本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 26

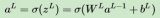

26 在 深度神经网络(DNN)模型与前向传播算法 中,我们对DNN的模型和前向传播算法做了总结,这里我们更进一步,对DNN的反向传播算法(Back Propagation,BP)做一个总结。 1. DNN反向传播算法要解决的问题

2021-03-22 16:28:22 4292

4292

fpga在工业上的应用有哪些?

2021-09-19 09:09:00 3799

3799 优秀的 Verilog/FPGA开源项目介绍(一)-PCIe通信 今天开始会陆续介绍一些优秀的开源项目,项目基本都是和FPGA或HDL相关的。对于一些找工作或者急需项目经验的人来说,这些项目都有一定

2021-10-11 15:31:47 11032

11032

从事FPGA开发无论是仿真还是上板验证,总少不了各种各样的case遍历,手动执行起来就太麻烦了。尤其像从事FPGA加速行业来说,CPU与FPGA版卡的交互和测试基本基于PCIe来实现,而软件有大量

2022-05-20 14:47:19 3661

3661 例如,经过训练以识别狗品种的 DNN 将遍历给定的图像并计算图像中的狗是某个品种的概率。用户可以查看结果并选择网络应该显示哪些概率(超过某个阈值等)并返回建议的标签。每个数学操作都被认为是一个层,复杂的 DNN 有很多层,因此被称为“深度”网络。

2022-06-16 09:27:14 2478

2478 目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-08-15 09:13:31 2967

2967 电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46:14 2379

2379 本篇文章我们将介绍瑞萨为R-Car V4H提供的三种类型的DNN开发模拟器,以及它们的使用情况和特点。

2023-02-02 11:06:53 2309

2309 本文是决策树的第三篇,主要介绍基于 Boosting 框架的主流集成算法,包括 XGBoost 和 LightGBM。

XGBoost

2023-02-17 15:57:58 1650

1650

英特尔 加速器架构实验室的Eriko Nurvit ad hi 博士以 最新 的 GPU 为参照,对两代 Intel FPGA 上新兴的DNN 算法 进行了评估,认为新兴的低精度和稀疏

2023-03-11 13:05:06 1093

1093 基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有

2023-05-11 15:33:30 1291

1291

之前的文章介绍了FPGA在线调试的方法,包括选定抓取信号,防止信号被优化的方法等等。

2023-06-20 10:38:48 9670

9670

摘要 在瑞萨提供的R-Car SoC相关的一些DNN模拟器中,本文将重点介绍 能够实现与实际硬件等价运算的Accurate Simulator ,并说明如何应用它来 分析和提高神经网络的精度。 太田

2023-07-13 18:15:04 993

993

包体积优化中,资源优化一般都是首要且容易有成效的优化方向。资源优化是通过优化APK中的资源项来优化包体积,本文我们会介绍得物App在资源优化上做的一些实践。

2023-07-24 09:00:48 1516

1516

深度学习cntk框架介绍 深度学习是最近几年来非常热门的话题,它正在彻底改变我们生活和工作的方式。随着越来越多的创新和发展,人工智能和机器学习的应用范围正在大大扩展。而对于深度学习这个领域来说

2023-08-17 16:11:23 2190

2190 电子发烧友网站提供《FPGA在新兴DNN推理领域的应用.pdf》资料免费下载

2023-09-15 10:52:53 0

0 电子发烧友网站提供《新兴DNN推理领域的FPGA.pdf》资料免费下载

2023-09-15 10:09:41 0

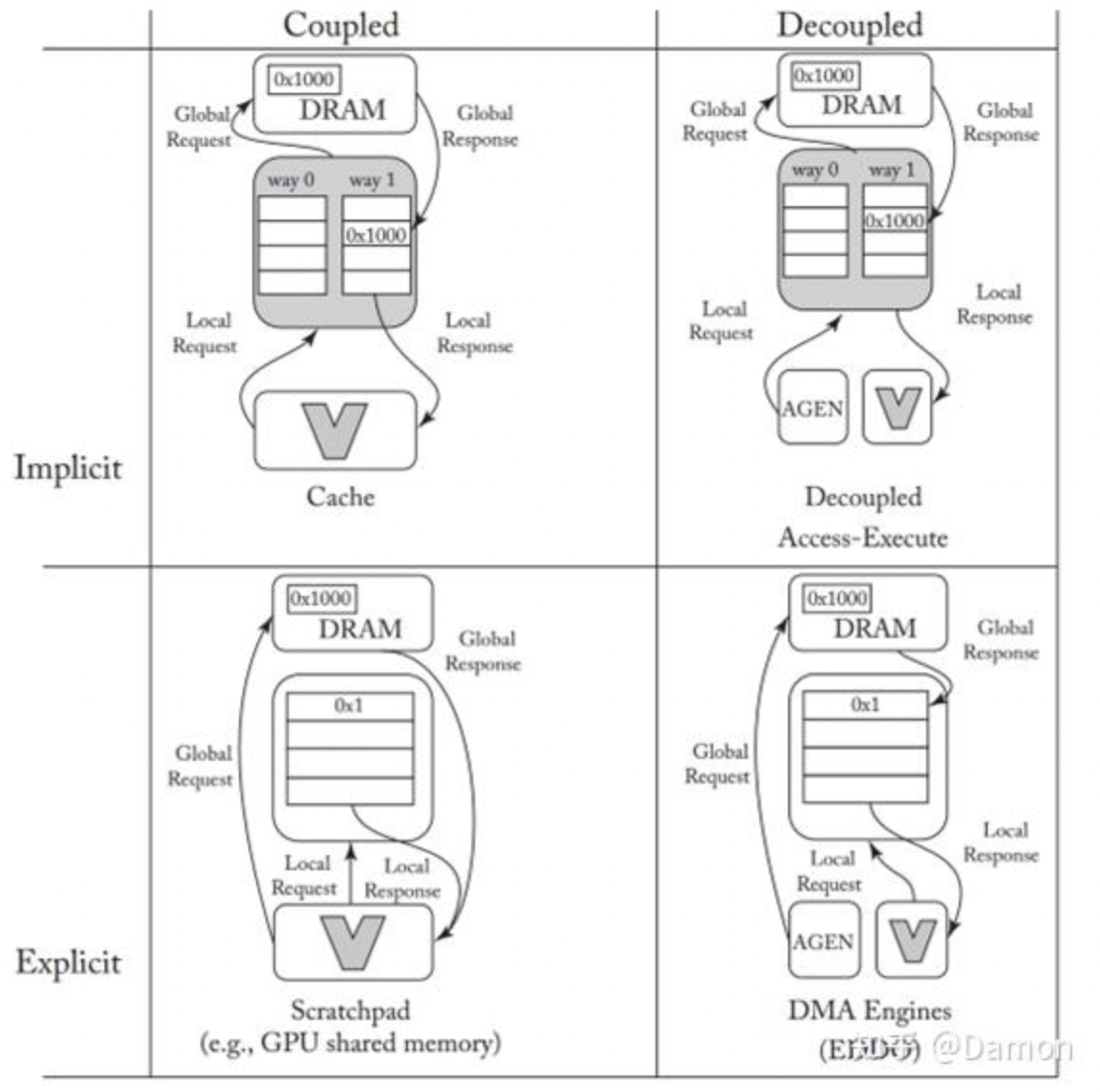

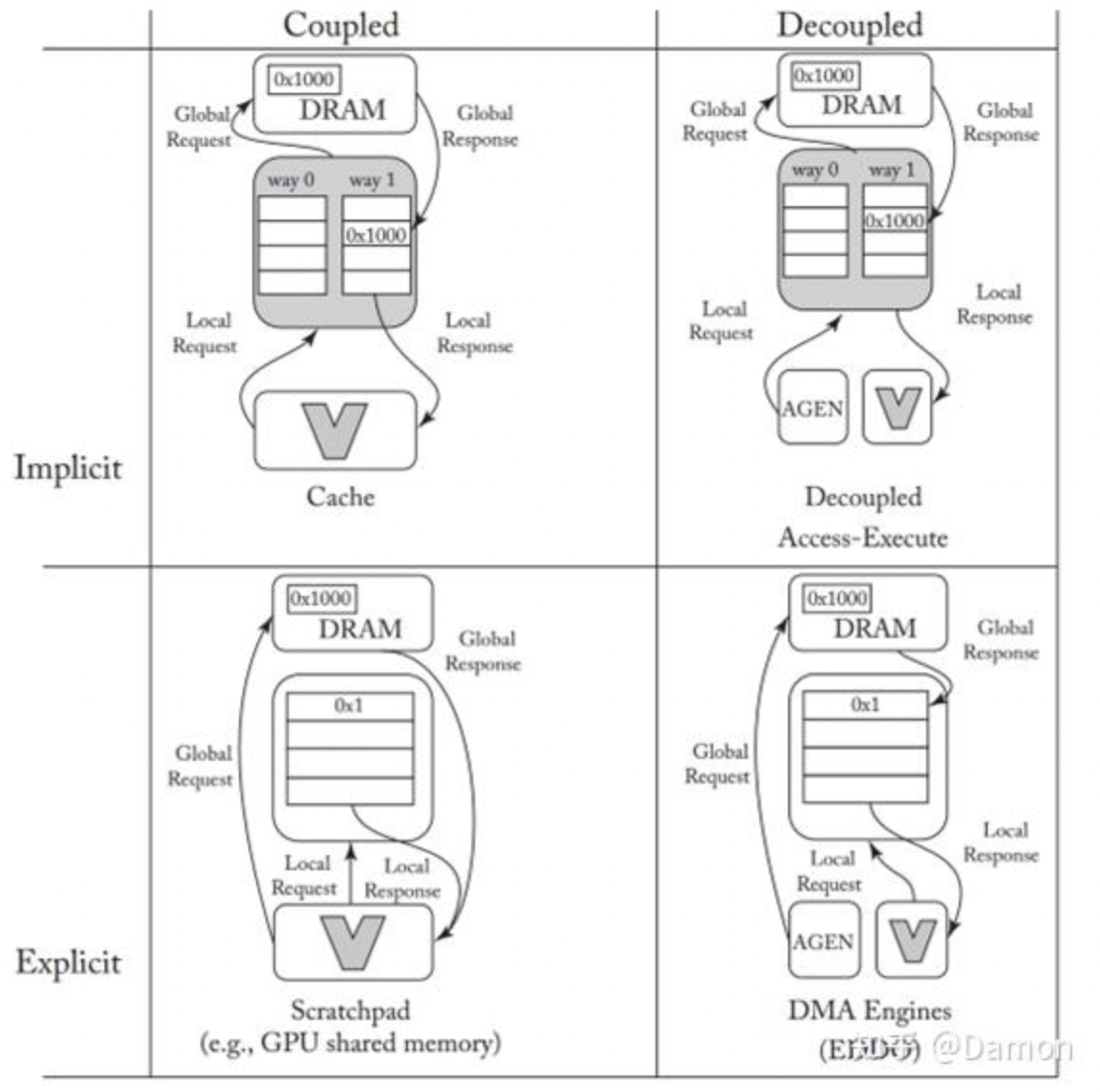

0 如前所述,数据缓存是创建高效DNN加速器的关键组件之一。因此,除了选择适当的数据流(控制数据缓存的位置和时间)外,DNN加速器还需要一个缓存方案

2023-10-17 17:23:56 2285

2285

一文看懂FPGA芯片投资框架

2023-01-13 09:06:26 4

4 国产FPGA研究框架

2023-01-13 09:06:57 11

11 电子发烧友网站提供《基于FPGA的神经振荡器设计及优化.pdf》资料免费下载

2023-11-10 09:39:29 0

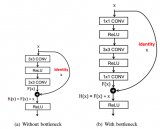

0 DNN中应用最广泛的是CNN和RNN,CNN是一种卷积网络,在图片识别分类中用的较多,RNN可以处理时间序列的信息,比如视频识别和语音识别。

2024-04-07 10:23:04 1147

1147

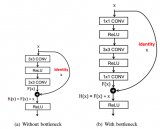

堆叠多个隐藏层,逐步提取和转化输入数据的特征,最终实现复杂的预测和分类任务。本文将对DNN的架构进行详细解析,并探讨其优化策略,以期为相关研究和应用提供参考。

2024-07-09 11:00:11 5047

5047 优化FPGA(现场可编程门阵列)设计的性能是一个复杂而多维的任务,涉及多个方面和步骤。以下是一些关键的优化策略: 一、明确性能指标 确定需求 :首先,需要明确FPGA设计的性能指标,包括时钟频率

2024-10-25 09:23:38 1454

1454 SSM框架的性能优化技巧 SSM(Spring + Spring MVC + MyBatis)框架的性能优化是提升Java Web应用性能的关键环节。以下是一些常用的性能优化技巧: 使用缓存

2024-12-17 09:10:45 1230

1230 随着AI应用的广泛深入,单一框架往往难以满足多样化的需求,因此,AI开发框架的集成成为了提升开发效率、促进技术创新的关键路径。以下,是对AI开发框架集成的介绍,由AI部落小编整理。

2025-01-07 15:58:39 1017

1017

电子发烧友App

电子发烧友App

评论