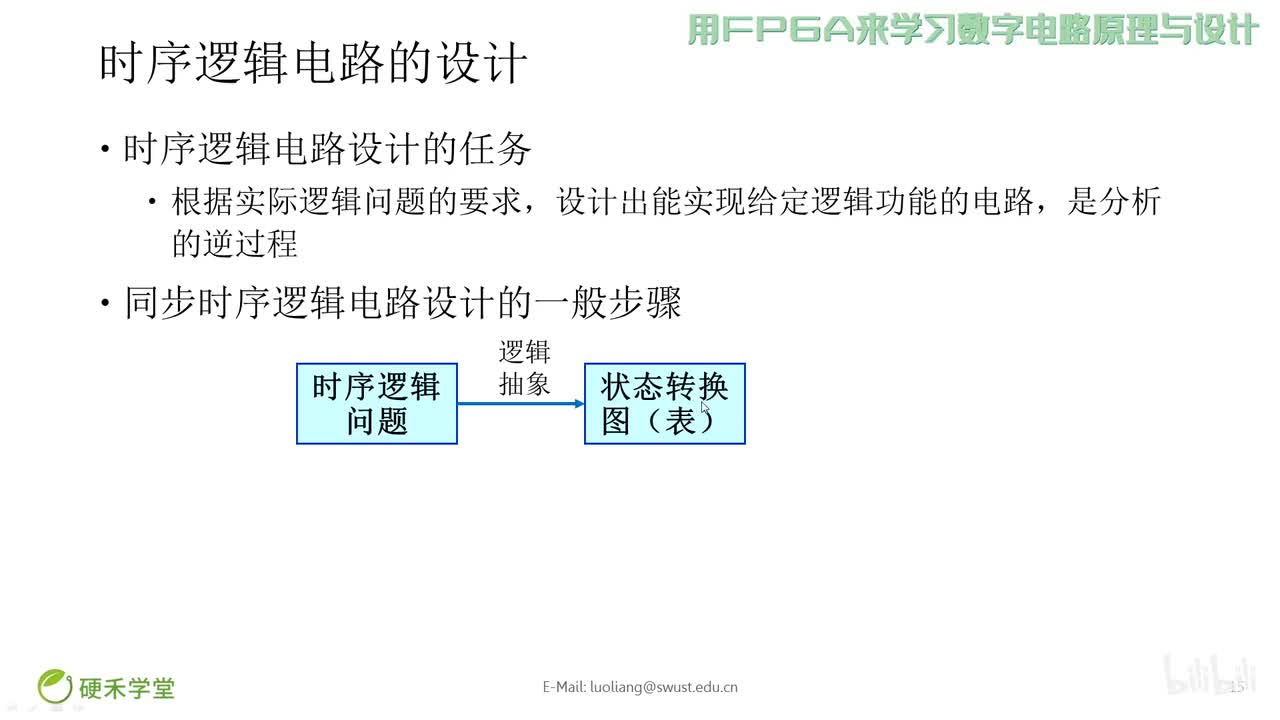

本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 18789

18789

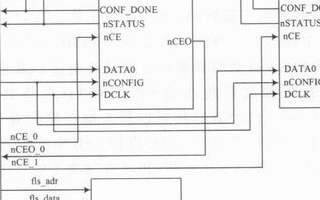

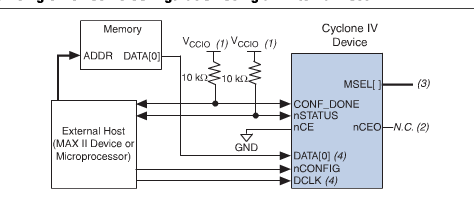

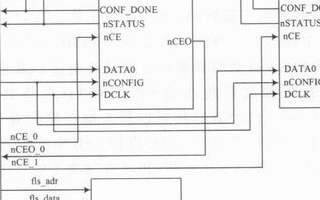

在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;

2023-02-20 10:18:27 8049

8049

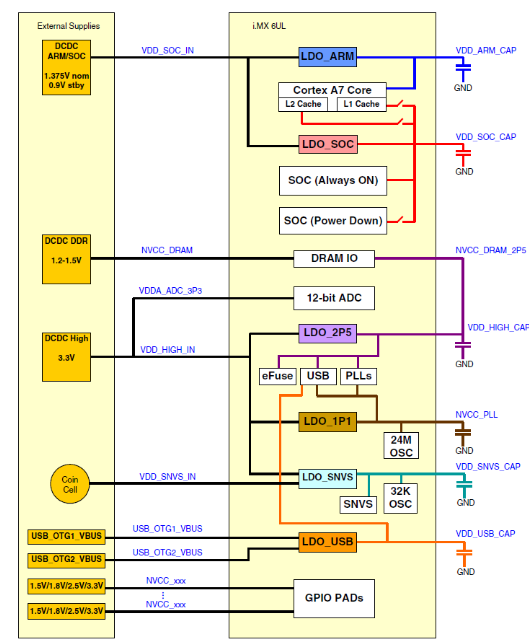

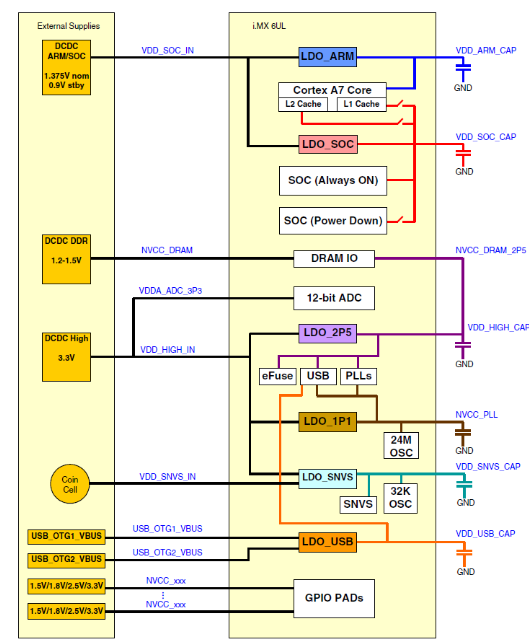

对于 DSP、CPU、GPU、FPGA等高性能处理器而言,确保其各模块所需电源的上电顺序对实现其可靠运行、提高效率并保障整体系统健康至关重要。

2025-07-16 13:49:20 3076

3076

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?

2017-04-19 10:42:54 8098

8098

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现以下情况,第一,上电

2018-05-16 18:03:32 8364

8364

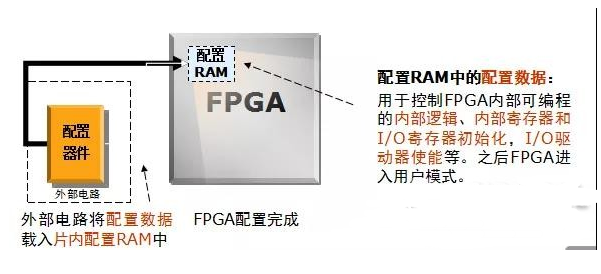

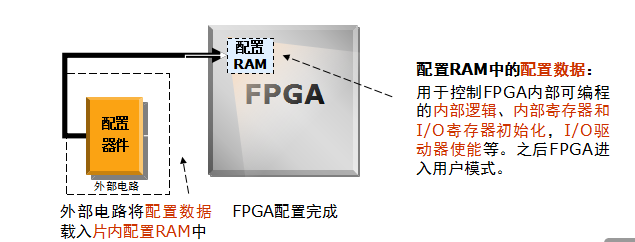

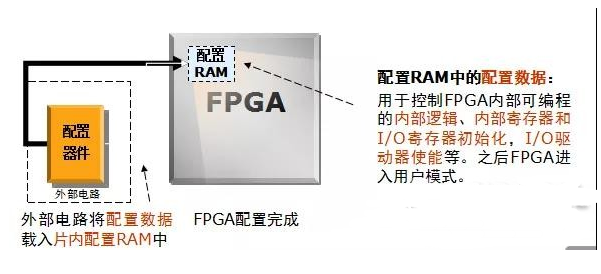

大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16:45 17573

17573 表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 3687

3687

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 目前,大多数 FPGA 芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常

2022-12-26 18:10:00 3584

3584 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

`FPGA 上电配置时候IO口会有一个短暂的3.3V 10ms 的电平,导致我控制端出现问题,我想问下如何可以避免这个电平`

2020-11-23 10:31:40

是 FPGA/ASIC 时序定义的基础概念。后面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。周期约束是一个基本时序和综合约束,它附加在时钟网线上,时序分析工具根据

2024-06-17 17:07:28

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA中几个基本的重要的时序分析参数介绍(fmax\tsu\th\tco\tpd)今天无聊,翻开书偶看到介绍时序部分的东西,觉得其中几个参数缩写所代表的含义应该记住,故写如下文章……FPGA中

2012-04-09 09:41:41

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

是基于静态随机存储器(SRAM) 结构的,断电后程序丢失后的每次上电都需要重新加载程序。且随着FPGA 规模的升级,加载程序的容量也越来越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其

2019-06-14 06:00:00

FPGA程序写完编译已用94%的资源。下载没有问题,上电后,有时正常运行,有时一上电没有现象,示波器看管腿的波形也没有,怀疑FPGA没有工作,有时epcs4的程序没有正确下载。量了FPGA的供电也都正常。到底是什么问题呢?

2015-01-08 15:18:37

前言操作环境:Windows 7 64bitISE 14.7 FPGA程序加载与固化将开发板通过Xilinx FPGA JTAG下载器连接到PC机,打开Windows的设备管理器查看下载器是否已正常

2020-09-25 09:57:45

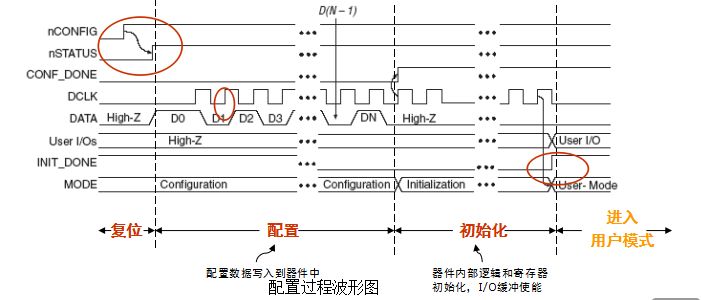

。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN属性在Vivado中设置ExMasterCclk_en选项 三、FPGA加载时序 上电时序图 上电时序图 上电配置流程 其配置过程分解为8个步骤。 1、上电 7

2021-01-15 16:43:43

cyclone fpga jtag突然不能下载程序,测量了一下电压,发现上电后 ,nstatus管教一直是低电平,其他供电正常 ,这是为什么呢?求帮忙解答,谢谢了

2016-09-27 20:40:03

学习的时候了解到FPGA的多路供电要求一定的上电断电顺序,目前在搞Altera的Cyclone IV系列的FPGA,主要有内部逻辑供电VCCINT,PLL供电VCCD_PLL,IO口供电VCCIO等

2017-05-18 22:36:29

为什么有不同的上电时序

2023-11-02 08:13:09

如果要求输出是vdd=3.3v,我是不是可以这样设计上电顺序:首先设置Vgg=-2V,再VCtrl=1V,再Vdd=3.3V,然后调节Vgg,使Igg=140mA,那么它们之间的上电时序是如何控制的。

2023-11-22 07:14:57

1.同样的板子,用过好多块,都没有问题,就这块无法加载,应该不是PCB设计问题。2.我设计的是主串加载模式(Master Serial)。硬件上将FPGA的M2~M0直接接到GND上。3.上电以后

2015-08-15 09:20:26

次的加载失败。为定位此问题,花费了一个多月,先后投入多位专家,最终确定问题的根源是“上电的时序问题”,特为此给大家分享。二、XILINX的上电启动流程 FPGA上电启动包含三大流程,分别是Setup

2022-02-24 09:37:51

1.问下aurix的TC397的上电时序要求是怎样的呢?

2.有看视频说TC3XX系列没有上电时序的要求,但是在Errata手册里看到,又有VDDM和VDD上电时间要求,否则会导致lock,能帮忙确认下AURIX TC397系列的上电时序要求吗?

2024-06-04 09:39:55

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现以下情况,第一,上电

2019-10-18 07:53:02

需要将FPGA程序通过I2C或者RS232加载到FPGA内部,然后通过FPGA存储到SPI FLASH中,再次上电后从SPI FLASH加载。 这个过程中,有以下几个问题:1.怎样将.v文件转换成

2016-04-29 14:46:21

按照TAS5711的datasheet中的上电时序进行上电,芯片正常工作,但是无法编辑寄存器,是时序有问题吗?

我是按照这个上电时序来上电的:AVDD/DVDD上电(3.3V),上电之前A_SEL

2024-10-22 06:58:25

如何用EEPROM对大容量FPGA芯片数据实现串行加载?如何设计并-串转换时序?

2021-04-29 07:13:12

各位前辈,FPGA采用并行加载方式,现CPLD外挂一片FLASH,要求用CPLD控制加载时序,从FLASH读取代码,送入FPGA,应该怎么用CPLD控制加载时序,程序应该怎么写,有可以参考的资料吗,谢谢各位了!

2013-02-21 12:07:34

模拟时序控制器IC。它能控制和监视四个电压域。电压的上电和关断是通过控制相应电压转换器上的使能(开/关)引脚进行的。电压转换器的开启时间可以利用小电容产生的时间延迟来调整。各输出电压通过相应的监控引脚

2021-04-12 07:00:00

有一个项目中用到OPA192这个放大器,有两个问题:

1.V+是+12V供电的,V-是-12V供电的,想问下+12V和-12V这两个电有没有什么必须的上电时序需要控制?

2.还有就是我的项目

2024-07-29 08:30:16

现在的FPGA还严格要求上电时序吗?想请教一下大家

2017-09-26 15:39:07

引言 电源时序控制是微控制器、FPGA、DSP、 ADC和其他需要多个电压轨供电的器件所必需的一项功能。这些应用通常需要在数字I/O轨上电前对内核和模拟模块上电,但有些设计可能需要采用其他序列

2019-07-03 08:15:19

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行

2019-07-18 08:10:11

请问fx3有上电时序要求吗

2025-05-09 07:29:38

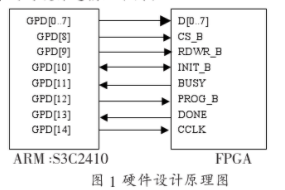

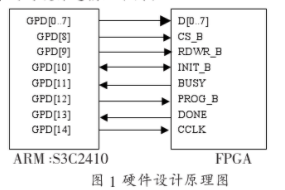

基于ARM+FPGA的可重构控制器设计及其在加载系统中的应用:文章提出了一种基于ARM+FPGA结构的可重构控制嚣的设计方法.并采用此方法开发了用于加载系统的2通道电液伺服控制器

2010-03-02 12:03:21 29

29 如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

2009-04-15 14:19:31 947

947

介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 根据FPGA芯片加载时序分析,本文提出了采用通过市面上常见的Flash ROM芯片替代专用PROM的方式,通过DSP的外部高速总线进行FPGA加载;既节约了系统成本,也能达到FPGA上电迅速加载的目的

2011-08-16 16:26:14 2130

2130

3 FPGA设计流程 完整的FPGA 设计流程包括逻辑电路设计输入、功能仿真、综合及时序分析、实现、加载配置、调试。FPGA 配置就是将特定的应用程序设计按FPGA设计流程转化为数据位流加载

2013-01-16 11:52:22 16

16 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1476

1476 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Power on Sequence:主板上的供电,从最开始的电压适配器电压输入,到最后CPU供电的产生,都有严格的开启顺序控制,这个先后顺序,就是上电时序。

2016-09-01 15:44:10 0

0 主板开机原理与上电时序图

2016-12-17 21:30:39 0

0 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

fpga时序收敛

2017-03-01 13:13:34 23

23 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 3842

3842 时序以及各阶段I/O 管脚状态,说明了FPGA上电配置对电路功能的严重影响,最后针对不同功能需求的FPGA外围电路提出了有效的设计建议。

2017-11-22 07:18:34 8500

8500

由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN,因此在电路设计中,可使用VDD_HIGH_IN电源芯片的控制信号使能VDD_SOC_IN的电源,如下图所示为使用VDD_HIGH_IN供电芯片的PG信号使能VDD_SOC_IN供电芯片的使能管脚。

2018-04-28 09:57:02 22709

22709

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4865

4865

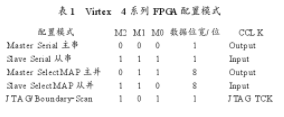

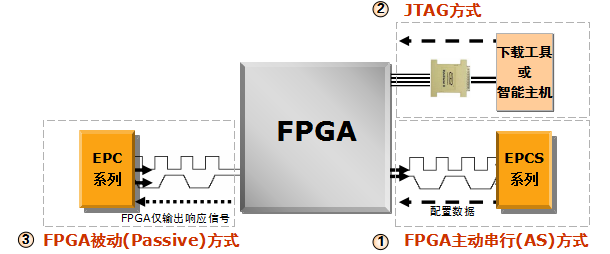

FPGA 的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit 文件并加载到FPGA 中,配置方式有JTAG、从并、从串、主从4 种,不同厂家叫法不同,但实现方式基本都是一样的。

2018-10-30 08:58:00 9336

9336

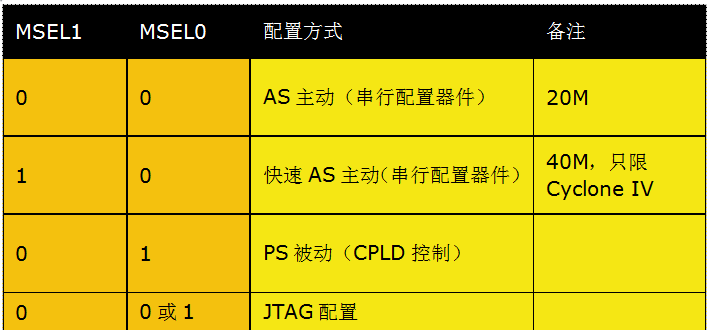

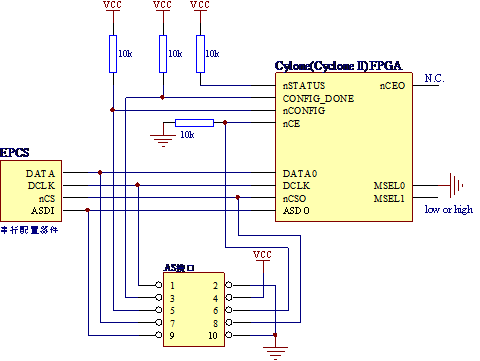

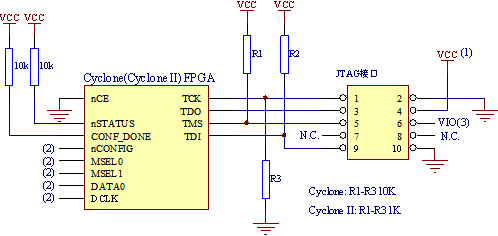

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 19146

19146 可编程的双重优点,被广泛应用于通信领域中。FPGA在上电后,需要加载配置文件对内部各功能模块进行初始化,而配置文件加载的效率直接影响系统的初始化时间。因此如何设计一种高效的FPGA加载方案,是通信系统设计中的一个重要环节。

2019-02-19 14:49:08 2849

2849

加载系统。该系统通过USB芯片将PC中的配置文件传送给CPLD,CPLD再将其写入FLASH芯片,FLASH芯片可以长久地存储配置文件。这样FPGA每次上电后CPLD将FLASH中的配置文件读出来配置

2019-02-20 15:36:23 3797

3797

在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且 FPGA要加载的程序可以

2019-03-22 16:20:14 1470

1470 本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

2019-03-27 10:56:04 20

20 小梅哥FPGAA进阶教程

2019-08-30 06:04:00 2357

2357

常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

2020-04-06 10:33:00 5132

5132

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。FPGA的加载模式主要有以下几种:

2020-04-07 08:00:00 16

16 FPGA在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,FPGA从外部专用的 EPROM读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且

2020-08-13 17:16:46 2922

2922

一:供电电源时序 EMMC 的供电有两种模式,且分两路工作,有 VCC 和 VccQ。在规范上,上电时序是有要求的,如下图所示。 EMMC 上电时序 开始上电时,VCC 或 VccQ 可以第一个倾斜

2020-10-30 21:29:17 3909

3909 时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 67

67 EMMC 的供电有两种模式,且分两路工作,有 VCC 和 VccQ。在规范上,上电时序是有要求的,如下图所示。

2020-12-02 23:13:00 23

23 本文档的主要内容详细介绍的是英业达上电时序的详细资料说明。

2020-12-04 08:00:00 63

63 本文档的主要内容详细介绍的是电源模块的上下电时序介绍免费下载。

2020-12-10 08:00:00 12

12 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 22

22 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 AN-1080: 利用简单时序控制器ADM108x进行上电和关断时序控制

2021-03-21 00:41:43 6

6 基于SRAM结构的FPGA容量大,可重复操作,应用相当广泛;但其结构类似于SRAM,掉电后数据丢失,因此每次上电时都需重新加载。

2021-03-26 13:52:58 6318

6318

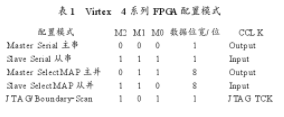

典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2022-03-14 14:02:50 2381

2381 上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-08-15 09:13:31 2967

2967 Class-D 功放TAS5731M 上电时序分析

2022-10-31 08:24:00 1

1 时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息。在

2022-12-28 15:18:38 5209

5209 总结Xilinx FPGA 的上电模式可以分为以下4类型: 主模式 从模式 JTAG模式(调试模式) 系统模式(多片配置模式) 1、主模式 典型的主模式都是加载片外非易失( 断电不丢数据) 性

2023-03-29 14:50:06 2111

2111 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

在不带内置ARM核的AMD FPGA产品系列中,FPGA的程序加载方式并没有发生大的变化

2023-07-07 14:14:58 4513

4513

FPGA高级时序综合教程

2023-08-07 16:07:55 9

9 笔记本上电时序

2024-01-09 10:26:36 1

1 AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝试从FLASH加载配置文件,其与工程是否含有MicroBlaze IP无关。

2024-04-25 12:49:14 1406

1406

电子发烧友网站提供《FPGA电源时序控制.pdf》资料免费下载

2024-08-26 09:25:41 1

1

电子发烧友App

电子发烧友App

评论