优秀的 Verilog/FPGA开源项目介绍(一)-PCIe通信

今天开始会陆续介绍一些优秀的开源项目,项目基本都是和FPGA或HDL相关的。对于一些找工作或者急需项目经验的人来说,这些项目都有一定的参考价值。

这里再介绍一下开源协议的区别,方便大家在阅读使用这些开源项目时尊重规则。

详情查看:https://suisuisi.blog.csdn.net/article/details/120660472

RIFFA项目

RIFFA(FPGA 加速器的可重用集成框架)是一个简单的框架,用于通过 PCI Express 总线将数据从主机 CPU 传送到 FPGA。该框架需要支持 PCIe 的工作站和带有 PCIe 连接器的板上的 FPGA。RIFFA 支持 Windows 和 Linux、Altera 和 Xilinx,具有 C/C++、Python、MATLAB 和 Java 的绑定。适配Xilinx和Intel的FPGA,支持PCIe 2.0设计中对底层硬件进行了抽象,用户使用的过程中无需关注底层的硬件,同时上层软件将PCIe的操作抽象为读和写操作,用户直接调用函数即可。公众号:OpenFPGA

方便软件工程师使用:

在软件方面有两个主要功能:数据发送和数据接收。这些函数通过 C/C++、Python、MATLAB 和 Java 中的用户库公开。该驱动程序支持一个系统中最多5个 FPGA。软件适用于 Linux 和 Windows 操作系统。用户只需编写几行代码即可与 FPGA IP 核进行通信。

方便硬件工程师使用:

在硬件方面,用户访问一个独立的发送和接收信号的接口。这些信号提供事务握手和通过 FIFO 接口读取/写入数据。不需要了解总线地址、缓冲区大小或 PCIe 数据包格式。只需在 FIFO 接口上发送数据并在 FIFO 接口上接收数据。

RIFFA 不依赖于 PCIe 桥接器,因此不受桥接器实现的限制。相反,RIFFA 直接与 PCIe 端点配合使用,运行速度足以使 PCIe 链路饱和。软件和硬件接口都得到了极大的简化。详细信息可以在硬件接口页面上找到。公众号:OpenFPGA

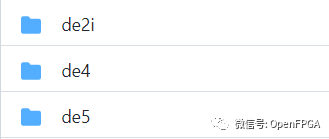

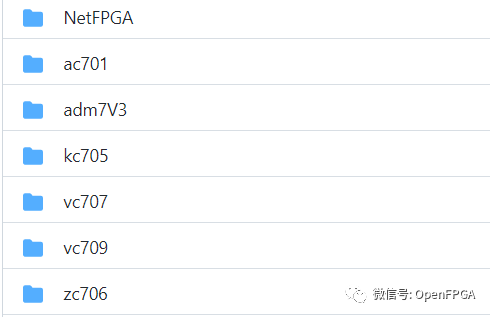

RIFFA 使用直接内存访问 (DMA) 传输和中断信号传输数据。这实现了 PCIe 链路上的高带宽。在我们的测试中,我们能够使所有测试中的链路饱和(或接近饱和)。我们已经在 AVNet Spartan LX150T、Xilinx ML605 和 Xilinx VC707 以及 Altera DE5-Net、DE4 和 DE2i 板上实现了 RIFFA。RIFFA 发行版包含在上面列出的三个开发板上设置设计的示例和指南。

此外,该网站还提供了如何从所有软件绑定访问您的设计的示例。RIFFA 已经在 Fedora 13 和 17(32/64 位版本)和 Ubuntu Desktop 10.04 LTS 和 12.04 LTS(32/64 位版本)上进行了测试。RIFFA 依赖于 Linux 内核 2.6.27+(在 2.6.32 - 3.3.0 之间的版本上测试)支持的自定义 Linux 内核驱动程序。公众号:OpenFPGA

其中FPGA文件夹是我们关心的部分,里面包含了ALtera和XIlinx两大主流FPGA厂家的几款主要板卡的DEMO,如下:

Altera文件夹下:

Xilinx文件夹下:

有兴趣的可以自己查看使用,项目地址:

https://github.com/KastnerRG/riffa

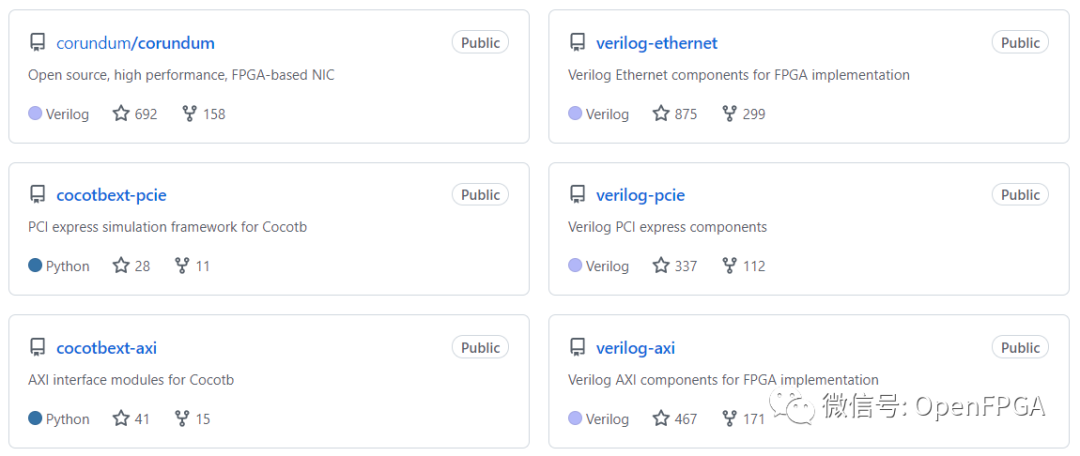

Alex的众多项目

Alex的项目可以用惊艳来形容,绝大部分都是个人开发的,都是非常专业的代码,非常敬佩其专业能力和分享精神,或许这才是真正的诗和远方。公众号:OpenFPGA

Alex Forencich主要项目

包含网络和PCIe相关,其中cocotbext-xxx是仿真测试模型(cocotb is a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.cocotb是一套基于python的用于构建仿真及测试用例的lib库)。

其中cocotbext-axi也是一个非常出名的项目。

有兴趣的可以自己查看使用,项目地址:

https://github.com/alexforencich

个人感觉Alex Forencich的PCIe项目完成度不如RIFFA,前者目前仅支持与 Xilinx UltraScale 和 UltraScale+ PCIe 硬核 IP 核配合使用,接口介于 64 位和 512 位之间。而后者在Altera及Xilinx很多主要平台经过验证,同时配备上位机驱动,方便使用。但是后者的仿真理论(包括使用cocotbext-pcie和 cocotbext- axi 的完整 cocotb 测试平台 。)更加充实,适合研究总线接口。以上仅代表个人愚见,我读书少,喷我你就是对的!

本文为OpenFPGA作者原创,未经本人授权禁止转载!

编辑:jq

-

FPGA

+关注

关注

1664文章

22503浏览量

639290 -

PCIe

+关注

关注

16文章

1479浏览量

88925 -

C++

+关注

关注

22文章

2130浏览量

77378 -

代码

+关注

关注

30文章

4976浏览量

74384 -

python

+关注

关注

58文章

4885浏览量

90309

原文标题:Alex的众多项目

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

微型遥控赛车开源项目介绍

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

开源鸿蒙项目顺利孵化毕业

开源鸿蒙项目达成开源孵化目标顺利毕业

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

开源FPGA硬件|FPGA LAYOUT评审,紫光同创定制公仔派送中

开放原子开源基金会与新一批开源项目完成捐赠签约

普华基础软件荣膺优秀开源项目奖

火爆开发中 | 开源FPGA硬件板卡,硬件第一期发布

火爆开发中|开源FPGA硬件板卡,硬件第一期发布

优秀的 Verilog/FPGA开源项目介绍(一)

优秀的 Verilog/FPGA开源项目介绍(一)

评论