即是相应的 HDL 程序以及最新非常流行的基于高层次综合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。 (1)选择FPGA(SoC)的若干理由 a)FPGA

2020-12-17 12:58:21 5247

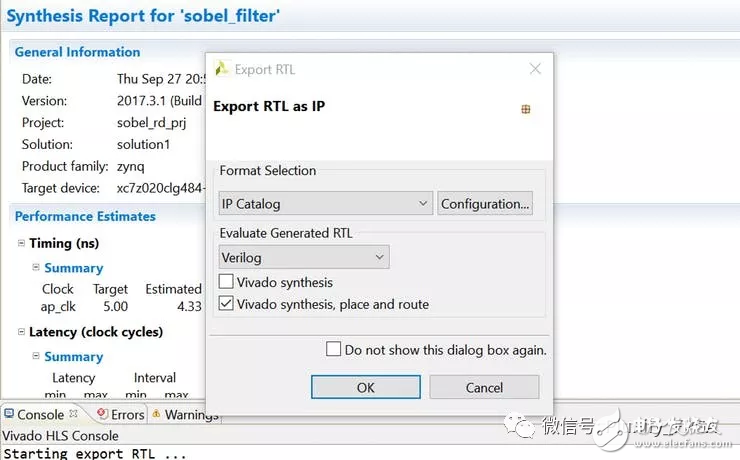

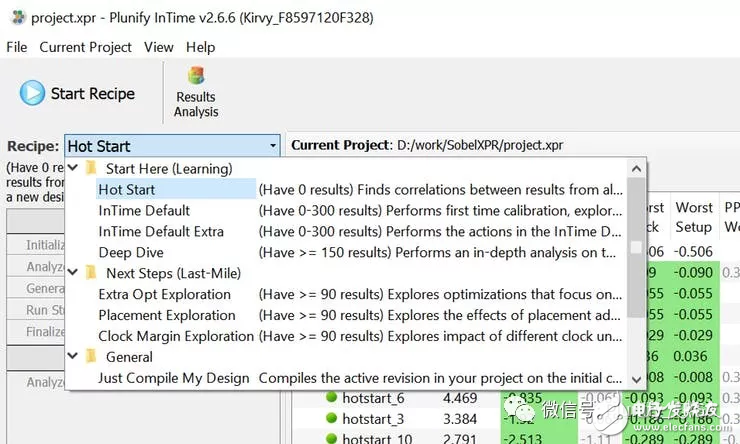

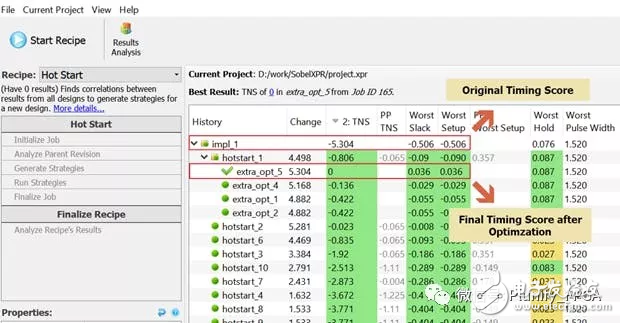

5247 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着从 C 转化得到 RTL 基本不可能。其实,使用 FPGA 工具设置来优化设计可以最

2020-12-20 11:46:46 2390

2390

FPGA设计流程是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的设计流程如上图所示:包括设计定义、代码实现、功能仿真、逻辑综合、前仿真、布局布线、后仿真和板级调试等步骤!

2023-04-04 10:29:51 3088

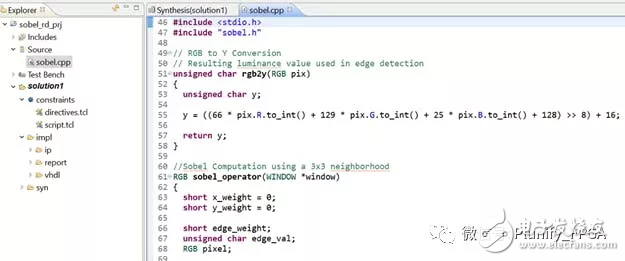

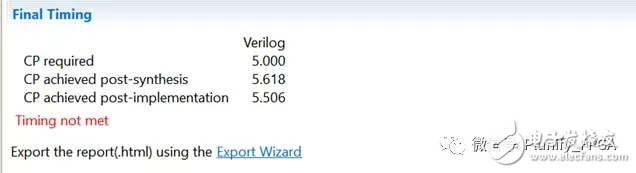

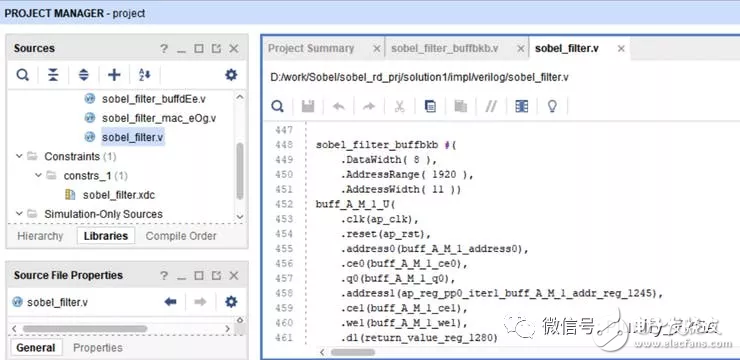

3088 用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

2023-10-30 11:41:01 1312

1312

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

2023-10-30 14:34:36 1625

1625

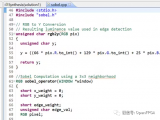

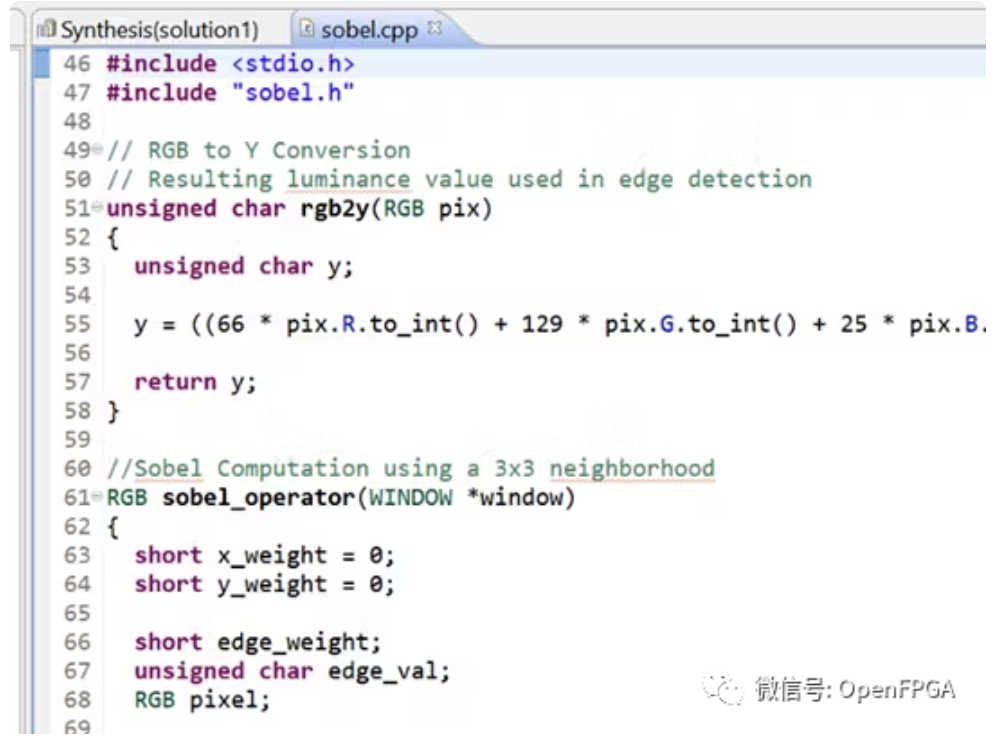

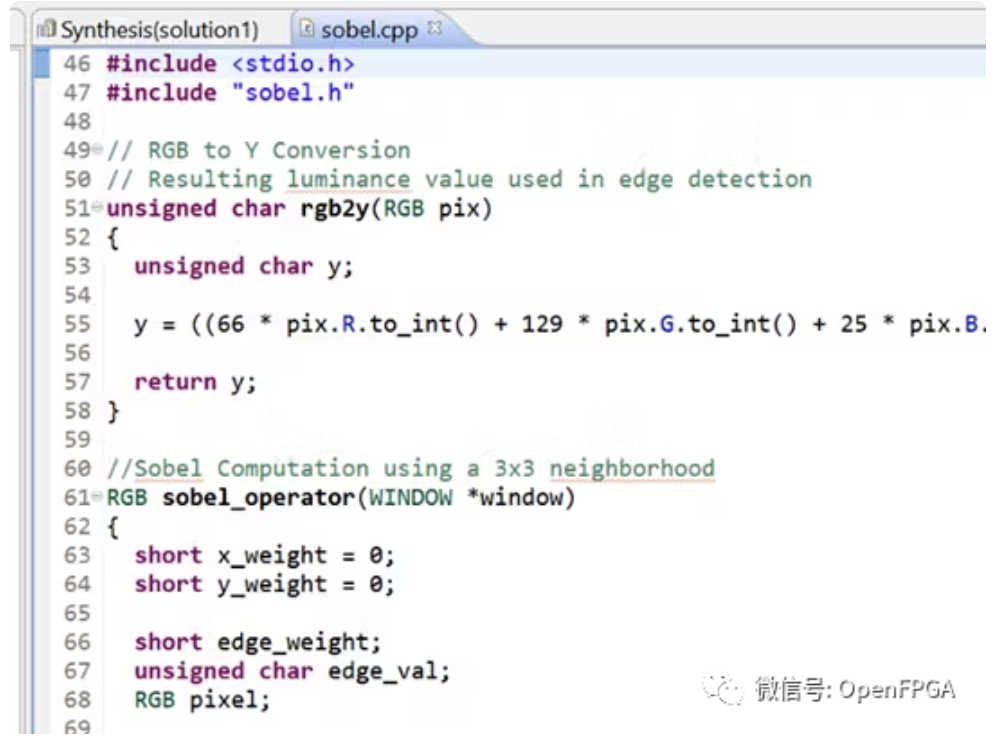

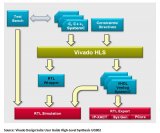

(HLS) 的帮助下,基于 C 语言的语言现在可用于 FPGA 设计。具体来说,AMD Vivado™ HLS 编译器提供的编程环境能够与标准处理器及专用处理器共享关键技术,用于优化 C 语言程序

2023-06-28 18:18:57

。DSP 和 RAM 推论优化当今的高级 FPGA 器件除常规逻辑模块外还包含 DSP 和 RAM嵌入式模块。这样一来,合成工具可了解各种 RTL 编码样式,将其映射到适当的 DSP或 RAM 模块,从而

2018-09-20 11:11:16

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般如图1-10所示,包括电路功能设计、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真

2021-07-23 09:12:07

FPGA设计工具中(如Xilinx的Vivado、Intel的Quartus等),通过IP核管理器或类似的功能,将所选的IP内核添加到设计中。这通常涉及设置内核的参数、配置接口以及将其连接到设计的其余部分

2024-04-28 09:41:04

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

第二章 FPGA 开发流程FPGA 的设计流程就是利用 EDA 开发软件和编程工具对 FPGA 芯片进行开发的过程。原理图和HDL(Hardware description language,硬件

2022-02-23 06:23:33

工作原理及其使用;对比手工编写代码与利用IP快速进行设计的异同;第五阶段 常系数复杂FIR滤波器的设计; 使用基于IP核的设计方法和流程,针对速度、面积、和功耗的优化; 使用EDA工具针对各个综合阶段

2012-09-13 20:07:24

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

2022-09-29 06:12:02

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

`FPGA面积优化1.对于速度要求不是很高的情况下,我们可以把流水线设计成迭代的形式,从而重复利用FPGA功能相同的资源。2.对于控制逻辑小于共享逻辑时,控制逻辑资源可以用来复用,例如FIR滤波器

2014-12-04 13:52:40

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-10 08:00:00

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

2024-08-16 19:56:07

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA TOOL W/MANUAL

2023-04-06 11:27:29

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-06 08:00:00

主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C来对Xilinx系列的FPGA进行编程,从而提高抽象的层级

2020-10-10 16:44:42

针对目标FPGA优化的RTL代码。尽管英特尔的HLS工具在现场的使用率比Xilinx的Vivado HLS少得多,但随着HLS编译器为英特尔One API软件开发平台的“ FPGA”分支提供动力,我们

2024-03-23 16:48:53

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis

2022-09-09 16:45:27

自定义模型,可使用 LabelImg 等工具对数据集进行标注,将数据转为 YOLO 格式。之后,可将 YOLO 格式转换为 ONNX 格式,以便兼容 FPGA 优化工具链。Tiny YOLO 在

2024-12-06 17:18:02

语言进行CPLD/FPGA设计开发,Altera和Lattice已经在开发软件方面提供了基于本公司芯片的强大开发工具。但由于VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且

2019-06-18 07:45:03

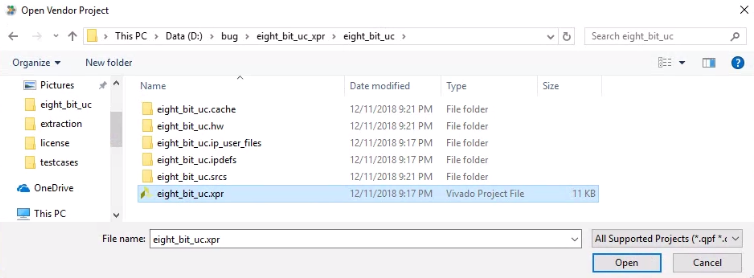

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

开拓者FPGA DEVB_121X160MM 6~24V

2023-03-28 13:06:25

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

用于Xilinx FPGA的Keysight E5910A串行链路优化工具

2019-10-16 10:49:30

如何利用模拟工具优化电路设计?如何利用专用仿真器解决RF电路问题? 使用模拟工具有哪些好处?

2021-04-13 06:40:30

进行编译的。本文仅验证了采用高级语言开发FPGA的可行性,还有很多优化工作待完善,仅以此文为大家提供一个新的视角,为软件开发人员利用FPGA进行算法加速做前期调研,欢迎感兴趣的同事共同交流。

2017-09-25 10:06:29

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

。EasyGo FPGA Solver 的优点在于,能够将Simulink的图形化模型利用解算器软件转化成FPGA执行的代码,而不需要进行FPGA的编译

2022-05-19 09:21:43

FPGA调试工具chipscope,学习与使用FPGA必用的工具。。

2009-03-23 09:45:00 86

86 实用FPGA的调试工具—ChipScope Pro

ChipScope Pro应用于FPGA调试阶段,它具有传统逻辑分析仪的功能,可以观察FPGA内部的任何信号,触发条件,数据宽度和深度等的设

2010-02-09 15:10:46 95

95 基于多种EDA工具的FPGA设计

介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实

2009-05-14 18:38:38 1036

1036

摘 要:在FPGA开发的各个阶段,市场为我们提供了很多优秀的EDA工具。面对眼花缭乱的EDA工具,如何充分利用各种工具的特点,并规划好各种工具的协同使用,对FPGA

2009-06-20 10:51:14 906

906 摘要:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实际操作介绍了

2009-06-20 11:42:45 674

674

FPGA设计工具浅谈

作为一个负责FPGA企业市场营销团队工作的人,我不得不说,由于在工艺技术方面的显著成就以及硅芯片设计领

2009-10-10 07:46:04 619

619 多种EDA工具的FPGA设计方案

概述:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配

2010-05-25 17:56:59 895

895

Mentor Graphics的FPGA Advantage是享誉业界,具有FPGA设计黄金组合的全流程设计工具。本次课程将使用户体验FPGA Advantage如何最大化地加速设计的实现以及复用。同时掌握如何利用FPGA Advantage快速实现设计从创建、理解、仿真验证、综合以及布局布线的全过

2011-03-15 13:39:56 98

98 自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1476

1476 基于FPGA的SM3算法优化设计与实现的论文

2015-10-29 17:16:51 5

5 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 本书用简洁的语言向读者展示了什么是FPGA、FPGA如何工作、如何对FPGA编程以

及FPGA设计中遇到的各种概念、器件和工具,如传统的基于HDL/RTL的仿真和逻辑综合、最新的纯C/C++设计捕获和综合技术以及基于DSP的设计流程。另外,本书还涉及大量丰富的、工程师所需的技术细节。

2016-04-26 11:42:13 3

3 本书用简洁的语言向读者展示了什么是FPGA、FPGA如何工作、如何对FPGA编程以

及FPGA设计中遇到的各种概念、器件和工具,如传统的基于HDL/RTL的仿真和逻辑综合、最新的纯C/C++设计捕获和综合技术以及基于DSP的设计流程。另外,本书还涉及大量丰富的、工程师所需的技术细节。

2016-04-26 11:42:13 4

4 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 FPGA学习资料教程之Xilinx-FPGA高级开发工具,感兴趣的可以看看。

2016-09-01 15:27:27 0

0 利用FPGA实现信号处理算法是一个难度颇高的应用,不仅涉及到对信号处理算法、FPGA芯片和开发工具的学习,还意味着要改变传统利用软件在DSP上实现算法的习惯,从面向硬件实现的算法设计、硬件实现、结构优化和算法验证等多个方面进行深入学习。

2016-12-26 17:26:41 12

12 基于FPGA的可堆叠存储阵列设计与优化

2017-01-07 21:28:58 0

0 参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行

2017-02-09 06:24:11 320

320 Luke Miller并非一开始就是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有过一些糟糕的经历。

2017-02-10 18:48:59 3929

3929

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 7860

7860 现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 3843

3843 通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 3066

3066

本文首先与实测系统功耗进行对比,验证了Xilinx公司ISE软件包中FPGA功耗估算工具XPower的准确性。然后对FPGA设计中影响系统功耗的几个相互关联的参数进行取样,通过软件估算不同样点下的系统功耗,找到功耗最低的取样点,得到最佳设计参数,从而达到优化系统设计的目的。

2017-11-25 09:26:44 2338

2338 1. FPGA 开发流程: 电路设计与设计输入 ;仿真验证:利用Xilinx集成的仿真工具足矣 ;逻辑综合:利用XST(Xilinx Synthesis Tool)工具 ;布局布线:利用Xilinx

2018-01-12 03:59:48 10715

10715 HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7738

7738

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS为FPGA流程提供集成化设计与开发环境,率先支持5G无线应用。

2018-08-30 10:09:32 8283

8283 作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 3178

3178 了解如何利用Xilinx成本优化的FPGA和SoC产品组合的最新增强功能。

2018-11-28 06:20:00 2906

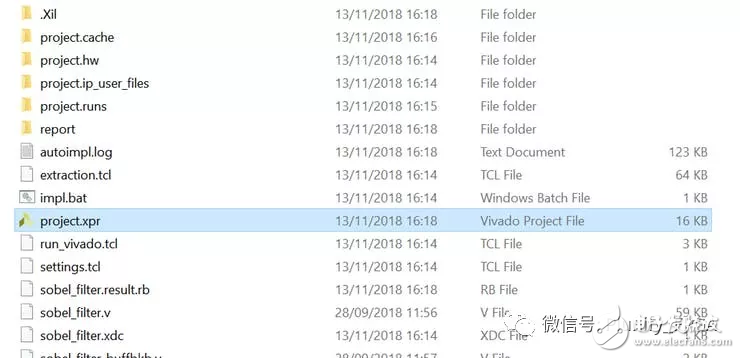

2906 用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。

2019-09-15 11:56:00 767

767 的约束?如果不同管脚可以有不 同约束值,如何设置? FAE:我们的工具提供的是时序分析功能,尚未提供时序约束功能,也就是说可以根据您输入的值作为参考,计算出当前实现的各种时序信息与参考值的差距,但并不会根据输入的值去做优化,所以也就不存在对不同管脚分别设置约束

2019-02-25 18:24:01 741

741

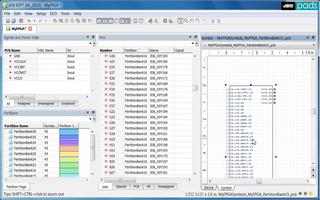

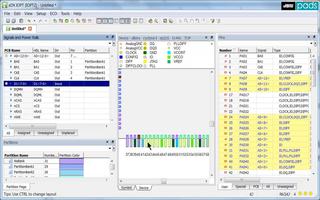

FPGA I/O 优化功能提供了自动化 FPGA 符号生成流程,该流程与原理图设计和 PCB 设计相集成,可节省大量创建 PCB 设计的时间,同时提高原理图符号的总体质量和准确性。

2019-05-20 06:16:00 3867

3867

与 FPGA 软件工具进行自动双向信息交换可提供由供应商规则驱动的“设计即正确”的 I/O 分配,从而实现快速、无误的优化流程。其包括了最新的器件支持,并且可提前访问尚未发布的 FPGA 供应商器件。

2019-05-16 06:13:00 4265

4265

介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 5460

5460 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 7438

7438

自动化和双向信息交换与FPGA软件工具提供了一个correct-by-construction供应商)I / O分配导致快速和错误免费优化过程。包括最新的设备支持和早期的拉菲FPGA供应商设备的访问。

2019-10-16 07:00:00 3269

3269 讨论了利用FPGA工具实现MBUS总线的原理、方法,以实际操作介绍了FPGA设计流程,并给出FPGA常用设计技巧。

2019-12-24 14:54:08 9

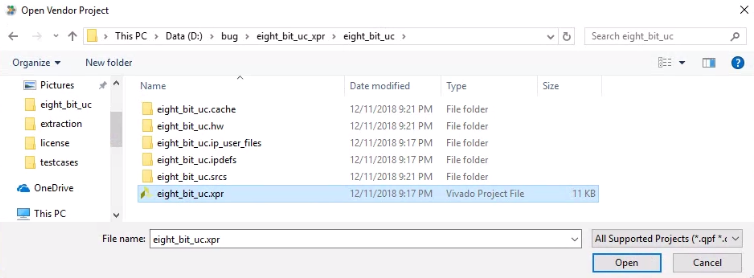

9 教程介绍 本教程旨在指导用户通过 Plunify Cloud 的云服务器,来使用 InTime 软件优化 FPGA 设计。如果您首次使用 InTime,请免费 申请该软件的本地试用 。 本教程涵盖

2020-12-21 17:57:01 1942

1942

elecfans论坛的FPGA模块还是比较活跃的,有各种FPGA工具使用问题的一些讨论。

2020-11-10 14:29:10 5265

5265 本文档的主要内容详细介绍的是FPGA JTAG工具设计的教程说明。

2020-12-31 17:30:55 18

18 1.项目需求 FPGA :V7-690T两片 Resource:两片FPGA通过X12 gth互联;每片FPGA使用48路serdes走光口与板外连接;每片FPGA使用SIROx4通过VPX与外界

2021-01-07 10:15:31 5788

5788

本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 26

26 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 实现,无缝的将硬件仿真环境集合在一起,使用软件为中心的工具、报告以及优化设计,很容易的在 FPGA 传统的设计工具中生成 IP。 传统的 FPGA 开发,首先写 HDL 代码,然后做行为仿真,最后做综合

2022-12-02 12:30:02 7407

7407 对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46:14 2379

2379 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 6467

6467 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 1731

1731

电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 3

3 本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 1647

1647

电子发烧友网站提供《基于FPGA的神经振荡器设计及优化.pdf》资料免费下载

2023-11-10 09:39:29 0

0 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0 调整电压和温度设置不要求FPGA 实现任何改变,可以提供一个方便的手段增量地改善最坏条件的性能。

2024-03-26 14:32:55 1915

1915

优化FPGA(现场可编程门阵列)设计的性能是一个复杂而多维的任务,涉及多个方面和步骤。以下是一些关键的优化策略: 一、明确性能指标 确定需求 :首先,需要明确FPGA设计的性能指标,包括时钟频率

2024-10-25 09:23:38 1454

1454 本文将首先介绍FPGA的基础知识,包括FPGA的工作原理以及为什么要使用FPGA等,然后讨论设计和执行FPGA应用所需的工具。

2024-11-11 11:29:44 2486

2486

在 AI 赋能工程设计的时代浪潮中,智多晶率先迈出关键一步——智多晶正式宣布旗下 FPGA 设计工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小助!这是 FPGA 领域首次引入大模型 AI 助手,为 FPGA 工程师提供前所未有的智能交互体验。

2025-06-06 17:06:39 1284

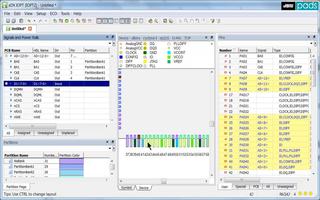

1284 智多晶EDA工具HqFpga(简称HQ),是自主研发的一款系统级的设计套件,集成了Hqui主界面、工程界面、以及内嵌的HqInsight调试工具、IP Creator IP生成工具、布局图、热力

2025-11-08 10:15:31 3423

3423

电子发烧友App

电子发烧友App

评论