深入解析PCA9306:双路双向I²C和SMBus电压电平转换器 在电子设计领域,I²C和SMBus接口的应用极为广泛,而电压电平转换在不同电压域的设备通信中起着关键作用。今天,我们就来深入

2025-12-29 14:45:16 75

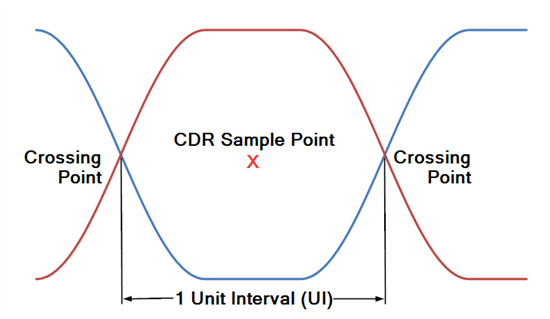

75 深入剖析DS25BR100/101:高速LVDS缓冲器的卓越之选 在高速信号传输领域,找到一款能够确保信号完整性、降低抖动并具备高抗噪能力的缓冲器至关重要。德州仪器(TI)的DS25BR100

2025-12-27 09:25:08 476

476 ,RC38208A - EVK)为工程师们提供了一个评估高性能综合器和抖动衰减器应用的理想平台。今天,我们就来深入了解一下这个评估板。 文件下载: Renesas Electronics

2025-12-26 18:10:03 944

944 深入探究 SN65LVELT23:一款高性能的电平转换器 作为一名电子工程师,在日常的硬件设计中,电平转换是一个常见且关键的环节。今天,咱们就来深入聊聊德州仪器(TI)的 SN65LVELT23

2025-12-25 09:40:16 142

142

电路原理很简单,分两种情况:

1.从A到B

A为高电平时,MOS管关断,B端通过上拉,输出高电平;

A为低电平时,MOS管内的体二极管导通,使MOS管的S极被拉低,从而使Vgs

2025-12-04 06:27:31

。

早期的器件多是TTL电平,如早先的54系列和74系列。现在的大部分器件使用的工艺都是CMOS工艺。

输出电平:高电平Uoh >=2.4v,低电平Uol <= 0.4v

2025-12-03 08:10:03

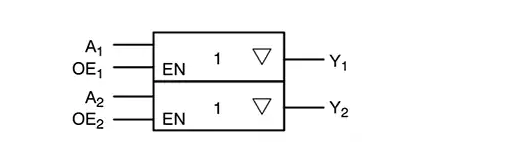

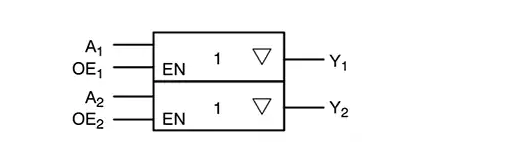

安森美 NL27WZ126 3态高电平使能双路缓冲器是MiniGate™ 高性能双路非反相缓冲器,工作采用1.65V至5.5V电源。高电平使能特性让这些缓冲器可以在使能时提供有源输出,使它们适合

2025-11-25 13:50:46 351

351

瞬间(上升沿/下降沿)、每次跳变仅触发一次中断、需干净跳变(避免抖动)、自动清除(硬件记录边沿事件);

电平触发:持续电平状态(高/低电平)、只要电平维持即持续触发中断、需稳定电平(避免浮动)、必须手动

2025-11-17 06:59:11

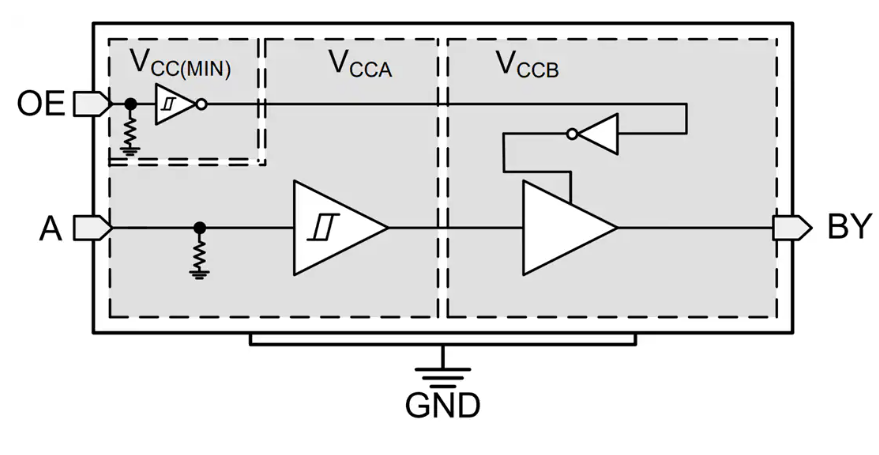

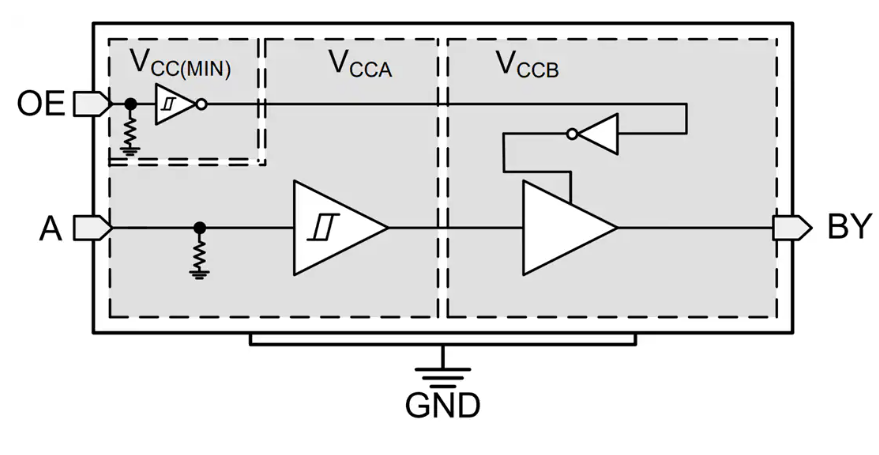

V~CCB~逻辑电平为基准,B引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定方向从

2025-09-16 15:21:50 646

646

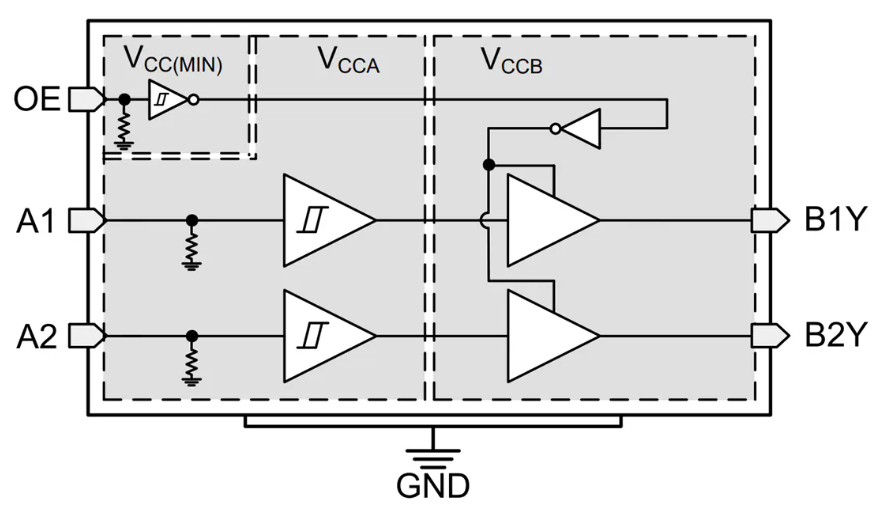

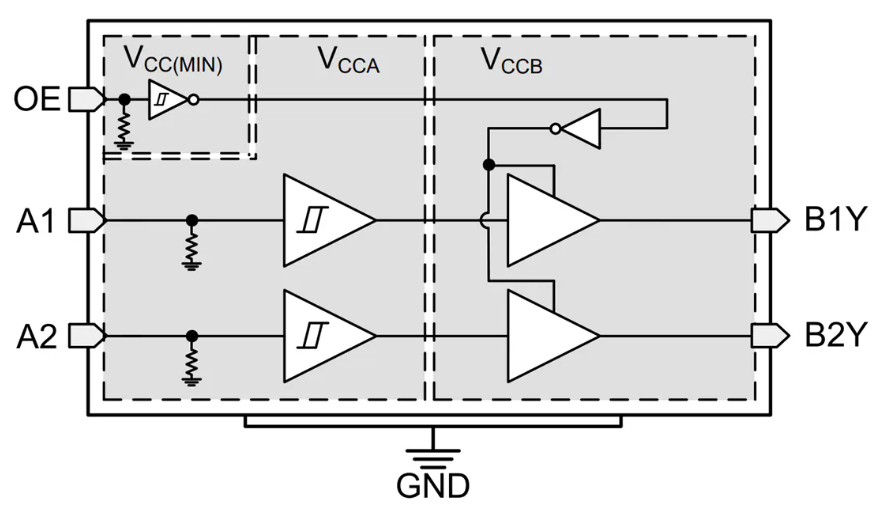

为基准,Bx引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定方向从A传输到B

2025-09-16 14:57:44 635

635

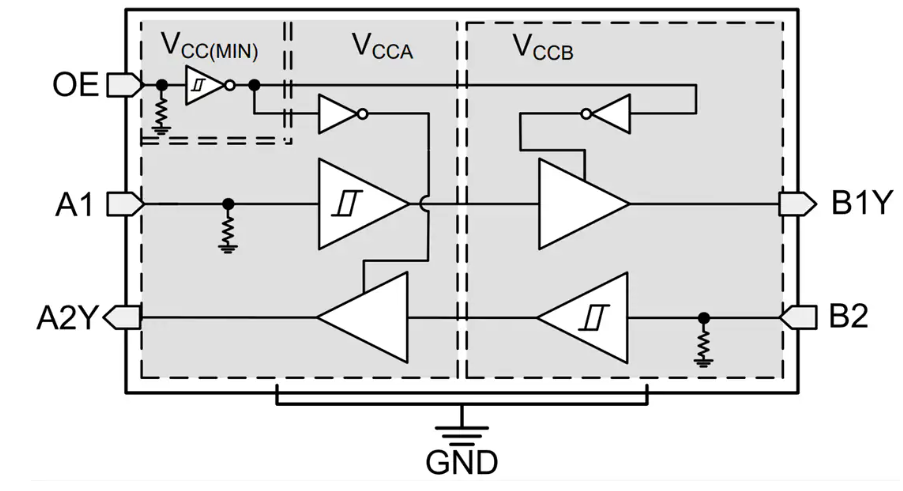

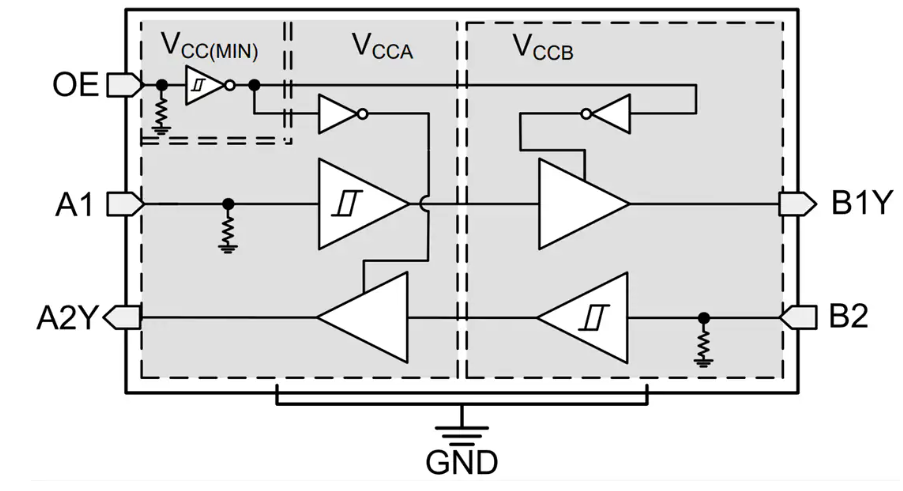

~或V~CCB~逻辑电平为基准,Bx引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定

2025-09-16 14:53:06 620

620

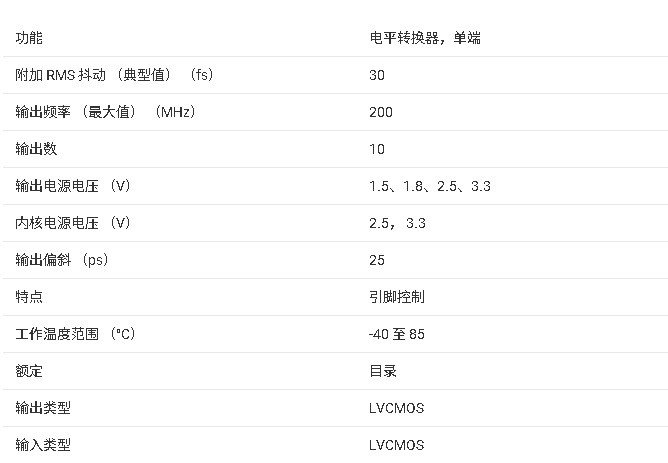

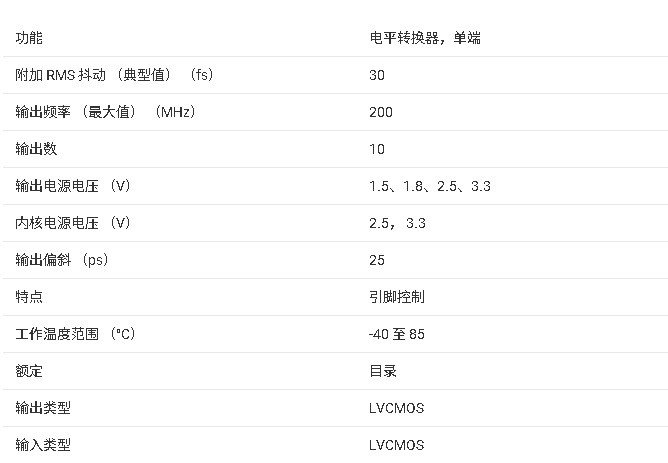

LMK00101是一款高性能、低噪声的LVCMOS扇出缓冲器,可分配 10个来自差分、单端或晶体输入的超低抖动时钟。The LMK00101 支持同步输出使能,实现无毛刺作。超低偏斜、低抖动和 高

2025-09-15 15:41:45 745

745

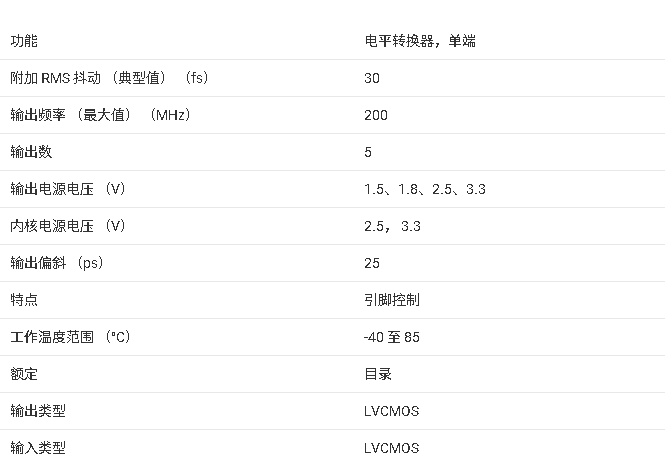

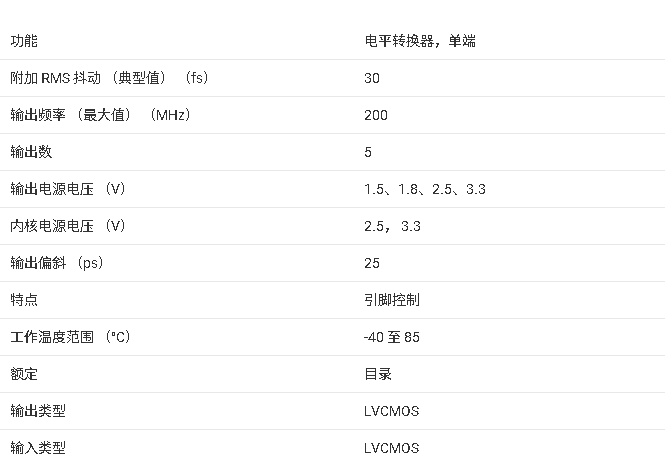

该LMK00105是一款高性能、低噪声的LVCMOS扇出缓冲器,可从差分、单端或晶体输入分配五个超低抖动时钟。该LMK00105支持同步输出使能,实现无毛刺作。超低偏斜、低抖动和高 PSRR 使该缓冲器非常适合各种网络、电信、服务器和存储区域网络、RRU LO 基准分配、医疗和测试设备应用。

2025-09-15 14:12:16 857

857

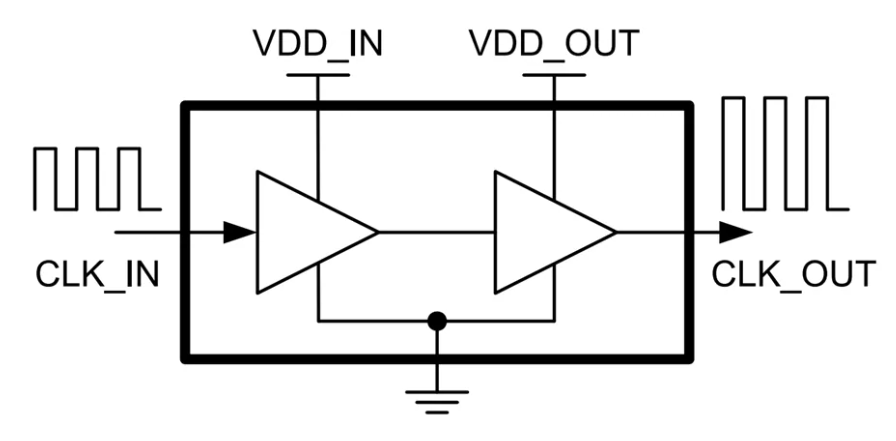

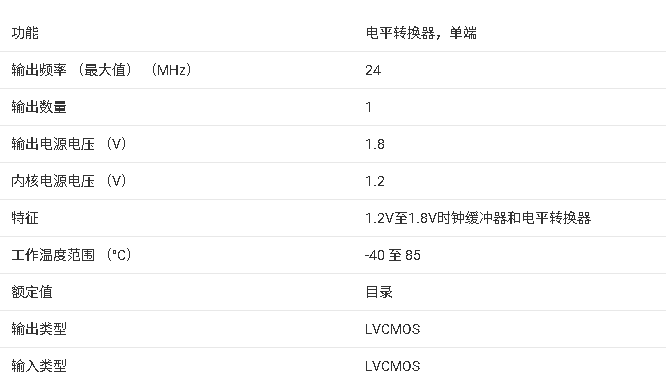

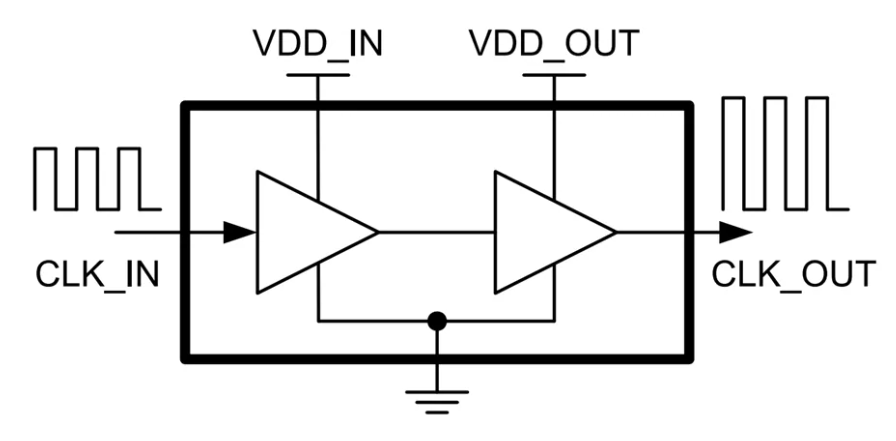

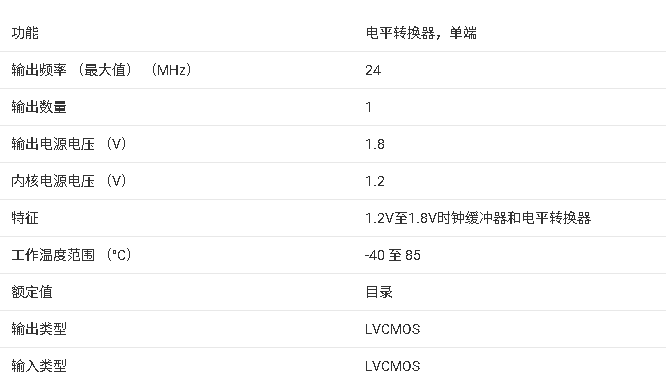

时钟电平。VDD_OUT引脚电源电压定义输出LVCMOS时钟电平。VDD_IN = 1.2V ±10%. VDD_OUT = 1.8V ±10%. Texas Instruments CDCBT1001在24MHz时具有小于0.8ps(12kHz至5MHz)附加RMS抖动。

2025-09-15 11:32:40 676

676

该CDCBT1001是1.2 V至1.8 V时钟缓冲器和电平转换器。VDD_IN引脚电源电压定义输入LVCMOS时钟电平。VDD_OUT引脚电源电压定义输出LVCMOS时钟电平。VDD_IN

2025-09-11 13:54:53 691

691

为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

2025-08-27 15:00:23

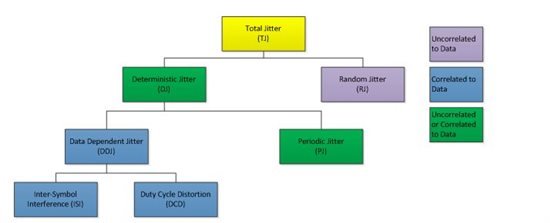

卓越的稳定性,完全消除了传统方案中常见的抖动问题。本文将深入解析FP7122如何实现无抖动、平滑自然的色温过渡。调色温技术面临的抖动问题在LED照明系统中,调色温

2025-08-27 10:51:22

当I/O上电初始配置为准高电平时,需要多少个下拉电阻来保持I/O低电平?

2025-08-26 07:40:32

当I/O上电初始配置为准高电平时,需要多少个下拉电阻来保持I/O低电平?

2025-08-21 07:54:20

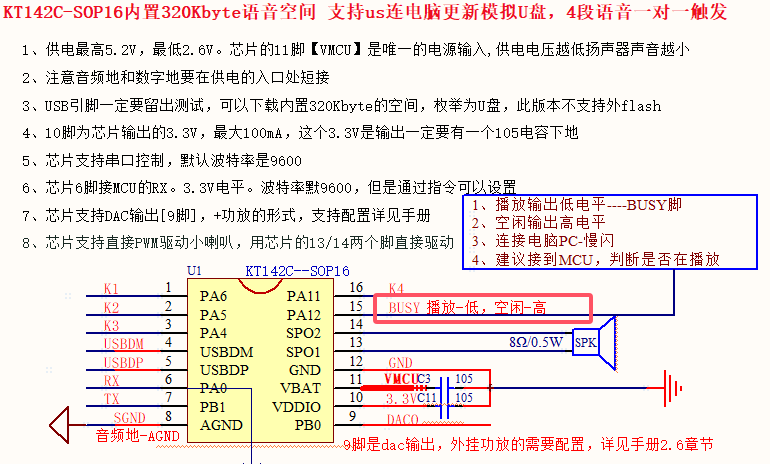

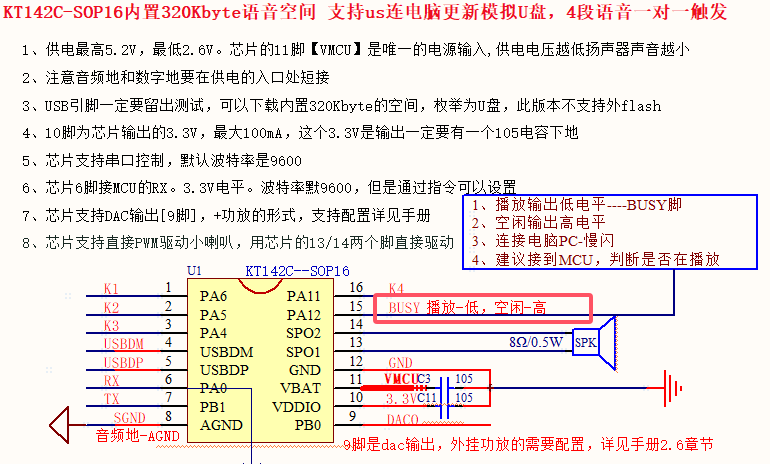

文档围绕 KT142C 芯片 busy 引脚展开,该引脚为 15 脚 PA12,播放时输出低电平,空闲时本应输出 3.3V 高电平,但芯片空闲 5 秒进入 2μA 超低功耗状态后,busy 脚呈高阻

2025-06-16 09:38:26 995

995

电机作为现代工业生产和日常生活中不可或缺的动力设备,其运行稳定性直接影响着整个系统的可靠性。然而,电机在长期运行过程中,常常会出现各种噪音和振动问题,这些问题不仅影响设备性能,还可能缩短电机寿命

2025-06-08 10:25:02 2760

2760 % 左右时,开关电源良好输出变为高电平,开关电流限制增加到 800mA(最小值),此时可以打开更高电流的负载。较高的电流限制提供短路保护,同时允许外设从 USB 总线吸收最大电流。

2025-05-27 17:51:25 584

584

原理分析 当输入端3.3V为低电平时,D1导通,输出端 1.8V为低电平,实现两端都为低电平。当输入端 3.3V为高电平时,D1截止,输出端被 R1 上拉至 1.8V ,为高电平,实现两端都为高电平。 二

2025-04-27 15:54:19

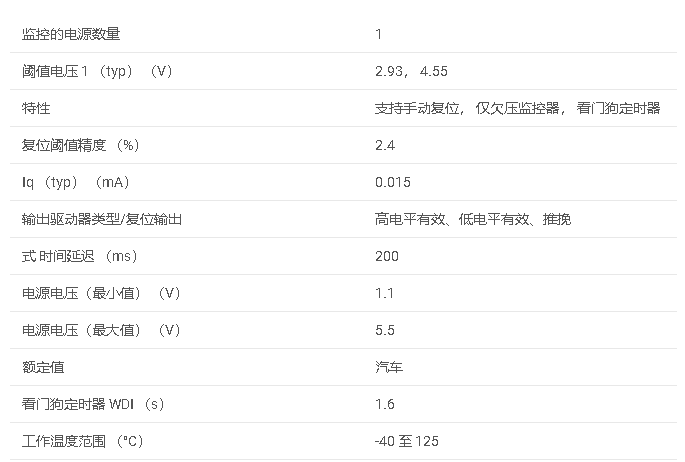

DS1232LPS-2+T&R,这款芯片在什么情况下,5脚RST会一直输出高电平?(正常时序是上电有个400多ms的高电平后,一直处于低电平,如果7脚没有及时喂狗,会触发复位,也就是重复400多ms的高电平后,一直处于低电平)

2025-04-18 07:51:16

液压技术讨论

2025-04-14 16:50:40 0

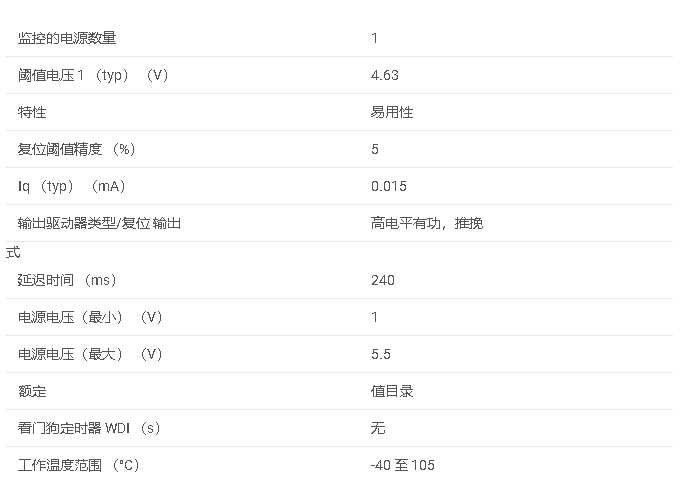

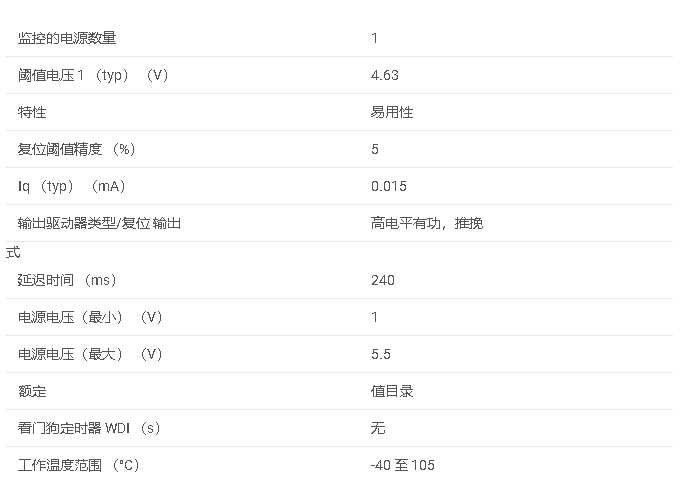

0 ,并在此电压降至工厂编程的电压以下时触发复位信号 reset 阈值。复位信号在 V 后保持 240 ms~抄送~上升到阈值以上。LM809 具有 /RESET 输出,而 LM810 具有高电平有效 RESET 输出。

2025-04-12 15:17:58 789

789

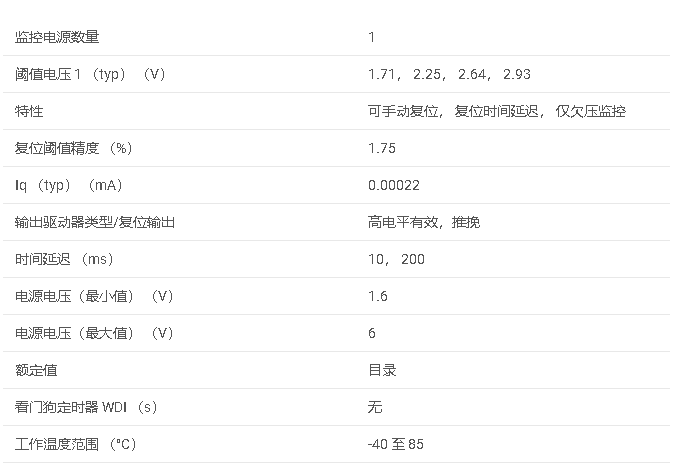

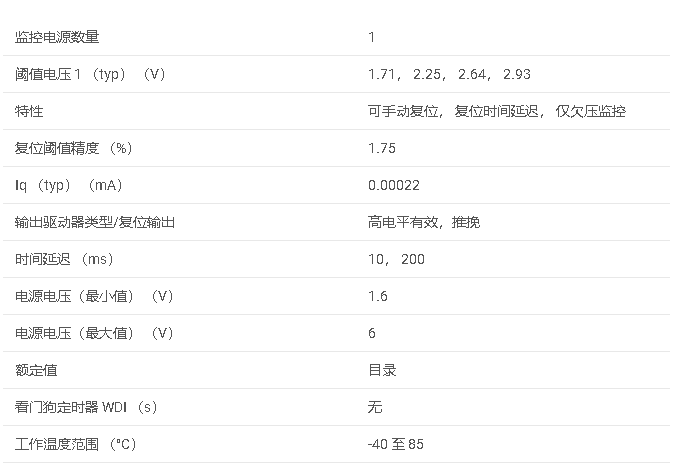

1.1 V。此后,监控电路监控 V DD 系列 并保持 RESET 输出有效,只要 V DD 系列 保持在阈值电压 V 以下 它 .一个内部定时器延迟输出返回到非活动状态 (高电平),以确保系统正确

2025-04-12 15:02:31 765

765

阈值电压 VIT− 以下,电源电压监控器就会监控 VDD 并保持 RESET 低电平。内部定时器延迟输出返回到非活动状态 (高),以验证系统复位是否正确。延迟时间 td 在 VDD 上升到阈值电压 VIT - 以上后开始。当电源电压降至阈值电压 VIT− 以下时,输出再次变为有效 (低电平)。

2025-04-11 18:01:11 807

807

用最右边的字符下划线代表低电平有效,高电平有效的信号不得以下划线表示,短暂的有效信号建议采用高电平有效。

2025-04-11 09:36:34 946

946 问题1:IO拓展芯片PCAL9722的P1_7引脚设置为上拉输入读取不到正确电平,默认读取到为1高电平,但是当我给低电平时,读取到的依然是1高电平(通过万用表测量该引脚确为低电平);

问题2:当设置

2025-04-01 06:11:18

我使用GPIO_AD_00生成 PWM 信号,并且工作正常。但是当我在 RT1170 中执行 POR作时。然后 PWM 引脚变高,直到电路板启动。启动后,它按预期生成 PWM 信号。但我不希望 PWM 引脚在执行 POR 时变为高电平,直到电路板启动。您能否就此问题帮助我。

2025-03-31 08:22:04

我遇到了一个问题,即 Chip Select (CS) 在大约 5 μs 内保持高电平。

最初,在使用 DMA 时,我观察到在 SCLK (串行时钟)开始之前,CS 低电平时间延长了约 2.2 μs

2025-03-31 06:56:37

类似TTL和CMOS区别的基础面试题1,TTL电平:输出高电平>2.4V,输出低电平=2.0V,输入低电平Vih,输入低电平Vih>Vt>Vil>Vol。6:Ioh:逻辑门

2025-03-26 19:32:54 1786

1786

一、电平规范 1、名称解释Uoh -> 输出高电平,Uol -> 输出低电平;Uih -> 输入高电平,Uil -> 输入低电平。2、TTL

2025-03-22 15:21:36

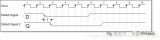

边沿检测经常用于按键输入检测电路中,按键按下时输入信号 key 变为低电平,按键抬起变为高电平。当输入的信号为理想的高低电平时(不考虑毛刺和抖动),边沿检测就发挥了很重要的作用。

2025-03-19 11:47:15 1213

1213

本篇文章将深入解析 FCom 低抖动可编程 VCXO 的特点、常用频率及其在光纤通信、5G 基站、数据中心、以太网、汽车电子、工业自动化、广播电视等应用中的作用,帮助工程师和采购人员选择最适合的高性能 VCXO 方案。

2025-03-13 08:00:00 1048

1048

= GPIO_PuPd_UP;函数无法拉高IO,必须要GPIO_SetBits(GPIOA,GPIO_Pin_5);来拉高电平,导致我上电瞬间LED会闪一下,这种体验很不好

2025-03-11 07:15:58

trigger out信号一直是高电平,投射pattern时也没有变化,不能起到触发的效果

2025-03-03 07:21:04

DLPC350上电后DMD_PWR_EN始终为低电平测试芯片电压正常,请问这个管脚电平在什么情况下高?电路是根据官方参考自己做的。PWRGOOD和POSENSE都为高电平。

2025-02-27 06:32:31

DLPC4100输出的RST_ACTIVE信号为高电平时,User FPGA无法抓到这个高电平,是什么原因导致的呢(管脚分配正确)?

2025-02-26 06:28:56

dlpc3438无法启动,HOST_IRQ一直高电平, 芯片:DLPC3438+DLPA2005+DLP3010

flash是用的w25q64

固件下载的是dlpc3433/8,DLPA2005

2025-02-24 06:04:33

您好,我在使用THS1206,AVDD=5V,BVDD=DVDD=3.3V;

输入时钟为3MHZ,和FPGA进行连接;

测试data_av信号输出的高电平和低电平都是mv级别的,请问是什么情况呢?

2025-02-14 08:25:17

数据手册看了好几遍,关于ADS1278的SYNC引脚使用还是不很明白。想问下,如果我不用这个引脚的话,可以一直上拉到高电平吗?还有看到如果把他接低电平,AD就停止转换,接到高电平后就恢复转换,这样的话,我可以把他当成一个启动停止转换的开关吗?希望指点。。。谢谢

2025-02-14 06:57:55

在ADS1278上电后,SCLK没给波型(一直是高电平),为什么DOUT会一直出来波形?很不解。不是说DOUT只在SCLK有波形输入的时候才会输出波的吗

2025-02-14 06:22:28

我参考电压和供电电压都是3.3V,AIN+接2V,AIN-接地,CS线和SLK接STM32端口,电路图和datasheet给的是一样的,对照时序图写的程序,但是我SDO端输出的全部是高电平。不知道

2025-02-13 07:08:59

使用ADS1240时,写数据时序输入正常。但DRDY 总是高电平,读不到数据。

2025-02-12 06:48:57

发送指令RDATAC后,为何DRDY引脚一直为高电平?是什么原因呢?

2025-02-11 06:08:41

专家们好 刚刚接触ADS1258 有问题需要请教 ADS1258采用SPI通信 根据pdf 我下面的发送命令的时序时序是否正确?如果正确的话 为什么GPIO引脚不能根据我的设置为高电平?我采用

2025-02-10 08:34:39

我把TS3A5017的2个EN引脚通过10K的电阻接地,为什么这2个引脚仍然是高电平

2025-02-10 07:54:52

我现在用LPC2103与ADS1251通讯,但是通讯不上,ADS1251的DOUT引脚电压一直是高电平?不知道什么原因

2025-02-10 06:53:51

我想问一下ADS1298如果使用寄存器命令RESET去复位,那么其RESET管脚是接高电平还是低电平,还是悬空

2025-02-10 06:00:14

我msp430F6638来控制ADS1298R,1298R的sclk、din和dou等t直接连接到430相应SPI的管脚。 我在观察430的spi输出数据时发现,逻辑正确,但是高电平被拉到1V左右

2025-02-08 07:27:54

参照ADS1293 PDF资料Figure 34. 8-12-Lead ECG Application 原理和寄存器设置,设置寄存器读写没有问题,但启动ADC转换后,DRDYB管脚一直为高电平

2025-02-06 08:15:50

手册上说DRDY会在SCLK的下降沿自动变成高电平(DRDY s pulled high at the falling edge of SCLK),但为什么我做了几次后发现DRDY并没有自动变成高电平,而是一直维持在低电平。

2025-02-06 07:14:10

clk和sclk时钟发现DRDY上有数据转换完成的脉冲生成,但是焊接上opa1632后发现opa工作正常,但ADS1274的DRDY一直高电平了,再去掉opa1632及外围电路,ADS1274的DRDY

2025-02-06 07:07:12

ADS7864 上电之后是不是BUSY 脚为高电平(没有开启转换)? 为什么我的ADS7864的BUSY 一直是低电平呢?是硬件问题?

2025-02-06 06:33:17

用单片机硬件通信ADS1248 对寄存器可操作,读写均正确。只能偶尔读到AD的值,用示波器测量各引脚单次读值时START 脚有100us的上升沿脉冲,连续读值时START为高电平,CS口始终为

2025-02-06 06:18:05

在电子电路中,上拉电阻起着非常重要的作用,其工作原理基于基本的电学定律,主要用于在特定的电路场景下将信号电平拉高。 首先,需要了解电路中的电平概念。在数字电路中,信号电平通常分为高电平和低电平,它们

2025-02-05 17:40:00 1455

1455

手册中关于SYNC的描述是:SYNC低电平时使能输入移位寄存器,SYNC需要保持低电平到接收玩24个SCLK周期才能更新DA输出,如果没到24个SCLK周期就变为高电平,输入移位寄存器将复位。

我

2025-02-05 09:31:01

请问一下,DRDY在上电之后,也就是初始化后,是保持高电平还是低电平?在传送指令结束后,是不是会自动跳为高电平?麻烦用过ADS1211的给说一说,并且在用的过程中要注意的问题给我讲一下,在这里先谢谢大家啦!

2025-02-05 09:26:39

与ADS8323的时钟引脚断开,示波器测量CPLD输出的时钟高电平为3.3v,连接上后只有1v,片子是不是坏了??

2025-02-05 07:40:13

。 使用示波器的垂直灵敏度(Volts/Division)和水平时间(Time/Division)旋钮调整显示范围,使得信号稳定地显示在屏幕上。 连接探头 : 将示波器的探头连接到TTL信号输出端,注意探头的地线接示波器的地端,以确保测量的准确性。 测量高电平和低电平 : 在垂直方向上,使用

2025-01-31 10:05:00 2715

2715 ) AND门 :只有当所有输入都为高电平时,输出才为高电平。 OR门 :只要有一个输入为高电平,输出就为高电平。 NOT门 (反相器):输出是输入的反相。 NAND门 :AND门的反相。 NOR门 :OR门的反相。 XOR门 (异或门):当输入不同(一个高电平,一个低电平

2025-01-24 09:40:33 1647

1647

1示波器显示电源.输入3.3V电压正常。

2.示波器显示CLK口方波输入正常

3.单片机用的是M4的SPI接口。

4.下面付的是出事化代码。

问题:DOUT/DRDY引脚一直高电平,SCLK引脚

2025-01-24 08:17:59

大家好,我在使用TLC7524做数模转换,在上电的一瞬间有接近100ms的最高值电压输出。如果将WR脚用1K电阻拉到地(此引脚未连接其他电路),则时间缩短至1ms以内,但仍然无法彻底消除。请问有什么好方法可以去除上电高电平输出,以下是原理图:

2025-01-24 07:32:47

根据手册,当检测到错误状态时,ALARMB引脚电平会被拉低的。

该ALARMB引脚外接上拉电阻,默认情况(没有开启LOD功能)输出为高电平。

但是一开启LOD功能,使能LOD_CN寄存器,也设置了

2025-01-23 07:32:26

ADS上电,DOUT/DRDY总是高电平,一直为高电平,多插几次电源,偶尔能正常启动DOUT/DRDY有正常的下降沿。

到底是怎么回事?

下面是启动顺序:

InitSPI3SEL();//设置

2025-01-23 07:01:19

adc08d1020的所有控制线(1.9V电平)接入xilinxV5芯片 电平为3.3V的IOBANK,现板子已做好,没有办法换FPGA的IO电平。

控制线有三种:

1)可以直接接高电平(1.9v

2025-01-22 08:20:59

我在AVDD为5V,DVDD为3.3V,工作频率为25M,SCLK为6.25M,Frame_Sync模式的情况下使用ADS1271,模拟输入端为零时输出数据的高几位(大概是D23到D12)为什么总是高电平?理论上只有最高位才有可能是高电平的么。

2025-01-17 06:23:00

TTL电平是一种数字电路中使用的电压标准,它定义了逻辑电平的高低状态。TTL电平的特点是: 电压范围 :TTL电平的高电平(逻辑1)通常在2.4V到5V之间,而低电平(逻辑0)则在0V到0.8V之间

2025-01-16 10:34:04 1134

1134 在电子工程领域,信号电平的转换是一个常见的需求,尤其是在不同技术标准之间。TTL(晶体管-晶体管逻辑)电平和高电平信号是两种不同的电平标准,它们在电压水平和应用场景上有所不同。 TTL电平的定义

2025-01-16 10:28:42 1597

1597 定了高电平和低电平的具体范围。在计算机处理器控制的设备内部的数据传输中,TTL电平信号是理想的,其电平标准通常如下: 输出高电平(H):大于2.4V,典型值为3.5V(室温下)。 输出低电平(L):小于0.4V,典型值为0.2V(室温下)。 输入高电平(VIH):

2025-01-16 10:26:58 2323

2323 晶体管来实现逻辑门的功能。TTL电平因其简单、可靠和成本效益高而在嵌入式系统中得到了广泛的应用。 TTL电平的定义和特性 TTL电平是一种数字信号电平标准,它定义了高电平和低电平的具体电压值。在TTL电平中,一个逻辑“1”(高电平)通常对应于2.4V到5V的电压范围,而一个逻辑“

2025-01-16 10:22:31 1653

1653 在数字电子学中,信号的传输和处理依赖于电压水平来表示逻辑状态。TTL电平和低电平信号是两种常见的电压水平,它们在数字电路中扮演着重要的角色。 TTL电平 TTL电平是一种广泛使用的数字逻辑标准,由

2025-01-16 10:21:08 2014

2014 挥着重要作用。 TTL电平简介 TTL电平是一种数字电路的电压标准,它基于晶体管-晶体管逻辑(TTL)技术。TTL电平通常使用5V供电,其逻辑“0”(低电平)约为0.8V,逻辑“1”(高电平)约为2.4V。这种电平

2025-01-16 10:13:33 1513

1513 电平是一种双极型晶体管逻辑电平,它由两个晶体管构成,一个是输入晶体管,另一个是输出晶体管。TTL电平的标准电压定义如下: 低电平(逻辑0):电压范围在0V到0.8V之间。 高电平(逻辑1):电压范围在2.0V到5V之间。 这些电压范围确保了数字信号的清晰

2025-01-16 09:56:25 3456

3456 逐渐成熟,并成为数字电路设计中的一个标准。 TTL电平标准的定义 TTL电平标准定义了数字信号的高低电平电压范围。在TTL电平标准中,高电平(逻辑1)通常定义为2.7V至5V,而低电平(逻辑0)则定义为0V至0.8V。这些电压范围确保了数字信号的清晰区

2025-01-16 09:46:44 3502

3502

ads1256的drdy引脚(数据准备输出)的高电平应该是多少?我用示波器测得只有300毫伏左右,这个值是器件初始化没有成功么?我看数据手册上应该上电复位完成后drdy就应该有输出呀。但是300毫伏对于F28335来说应该捕捉不到吧。

2025-01-15 08:19:08

我把MODE接高电平 FORMAT接地工作在SPI低功耗模式下。当PDWN管脚接高电平时,发现RDRY、DOUT管脚均有波形输出。

请问:

1、当PDWN管脚为高电平时,ADC转换就启动了;

2

2025-01-15 07:00:21

ADS7815数据输出端口在转换的期间为三态,转换完成后为高电平或低电平,但为什么我使用的时候,数据端口输出比较混乱,即使被采样信号为0,输出端口也会有高电平

2025-01-14 07:58:18

请问大家有没有用试过用ADS1234 的时候DOUT一直为高电平,无论DVDD设置5V还是3.3V, DOUT一直输出是3.3V,

PDWN脚是通过MCU控制,MCU是C8051F系列的。

在线等待回复,万分感谢。

2025-01-13 08:21:40

示波器通道1监测输入通道A(input)一直为高电平,高电平时偶尔有干扰,但是示波器通道2监测输出通道A(output)由高电平变为了低电平。而低电平的脉宽在2us~17us不等,请大神们解答

2025-01-13 06:52:06

dac8571采用高速模式,并且也有应答信号,但是输出为什么始终为高电平?

2025-01-10 16:04:11

dac8571采用高速模式,并且也有应答信号,但是输出为什么始终为高电平?

2025-01-10 09:42:35

我现在在调试ADS8684,但是ADC的输出引脚的波形在最后一个高电平会拖很长的尾巴, 这个不知道怎么回事?我拍了照片,上面的是CLK波形, 下面的是OUT波形。另外,ISO7641在输入信号

2025-01-09 08:21:29

最近一个周用FPGA写一个读取一个ADS1271数据的程序。按照芯片手册上的初始化的理解,我先将SYNC_N用引脚拉低500个时钟周期,然后再将其拉高。可是DRDY_N一直是高电平,未能使能输出数据。请问这是由于初始化的脉冲宽度小了么?还是根本就是我的理解有错误。

2025-01-09 07:36:48

TLV1544的EOC输出始终是高电平,输入其他端口的信号都是对的,是怎么回事,是芯片换了吗?这个芯片应该可以用51单片机来控制吧?

2025-01-08 06:28:45

用示波器量晶振没启振,硬件电路确定是好的(已经仔细检查很多遍了),电源也是正常的。DRDY一直是高电平,什么原因呢

2025-01-06 06:25:16

电子发烧友App

电子发烧友App

评论