RAM是随机存取存储器也叫主存,是与CPU直接交换数据的内部存储器芯片。它可以随时读写(刷新时除外),而且它的速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,便是一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。

随机存取存储器(ram)既可向指定单元存入信息又可从指定单元读出信息。任何RAM中存储的信息在断电后均会丢失,所以RAM是易失性存储器。

特点

随机存取

所谓“随机存取”,指的是当存储器中的数据被读取或写入时,所需要的时间与这段信息所在的位置或所写入的位置无关。读取或写入顺序访问(Sequential Access)存储设备中的信息时,其所需要的时间与位置就会有关系。它主要用来存放操作系统、各种应用程序、数据等。

当RAM处于正常工作时,可以从RAM中读出数据,也可以往静态RAM中写入数据。与ROM相比较,RAM的优点是读/写方便、使用灵活,特别适用于经常快速更换数据的场合。

易失性

当电源关闭时的RAM不能保留数据。如果需要保存数据,就必须把它们写入一个长期的存储设备中(例如硬盘)。

RAM的工作特点是通电后,随时可在任意位置单元存取数据信息,断电之后内部信息也随之消失。

对静电敏感

正如其他精细的集成电路,随机存取存储器对环境的静电荷非常敏感。静电会干扰存储器内电容器的电荷,引致数据流失,并且会烧坏电路。因此在触碰随机存取存储器前,应先用手触摸金属接地。

访问速度

现代的随机存取存储器几乎是所有访问设备中写入和读取速度最快的,存取延迟和其他涉及机械运作的存储设备相比显得微不足道。

需要刷新(再生)

现代的随机存取存储器依赖电容器存储数据。电容器充满电后代表1(二进制),未充电的代表0。由于电容器或多或少有漏电的情形,若不作特别处理,数据会随时间渐渐流失。刷新则是指定期读取电容器的状态,然后按照原来的状态重新为电容器充电,弥补了流失的电荷。需要刷新正好解释了随机存取存储器的易失性。lw

ram是什么

- RAM(119992)

- 易失性存储器(6840)

- 随机存取存储器(9273)

相关推荐

热点推荐

电子工程师必备:探秘FM25L16B 16 - Kbit串行F - RAM

电子工程师必备:探秘FM25L16B 16-Kbit串行F-RAM 在电子工程师的日常设计工作中,选择一款合适的非易失性存储器至关重要。今天我们就来详细了解一款性能卓越的产品——FM25L16B

2026-01-05 16:25:25 29

29

29

29FM25V10 1-Mbit 串行 F-RAM 芯片的特性与应用解析

FM25V10 1-Mbit 串行 F-RAM 芯片的特性与应用解析 在电子设计领域,找到一款性能卓越、功能丰富且稳定可靠的非易失性存储器至关重要。今天,我们就来深入探讨 Cypress 公司推出

2026-01-04 17:25:09 367

367

367

367探索FM24V05:高性能I²C F - RAM的卓越之选

探索FM24V05:高性能I²C F - RAM的卓越之选 在电子设备设计中,存储器的选择至关重要,它直接关系到系统的性能、可靠性和使用寿命。今天,我们将深入探讨一款出色的串行存储器

2025-12-31 16:40:23 727

727

727

727FM25L04B:高性能4-Kbit串行F-RAM的卓越之选

FM25L04B:高性能4-Kbit串行F-RAM的卓越之选 在电子设计领域,非易失性存储器的选择至关重要,它直接影响着系统的性能、可靠性和使用寿命。今天,我们来深入了解一款备受关注的产品

2025-12-31 16:05:18 85

85

85

85显存读写冲突造成花屏解决方案

.

TE信号从TFT控制器发出, 告诉MCU,现在“开始”从第一行开始读RAM并显示了~

目标是避免TFT控制器读取RAM数据时, MCU却在往同一位置写数据所造成的冲突,

详细说明:

举例:

&

2025-12-29 09:07:56

FM24V02A:高性能串行F - RAM的卓越之选

FM24V02A:高性能串行F - RAM的卓越之选 在电子设计领域,非易失性存储器的选择至关重要,它直接影响着系统的性能、可靠性和使用寿命。今天,我们就来深入探讨一款高性能的串行F - RAM

2025-12-28 15:25:09 404

404

404

404探索FM25L16B:高性能16-Kbit串行F-RAM的魅力

探索FM25L16B:高性能16-Kbit串行F-RAM的魅力 在电子设计领域,寻找一款高性能、可靠且耐用的非易失性存储器是许多工程师的追求。今天,我将带大家深入了解一款令人瞩目的产品

2025-12-23 15:55:09 139

139

139

139CW32在不同复位方式对应的复位范围

上电复位 / 掉电复位(POR/BOR)

整个 MCU

引脚输入复位(NRST)

整个 MCU(除 RTC 外)

IWDT/WWDT 复位

M0+ 内核 / 外设(除 RAM 控制器

2025-12-22 09:44:23

Infineon SEMPER NOR Flash与HYPERRAM™ 2.0 Gen2 Flash+RAM MCP产品解析

Infineon SEMPER NOR Flash与HYPERRAM™ 2.0 Gen2 Flash+RAM MCP产品解析 引言 在汽车集群和工业HMI应用中,通常会使用NOR Flash来存储

2025-12-20 16:20:02 1044

1044

1044

1044XC7Z020-2CLG484I, 双核ARM Cortex-A9处理器, 现货库存

相当规模的FPGA逻辑资源,包括278,624个逻辑单元、36个18x18位的DSP48E1乘法器、2个块RAM(Block RAM)以及大量的分布式RAM和移位寄存器

2025-12-15 16:54:02

Amphenol 38999 Ram-Lock 推拉接口连接器:设计与应用指南

Amphenol 38999 Ram-Lock 推拉接口连接器:设计与应用指南 在电子设备的设计中,连接器的选择至关重要,它直接影响到设备的性能、可靠性和易用性。今天,我们来深入了解一下

2025-12-11 10:55:16 290

290

290

290FM24CL04B:4-Kbit串行F-RAM的卓越性能与应用解析

FM24CL04B:4-Kbit串行F-RAM的卓越性能与应用解析 在电子工程领域,非易失性存储器的选择对于系统的性能和可靠性至关重要。今天,我们将深入探讨FM24CL04B这款4 - Kbit

2025-12-10 17:15:02 1628

1628

1628

1628

单片机堆栈解析

什么是单片机堆栈?

在片内RAM中,常常要指定一个专门的区域来存放某些特别的数据,它遵循顺序存取和后进先出(LIFO/FILO)的原则,这个RAM区叫堆栈。

它的作用

子程序调用和中断服务时CPU

2025-12-09 06:52:13

FreeRTOS任务和协程的区别是什么

1.堆栈 协程是没有堆栈分配的,是所有创建的协程共同使用一个堆栈空间,这相比于任务来说,减少了RAM的使用空间。 2. 调度和优先级 协程使用协同调度,但是可以包含在使用的抢占优先级之中。

3. 宏

2025-12-08 08:18:48

ucos与freertos哪个好?

选择uCOS或FreeRTOS取决于项目的具体需求和资源限制。

FreeRTOS的优点包括:

更小的内核ROM和RAM占用,特别是在RAM方面,适合资源受限的嵌入式系统。

支持协程

2025-12-05 07:13:39

MCU代码需要搬到RAM中才能运行吗?不这样做会有什么不妥嘛?

大部分单片机的代码直接在nor flash中运行,少部分需要加载到ram中。

nor flash可以直接寻址一个字节,可以找到一个指令的具体地址,因此可以直接运行。

nand flash 的存储单元

2025-12-04 07:39:27

单片机程序的执行

。

但是单片机上只有几K的RAM,而flash一般有几十K甚至1M,这个时候指令和数据都在内存中吗(这里指的内存仅指RAM,因为PC上我们常说的内存就是DDR RAM memory,先入为主以至于认为

2025-12-04 06:20:08

芯源MCU的RAM存储器的操作

用户可执行的RAM 存储器操作包括:读操作、写操作。

对RAM 的读写操作支持8bit、16bit 和32bit 三种位宽,用户程序可以通过直接访问绝对地址的方式完成读写,

但要注意读写的数据位宽

2025-11-21 07:46:52

2.4G射频芯片XL2417D系列 内置ram核32位主控 128k/flash,8k/ram

和8KB的RAM。XL2417D的工作电压范围为1.7~3.6V,在Tx和Rx模式下功耗极低,射频接收电流10.2mA,发送电流9.5mA。XL2417D抗干扰能力强,接收性能优秀。 XL2417D 芯片

2025-11-13 15:55:09 328

328

328

328CW32的ADC视线,DMA扩展采样思路

的 CH1 用于将 ADC 的转换结果传输到 RAM 中,如将采样 6 个 ADC 通道,因此传输次数 CNT为 6,源地址固定为 ADC 的 RESULT0 寄存器,目的地址需要递增;

3.DMA

2025-11-13 08:09:15

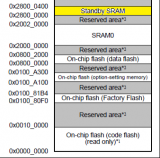

GD32VF103 没有Backup RAM 和 Data Flash这样的区域嘛?

刚开始接触risc-v单片机,感觉GD32VF103还不错,还买了rv-star开发板打算学习一下。我在datasheet上看到了DataFlash没有,但没看到backup Ram(reset后RAM里的数据不丢失)的区域定义,

问一下,没有backup Ram这样的区域嘛?

2025-11-07 06:58:59

make upload报错怎么解决?

set_command_timeout_sec.

Error: Debug interrupt didn't clear.

Error: Debug RAM 0x0: 0xfff04493

2025-11-06 07:29:38

使用J-Link Attach NXP S32K3导致对应RAM区域被初始化成0xDEADBEEF

在IAR Embedded Workbench for Arm中使用J-Link Attach NXP S32K3的时候,会提示对应RAM区域被初始化成0xDEADBEEF,导致对应RAM区域的数据被“篡改”。

2025-11-03 15:26:41 5052

5052

5052

5052

双口ram的使用方法

单口 RAM 只有一个时钟(clka)(时钟上升沿到来时对数据进行写入或者读出)、一组输入输出数据线(dina & douta)、一组地址线(addra)、一个使能端(ena

2025-10-29 06:28:42

芯来e203移植开发分享(二)——仿真文件简述与itcm固化程序

,其实就是把rv32ui-p-add.verilog中16进制文件加载到itcm的ram中,需要主要的itcm中的ram是64bit宽度,.verilog的文件是由$readmemh读上来的8bit

2025-10-27 06:04:31

ITCM扩容教程 & xxx.elf section `.bss\' will not fit in region `ram\'解决办法

; will not fit in region ram解决办法

一, xxx.elf section .bss' will not fit in region ram报错原因

1.这种情况一般是你

2025-10-24 12:46:00

Xilinx BRAM IP核配置及其例化

首先在IP catalog中搜索 BRAM ,点击BRAM GENERATOR。

接口方式有五种,一般使用simple dual port ram

Simple Dual Port RAM,简单双

2025-10-24 06:10:15

e203_dtcm_ctrl模块分析

。

output [32-1:0] ext2dtcm_icb_rsp_rdata:外部代理输入到 DTCM 的总线通道的读取数据。

此模块还提供了控制 DTSM RAM 的接口,包括 dtcm_ram

2025-10-24 06:05:15

ram ip核的使用

1、简介

ram 的英文全称是 Random Access Memory,即随机存取存储器, 它可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据, 其读写速度是由时钟频率

2025-10-23 07:33:21

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

ram的IP就可以

2. 将机器指令初始化到ITCM的bank-ram-IP

生成的机器指令在这里

然后我们需要把它转化为coe文件

我们参考网上的相关代码,做了hex到coe的转换,核心代码实现如下:

读取hex:

生成coe:

3. 然后就可以仿真啦

2025-10-21 11:08:55

国产DSP-QXS320F280049开发板

– 1MB FLASH (ECC 保护) – 1MB SRAM(ECC保护/奇偶校验保护) • 1MB 指令RAM,512KB 数据RAM • 时

2025-10-15 16:29:50

DP8570A 定时器控制外设技术手册

看起来像一个连续的内存或 I/O 端口块。地址空间组织为 2 个 32 字节的软件可选页面。这包括控制寄存器、时钟计数器、报警比较 RAM、定时器及其数据 RAM 以及省时 RAM。任何未用于其预期目的的 RAM 位置都可以用作通用 CMOS RAM。

2025-10-08 10:20:00 620

620

620

620

如何在RTT Studio中像Keil中一样定义一个RAM区域,并该区域RAM上电复位是不会被初始化的(sct分散加载)?

在keil中可以设置一个ram的区域,存放于该区域的数据上电或复位是不会初始化的,在kei中的操作以及生成的sct文件如下:

在IAR中通过icf文件也是可以实现上述划分定义的。

那么在RTT Studio中如何实现?

2025-09-29 06:49:33

USB读RAM buffer使用规范建议

Questions:硬件和软件同时去访问 USB RAM buffer 造成数据乱掉或丢失 造成乱码流程:

软件设置 USB Valid

关总中断,USB 收数据到 RAM Buffer,此时

2025-09-22 17:27:34

关于“随机存取存储器(RAM)”的基础知识详解;

【博主简介】 本人系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵,如有需要可看文尾联系方式,当前在网络平台上均以“ 爱在七夕时 ”的昵称为ID跟大家一起交流学习! 一提到“存储器”,相信很多朋友都会想到计算机。是的,在计算机的组成结构中,有一个很重要的部分,就是

2025-09-19 11:04:07 1443

1443

1443

1443

env生成的gd32H759IM MDK5工程,出现烧写错误怎么解决?

icf文件修改了flash和ram大小

/*-Editor annotation file-*/

/* IcfEditorFile="$TOOLKIT_DIR

2025-09-15 06:37:34

N9H30如何从SPI闪存将应用程序加载到RAM地址0x0?

无法利用 uboot 从 SPI 闪存0x0将应用程序加载到 RAM 地址。SF 读取0x0 0x100000 0x700000这是 uboot 限制

2025-09-01 06:06:06

如何在 nuc980 上切换到持久文件系统?

我遵循了“NUC980 Linux 4.4 BSP 用户手册EN.pdf”文档,但当我尝试取消选择“初始 RAM 文件系统和 RAM 磁盘 (initramfs/initrd) 支持

2025-08-29 07:58:01

如何使TC1796运行在RAM?

Hello,我目前正在寻找一种方式,能让我的代码运行在TC1796的RAM上,请问有人能帮助我吗?

IDE环境:HighTec

调试环境:UDE

硬件环境:Triboard-TC1796B

代码

2025-08-13 07:26:38

嵌入式系统中,FLASH 中的程序代码必须搬到 RAM 中运行吗?

嵌入式系统里,FLASH 中的程序代码并非必须搬到 RAM 中运行,这得由硬件配置、实际性能需求和应用场景共同决定。就像很多低端单片机,无论是依赖片内 Flash 还是外挂的 SPI NOR

2025-08-06 10:19:59 1209

1209

1209

1209

蓝牙低功耗

\\\\n\");

PRINT(\"[SLEEP] Light sleep: Parameters - RB_PWR_RAM32K=0x%02X, RB_PWR_RAM

2025-07-31 11:05:00

请问如何创建在 RAM 区域完全独立运行的闪存驱动程序代码?

我在开发闪存驱动程序代码时遇到了一个问题。我将准备好的HEX文件写入指定的RAM区域,并尝试使用指针调用,但调用失败,无法正常擦除或写入。对于flash的操作代码已经通过了单独的测试,为了使其更加

2025-07-25 07:33:05

LC87F0K08A 8位微控制器8K字节闪存ROM/384字节RAM规格书

电子发烧友网站提供《LC87F0K08A 8位微控制器8K字节闪存ROM/384字节RAM规格书.pdf》资料免费下载

2025-07-17 15:33:20 0

0

0

0无法将固件刻录到PFlash的原因?怎么解决?

我正在尝试将 Tasking 创建的十六进制文件中的构建数据闪存到闪存中,方法是先将其加载到 RAM 中,然后使用 IfxFlash 调用擦除所有 PFlash,再将所述构建加载到 PFlash 中

2025-07-15 07:39:16

如何使用 SPI 全双工在两个 5LP MPU 之间连接 RAM?

我需要将两个 5LP MPU 连接在一起以镜像两个 5LP MPU 内的 RAM。

我认为这将是 DMA 的一个功能,但我不确定如何实现该功能。

我的主 SPI 单元将向从属 MPU 发送一个数据块

2025-07-15 06:20:29

TLE9893 怎么将代码放在ram中运行?

如题,我希望将我的中断回调函数放进ram中运行以保证他的运行速度更快。那么我该怎么修改程序才能做到呢?或者有没有相关的例程给我参考一下。

2025-07-14 08:00:36

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

1.实验简介

实验目的:

掌握紫光平台的 RAM、ROM、FIFO

2025-07-10 10:37:35

请问收到HCI_DOWNLOAD_MINIDRIVER响应后是否需要LAUNCH_RAM命令?

如果在收到 HCI_DOWNLOAD_MINIDRIVER 响应后需要使用 LAUNCH_RAM 命令,则应使用什么地址?

这与 CYBT353027-02 特别相关。

开机后似乎需要立即执行以下

2025-07-07 06:56:25

三大开发环境下的Standby RAM变量配置教程

在嵌入式低功耗设计中,Standby RAM(待机保持内存)是芯片在深度休眠模式下仍能保持数据的关键硬件资源。但许多开发者苦于不同开发环境的配置差异,难以高效利用这一特性。

2025-07-05 15:18:25 2605

2605

2605

2605

【中科昊芯Core_DSC280025C开发板试用体验】+2.RAM工程与FLASH工程对比

前言

大家好,非常感谢电子发烧友与中科昊芯提供的DSC280025C开发板,这是一款DSP的开发板,基于RISC-V指令架构。

在开发DSP的芯片的时候,要分代码运行在RAM模式和FlASH模式

2025-07-04 10:37:42

基于恩智浦i.MX RT芯片内部RAM运行LVGL工程

随着越来越多用户选择i.MX RT系列芯片制作产品,产品的需求以及芯片的用法也越来越多。本文将介绍在i.MX RT平台中,如何创建LVGL项目并将其运行在内部SRAM而非SDRAM上。本文档包含4个部分:通过GUI Guider生成LVGL工程;LVGL工程的 FlexRAM内存配置;修改工程配置使得程序运行;使用局部缓冲区节省SRAM空间。本文档以IAR项目为例。

2025-07-01 09:33:19 2339

2339

2339

2339

CUEBIDE生成的APP程序,在写入FLASH之后无法正常跳转怎么解决?

,LENGTH = 64K

RAM (xrw) : ORIGIN = 0x20000000,LENGTH = 128K

FLASH (rx) : ORIGIN = 0x08020000,LENGTH = 896K

2025-06-09 06:43:29

FX3 RAM编程因定制板而失败怎么解决?

USBBulkSourceSink.img 写入 RAM 时,控制中心显示编程失败。

・我已确认该图像在评估板上成功。

・我已将 PMODE[2:0] 设置为 z11。

・我确认时钟是26MHz。

・确认电源正常。

请查看以下

2025-05-15 08:22:16

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36:22 912

912

912

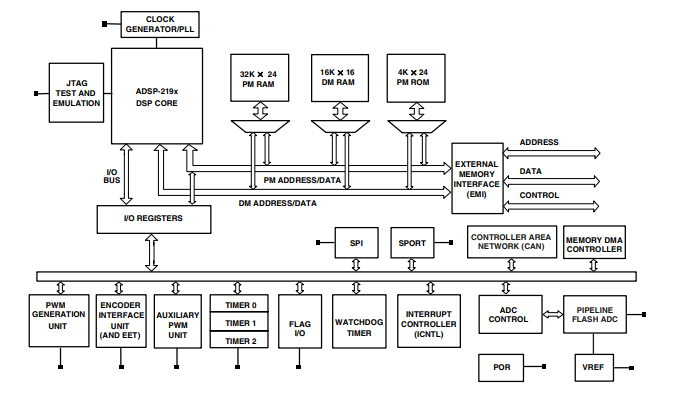

912ADSP-21992高性能混合型信号DSP,160MHz,32K字程序存储器RAM,16K字数据存储器RAM技术手册

ADSP-21992进一步扩展了ADSP-2199x混合信号DSP产品系列的性能,可提供32K字程序存储器RAM和16K字数据存储器RAM。此外,ADSP-21992还可提供片上CAN通信端口,支持

2025-05-12 16:08:28 889

889

889

889

浅谈MCU片上RAM

MCU片上RAM是微控制单元(MCU)中集成于芯片内部的随机存取存储器,主要用于程序运行时的数据存储与高速读写操作。以下是其核心要点: 一、定义与分类 片上RAM是MCU内部存储单元的一部分

2025-04-30 14:47:08 1123

1123

1123

1123工程配置linker flags选项添加--print-memory-usage时,ram打印是错误的,为什么?

工程配置linker flags选项添加--print-memory-usage时,编译后信息显示flash和ram已使用的百分比%,发现ram打印是错误的,ram实际没有用到100%。

有人使用过

2025-04-17 08:19:59

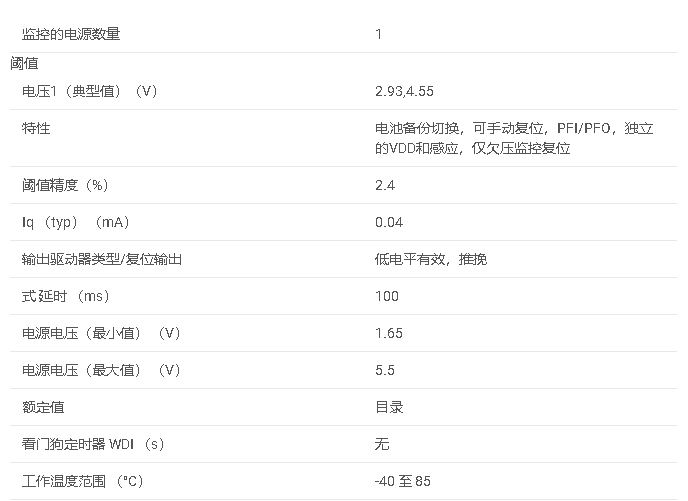

TPS3619 用于 RAM 保留的备用电池监控器数据手册

在上电期间,当电源电压 (V~DD 系列~或 V ~蝙蝠~ ) 变得高于 1.1 V。此后,电源电压监控器监控 V~DD 系列~并保持 RESET 输出有效,只要 V~DD 系列~保持在阈值电压 (V ~它~ ).内部 timer 延迟输出返回到 INACTIVE 状态 (HIGH),以确保 正确重置系统。延迟时间从 V 之后开始~DD 系列~已上升到 V 以上 ~它~ .当电源电压降至 V 以下时~它~output 再次变为 active (low)。

2025-04-12 10:30:16 672

672

672

672

mpc5744 bootloader怎么修改启动文件让RAM中的指定位置不清零?

我在开发一个bootloader,当APP跳转bootloader时,我写了一个标志在ram的固定地址,然后进行非掉电复位;问题是进入Bootloader之后,这个标志会丢失,请问如何修改程序才能让这个标志不被清除?

2025-04-08 08:28:52

如何在S32K146中实现以下功能?

;_vin_code_ram\" \"_vin_code_ram\"

uint8_t vp8u_vin[18];

#pragma pop

在Lcf Files文件中:

MEMORY

2025-04-04 08:00:45

开发5744的Bootloader时,为flashdriver在ram中指定了一块的空间?

你好,我在开发5744的Bootloader时,为flashdriver在ram中指定了一块的空间,我想要将flashdriver放在这块地址中,使用链接文件将函数地址指定到了这里,编译通过,但是下载进去并不能使用?请问这可能是由哪些原因造成的?

2025-04-02 07:07:05

别再说你的单片机RAM不够用了,来看看这个吧(可下载)

当我们写代码的时候,会用到很多变量,如果随意的定义变量,比如写了 N 多个“unsigned char/int X;”那么代码可能会显的很乱,自己拐回头看的时候都晕掉了,这个时候我们可以构造一个复杂的数据类型-结构体类型,对代码中出现的变量进行类别的划分,用构造的结构体类型定义结构体变量,在写 or 看代码的时候,只要看到这个结构体就能大致的知道其实现功能,

2025-03-28 14:12:41 0

0

0

0iMX8MPlus SoC M7核心是否需要单独的RAM内存?

对于 iMX8MPlus SoC ,M7 核心是否需要单独的 RAM 内存?或者是否有用于 M7内核的内部 SRAM?

2025-03-28 08:03:02

S32K116不能使用全部RAM怎么解决?

'm_data_2' 溢出 0 字节

当它是 8192 时,RAM 只使用了将近 9 KB,小于总 RAM 空间 16kB,为什么会提醒错误,如何解决?

2025-03-26 07:26:51

MCUXpresso存储器放置错误怎么解决?

我在 MCUXpresso 中的内存映射方面遇到了问题。我正在使用 LPC4088 和外部闪存以及外部 RAM。

我正在按照 MCUXPresso 手册的说明进行作:

设置内存分配和闪存驱动程序

2025-03-21 07:32:28

将指定文件下的函数加载到指定ram问题

问题:mcuxpresso环境,xip模式下我需要使用flexspi将norflash的一部分作为文件系统,将flex以及fatfs相关函数全部加载到ram,发现rodata仍然在flash地址

2025-03-12 17:02:45

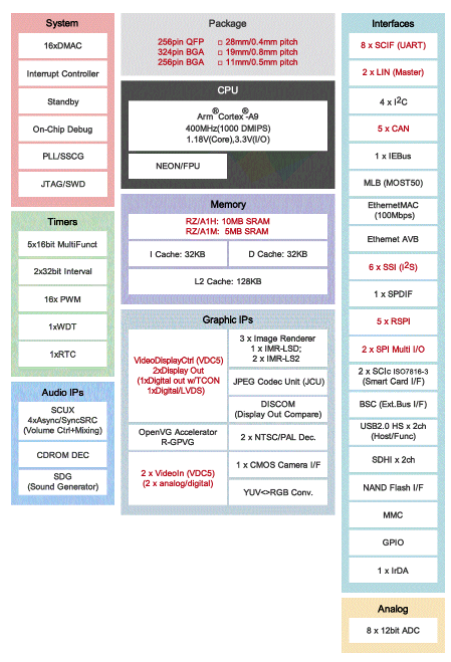

带5MB片内RAM的RTOS微处理器RZ/A1M数据手册

RZ/A1M 系列微处理器单元(MPU)功能齐全,配备运行频率为 400MHz 的 Arm® Cortex®-A9 内核以及 5MB的片上静态随机存取存储器(SRAM)。凭借 5MB 的片上 SRAM,RZ/A1M 无需外部存储器,就能支持两台分辨率为WSVGA(1024×600)的显示器,或者一台分辨率为 WXGA(1280×800)的显示器。RZ/A1M能够实现极为紧凑的嵌入式设计,而且无需担心存储器的采购问题以及存储器的停产问题。使用 RZ/A1M,你可以像设计微控制器(MCU)那样设计嵌入式系统,同时获得400MHz Arm® Cortex®-A

2025-03-11 15:04:11 1127

1127

1127

1127

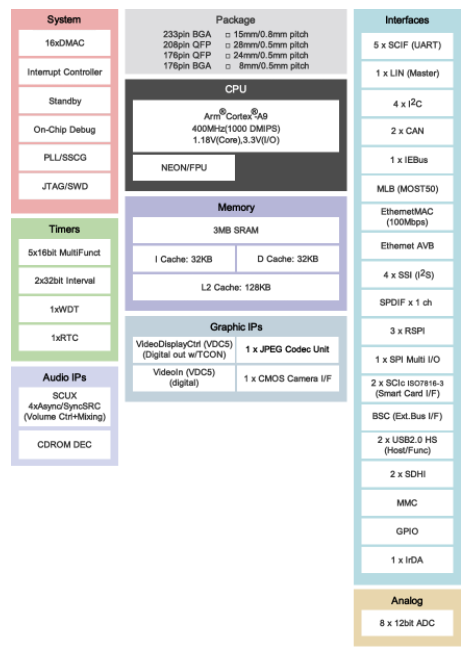

带片内RAM 3MB的RZ/A1LU RTOS微处理器数据手册

RZ/A1LU 系列微处理器单元(MPU)性价比高,具备运行频率达 400MHz 的 Arm® Cortex® - A9 内核以及 3MB的片上静态随机存取存储器(SRAM)。凭借 3MB 的片上 SRAM,RZ/A1LU 无需外部内存,就能支持两台分辨率为WVGA(800×480)的显示器,或者一台分辨率为 WSVGA(1024×600)的显示器。RZ/A1LU能够实现极为紧凑的嵌入式设计,且无需担忧内存采购和内存停产的问题。有了 RZ/A1LU,你可以像设计微控制器(MCU)那样设计嵌入式系统,同时获得 400MHz Arm® Cortex® - A9 MPU 的性能。

2025-03-11 14:22:18 990

990

990

990

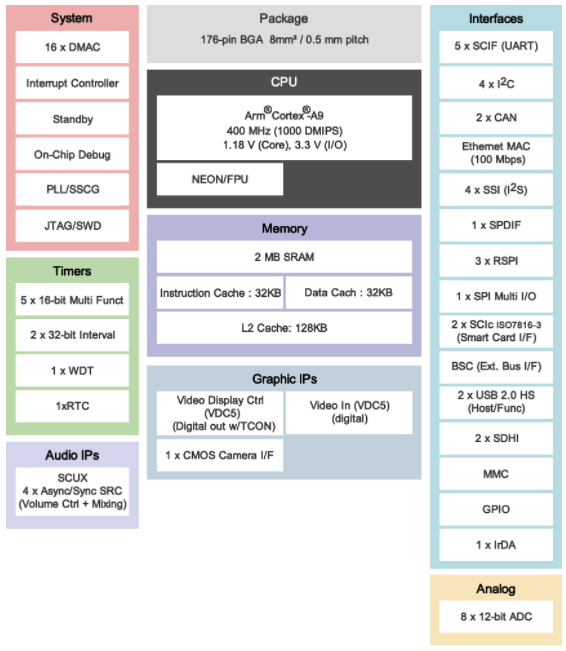

带2MB片内RAM的RTOS微处理器RZ/A1LC数据手册

RZ/A1LC 微处理器单元(MPU)是 RZ/A1 系列中最具成本效益的产品,其特点是配备运行频率为 400MHz 的 Arm®Cortex®-A9 内核以及 2MB 的片上静态随机存取存储器(SRAM)。凭借 2MB 的片上 SRAM 和 400MHz 的 Arm® Cortex®-A9 内核,RZ/A1LC 是那些试图达到 MPU 性能水平的微控制器(MCU)设计的绝佳替代品。RZ/A1LC 能够实现非常紧凑的嵌入式设计,而且无需担心内存采购和内存停产的问题。它支持 Linux、实时操作系统(RTOS)或裸机运行,是设计紧凑且高性能的智能物联网终端

2025-03-11 14:07:40 1036

1036

1036

1036

cube ai模型太大,超过闪存和ram,量化后8位整数,不支持解析怎么解决?

2025-03-11 06:48:46

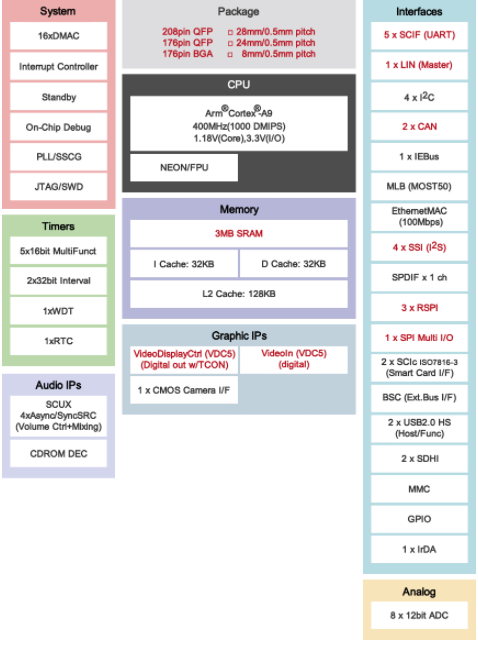

带片内RAM 3MB RZ/A1L RTOS微处理器数据手册

RZ/A1L 系列微处理器(MPU)采用了运行频率达 400MHz 的 Arm® Cortex® - A9 内核,并配备 3MB的片上静态随机存取存储器(SRAM)。凭借这 3MB 的片上 SRAM,RZ/A1L 无需外部存储器就能支持两块WVGA(800x480)分辨率的显示屏,或者一块 WSVGA(1024x600)分辨率的显示屏。RZ/A1L能够实现极为紧凑的嵌入式设计,让开发者无需担心存储器采购和存储器停产的问题。借助 RZ/A1L,你可以像设计微控制器(MCU)一样设计嵌入式系统,同时获得400MHz Arm® Cortex® - A9 微处理器(MPU)的

2025-03-10 16:14:20 977

977

977

977

STM32U5如何设置才能保证LPBAM和RUN模式下的应用程序正常使用呢?

/* Memories definition */MEMORY{RAM (xrw): ORIGIN = 0x28000000,LENGTH = 16KFLASH(rx): ORIGIN

2025-03-10 08:21:07

RAM容量不足导致的数据溢出如何预防和处理?

在 STM32F411 中,RAM 容量是有限的,特别是在进行复杂的数据处理和存储时,可能会遇到数据溢出问题。数据溢出是指程序运行时,数据超出了 RAM 的分配区域,导致程序崩溃或数据丢失。STM32F411 的 RAM 容量为 128KB,在处理较大数据量时,容易出现内存溢出的情况。如何预防和处理

2025-03-07 16:09:23

STM32H743对关键中断函数,使用ITCM搬至RAM运行,仿真进入HardFault_Handler报错怎么解决?

STM32H743对关键中断函数,使用ITCM搬至RAM运行,STM32CubeIDE仿真进入HardFault_Handler报错。其中,ITCM已查找网上多篇教程,修改了ld链接文件

2025-03-07 08:04:54

MXD1210非易失RAM控制器技术手册

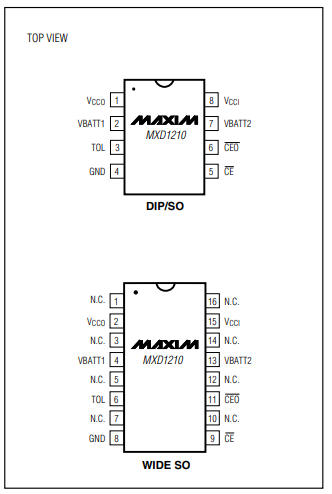

MXD1210非易失性RAM控制器是一款超低功耗CMOS电路,可将标准(易失性)CMOS RAM转换为非易失性存储器。它还会持续监控电源,以在RAM的电源处于边际(超出容限)条件时提供RAM写保护。当电源开始出现故障时,RAM受到写保护,并且器件切换到电池备用模式。

2025-02-28 10:48:16 917

917

917

917

DS1315隐含时钟芯片技术手册

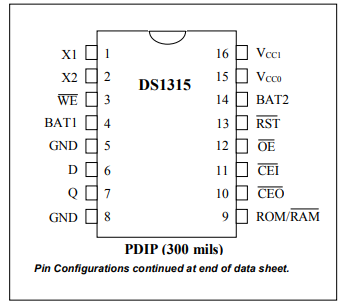

DS1315幻象时间芯片集成了CMOS计时器和非易失性存储器控制器。在没有电源的情况下,外部电池可维持计时操作并为CMOS静态RAM提供电源。该计时器可记录百分之一秒、秒、分、时、星期、日期、月和年

2025-02-28 10:23:08 769

769

769

769

DS1746 Y2K兼容、非易失时钟RAM技术手册

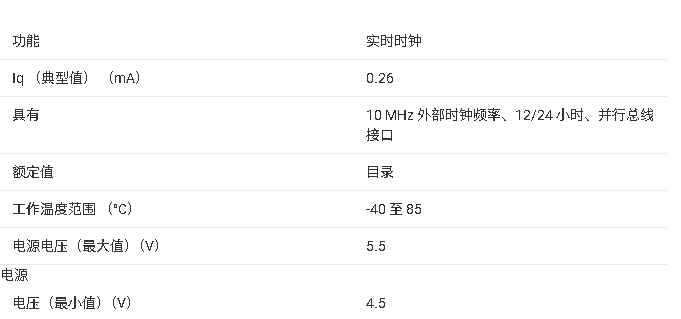

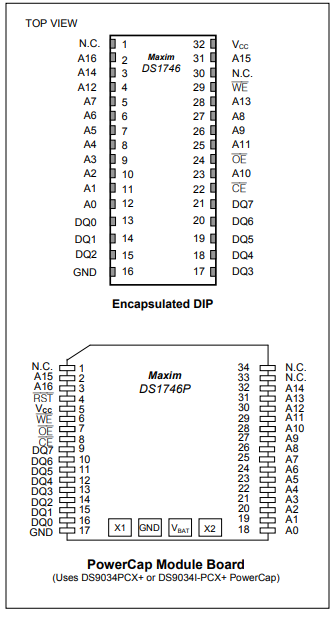

DS1746是一款全功能、符合2000年标准(Y2KC)的实时时钟/日历(RTC)和128k x 8非易失性静态RAM。用户对DS1746内所有寄存器的访问都通过字节宽接口实现,如图1所示。RTC

2025-02-27 17:20:04 913

913

913

913

DS1557 4M非易失、Y2K兼容时钟RAM技术手册

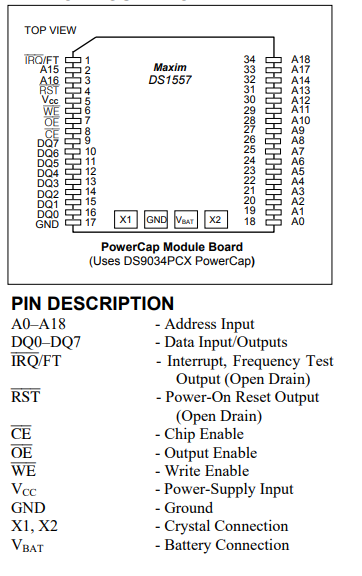

DS1557是一款全功能、符合-2000年标准(Y2KC)的实时时钟/日历(RTC),具有RTC警报、看门狗定时器、上电复位、电池监控器和512k x 8非易失性静态RAM。用户对DS1557内所有

2025-02-27 17:11:32 932

932

932

932

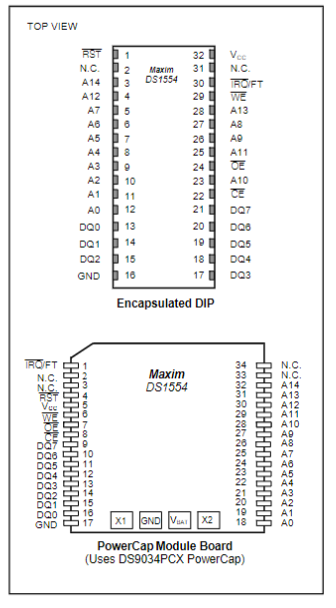

DS1554 256k非易失、Y2K兼容时钟RAM技术手册

DS1554是一款全功能、符合2000年标准(Y2KC)的实时时钟/日历(RTC),具有RTC警报、看门狗定时器、上电复位、电池监控器和32k x 8非易失性静态RAM。用户对DS1554内所有

2025-02-27 16:54:35 1041

1041

1041

1041

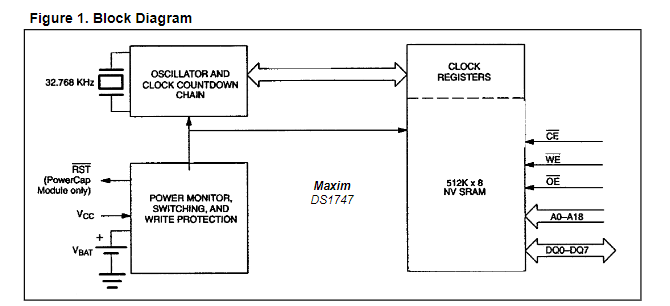

DS1747 Y2K兼容、非易失时钟RAM技术手册

信息和控制位占用RAM中最高的8个地址。RTC寄存器包含世纪、年、月、日、星期、小时、分和秒数据,采用24小时BCD格式。器件可自动对每个月份及闰年进行日期校正。RTC时钟寄存器采用双缓冲,可避免在时钟

2025-02-27 15:51:09 872

872

872

872

DS1558系列看门狗时钟,带有NV RAM控制器技术手册

DS1558为完备的、2000年兼容(Y2KC)的、实时时钟/日历(RTC),具有RTC报警、看门狗定时器、上电复位、电池监控以及NV SRAM控制器。用户访问DS1558中所有寄存器都通过完整数据资料中的图1所示的字节宽度接口来实现。RTC寄存器包含24小时制BCD格式的世纪、年、月、日、星期、时、分、秒数据。对于每月天数及闰年的修正均自动完成。

2025-02-27 11:03:48 1005

1005

1005

1005

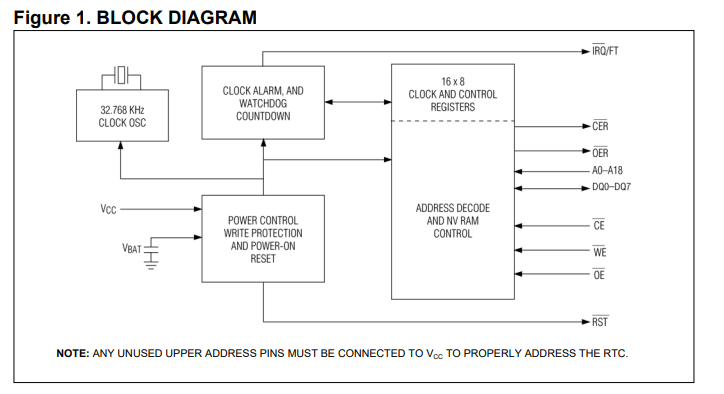

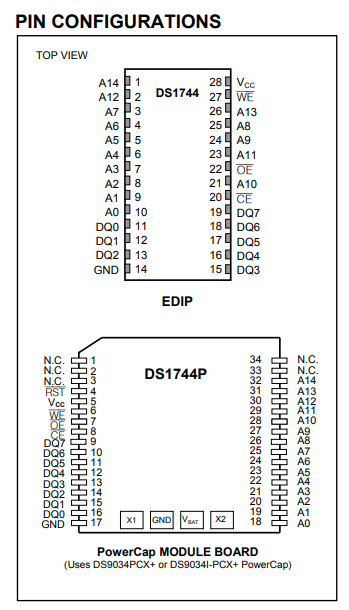

DS1744系列Y2K兼容、非易失时钟RAM技术手册

访问。RTC信息和控制位占用RAM中最高的8个地址。RTC寄存器包含世纪、年、月、日、星期、小时、分和秒数据,采用24小时BCD格式。器件可自动对每个月份及闰年进行日期校正。RTC时钟寄存器采用双缓冲

2025-02-27 09:31:07 996

996

996

996

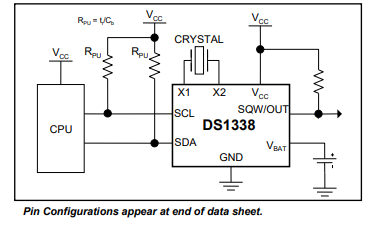

DS1338 I2C RTC,带有56字节NV RAM技术手册

DS1338串行实时时钟(RTC)是低功耗、全二进制编码的十进制(BCD)时钟/日历,外加56字节NV SRAM。地址与数据通过I²C总线串行传送。时钟/日历可以提供秒、分、时、日、月、年信息。对于少于31天的月份,到每月的最后一天会自动进行调节,包括闰年修正。该时钟可以通过AM/PM指示器工作在24小时模式或12小时模式。DS1338具有一个内部电源感应电路,可以检测到电源失效,并自动转换到备用电源。

2025-02-26 17:29:05 931

931

931

931

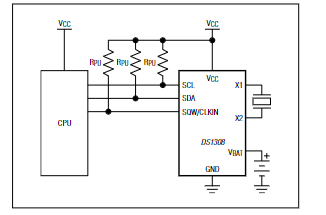

DS1308低功耗I2C RTC,带有56字节NV RAM技术手册

DS1308串行实时时钟(RTC)是一个低功耗、全二进制编码的十进制(BCD)时钟/日历,加上56字节的NV RAM.地址和数据通过I2C接口串行传输。时钟/日历提供秒、分钟、小时、日、日期、月和年

2025-02-26 13:48:50 884

884

884

884

闪速存储器属于RAM还是ROM,闪速存储器一般用来做什么的

在数字存储技术的快速发展中,闪速存储器(Flash Memory)以其独特的性能和广泛的应用领域,成为了连接随机存取存储器(RAM)与只读存储器(ROM)之间的重要桥梁。本文将深入探讨闪速存储器的技术特性、分类及其在现代电子设备中的应用。

2025-01-29 16:53:00 1683

1683

1683

1683闪速存储器属于RAM还是ROM,闪速存储器有哪些功能和作用

本文旨在深入探讨闪速存储器的归属问题,即它是否属于RAM或ROM,同时详细阐述闪速存储器的功能与作用。

2025-01-29 15:21:00 1590

1590

1590

1590RAM-Based Shift Register Xilinx IP核的使用

一般来讲,如果要实现移位寄存器的话,通常都是写RTL用reg来构造,比如1bit变量移位一个时钟周期就用1个reg,也就是一个寄存器FF资源,而移位16个时钟周期就需要16个FF,这种方法无疑非常浪费资源。

2025-01-21 15:42:25 2967

2967

2967

2967

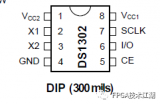

基于FPGA的实时时钟设计

本次设计采用了美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路 DS1302,它可以对年、月、日、周、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。采用三线

2025-01-06 16:06:57 1903

1903

1903

1903

电子发烧友App

电子发烧友App

评论