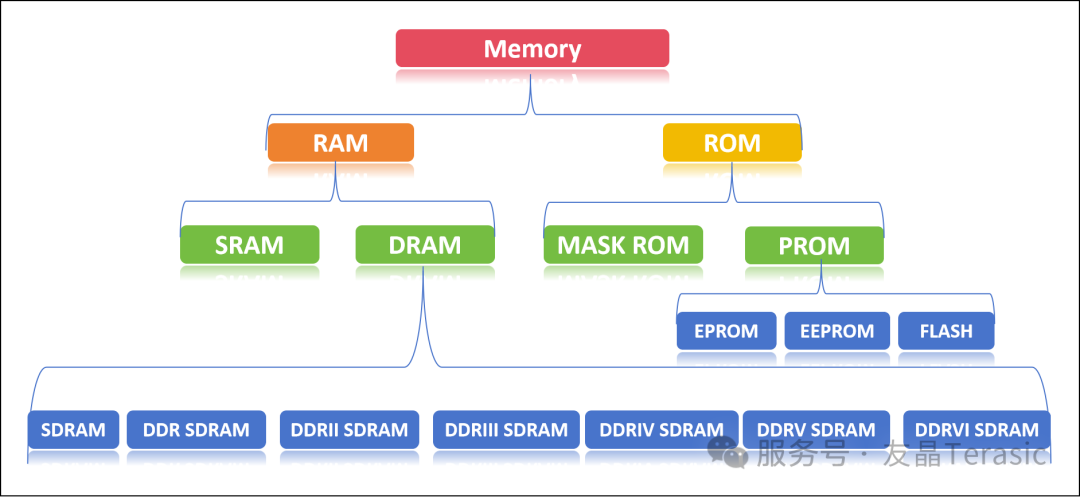

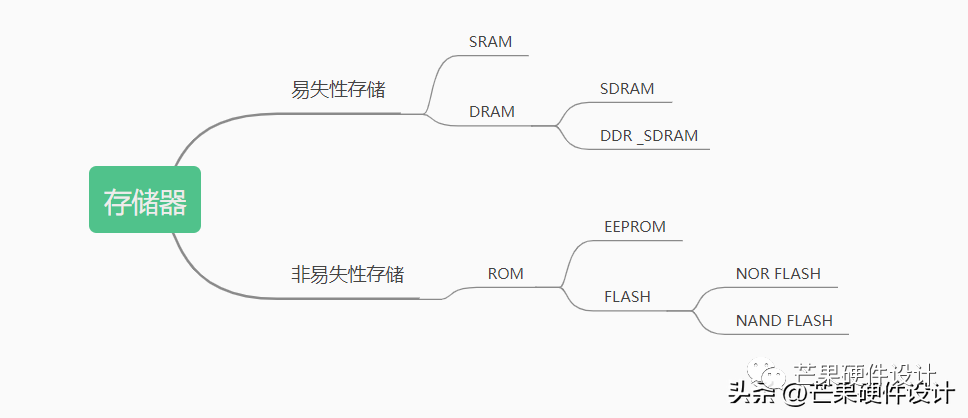

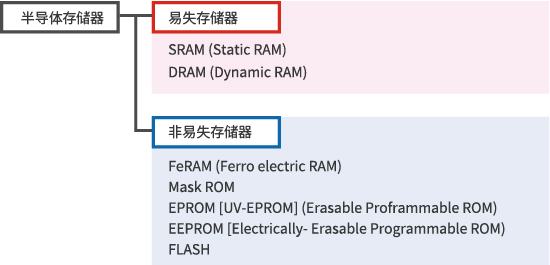

存储器分类

初学者要了解SDRAM需要先了解存储器分类。按照存储器的存储功能划分,可将其分为RAM 和 ROM 两大类。

RAM(Random Access Memory)存储器又称随机存取存储器,正常工作时存储的内容可通过指令随机读写访问,RAM中的数据在掉电时会丢失。

ROM(Read Only Memory)存储器又称只读存储器,只能由专用的装置写入,一旦写入,不能随意改写。正常工作时ROM只能读出数据。ROM 具有掉电后数据可保持不变的优点。

RAM往下又可细分为SRAM和DRAM。

SRAM

SRAM(Static RAM),全称为静态随机存取存储器,是一种在系统不断电的情况下能无限期保持其内容的记忆设备。由于其读写速度极快且能耗极低的特点,在对速度和可靠性要求较高的应用场景中,如CPU缓存等,SRAM成为了首选方案。然而,值得注意的是,SRAM每个存储单元采用了复杂的双稳态电路设计来保存数据,制作一个bit存储位通常需要6个MOS管,这直接导致了其集成度低(容量一般只能到几百到几兆字节)且制造成本远高于DRAM。

DRAM

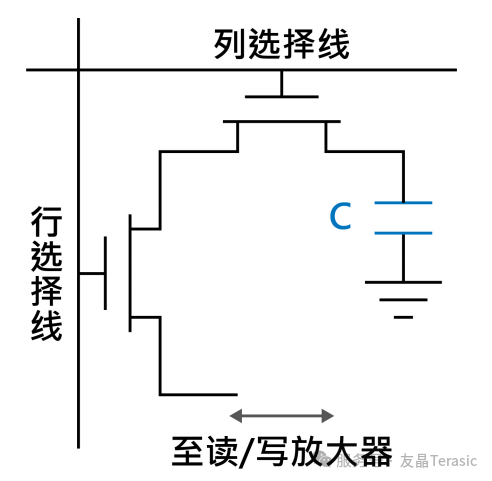

DRAM(Dynamic RAM),动态随机存取存储器,与制作一个 bit存储位通常需要6个MOS管的SRAM相比,保存一位数据简单到只需一个电容,其中一个存储器单元的结构如图所示。当行选择线与列选择线动作时,可令 MOSFET 接通,允许电容的电压被读取或写入。

由于电容的电压会有传输时的损失以及保存时的漏电现象,所以除了在读取与写入时必须经过放大之外,每保存一位经过一段时间就必须将数据读出后再写入一次,这个动作称为 DRAM 的刷新(Refresh),会降低使用效率。

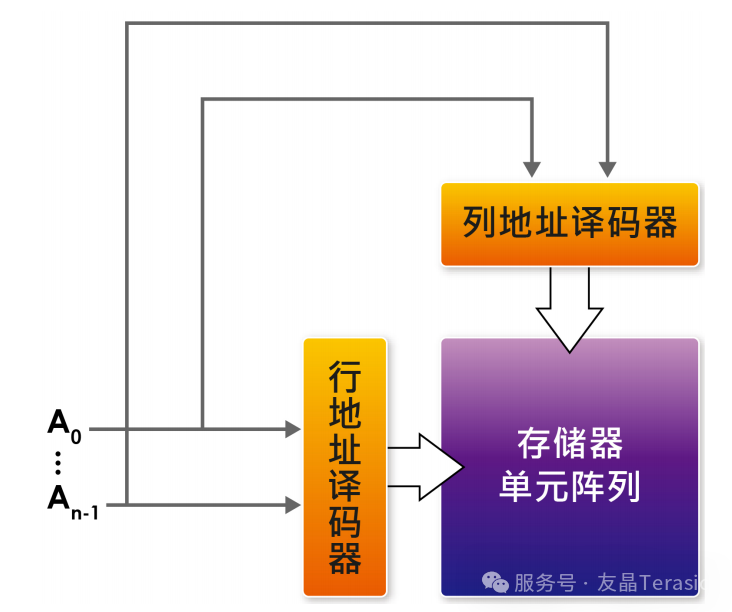

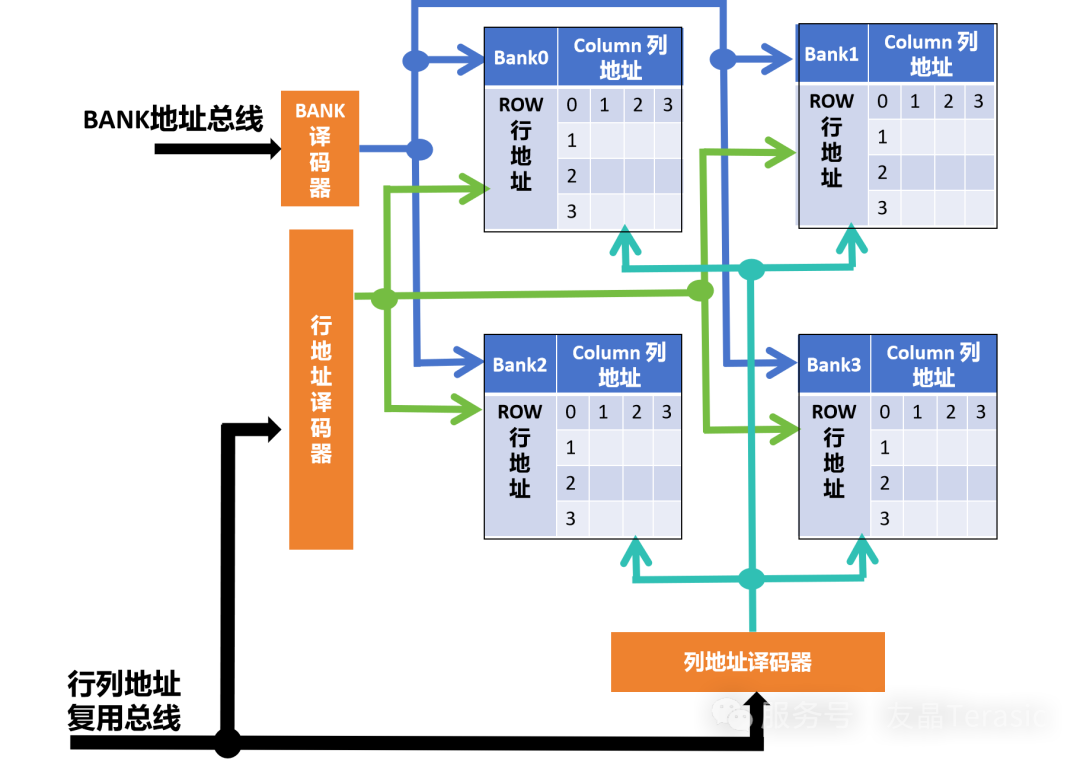

为了降低封装成本,减少 IC 引脚的数目, DRAM 的地址输入线是采用多工方式,亦即以同样的地址线分两次输入,先输入行地址再输入列地址,如下图所示。对于 n 条地址线输入的 DRAM,可以规划最大译码的存储器单元数目为 22n,因此常见 DRAM 芯片的 容量多以 4 的倍数递增,如 4M Byte、 16M Byte、 64M Byte、 256M Byte 等等。

SDRAM的诞生

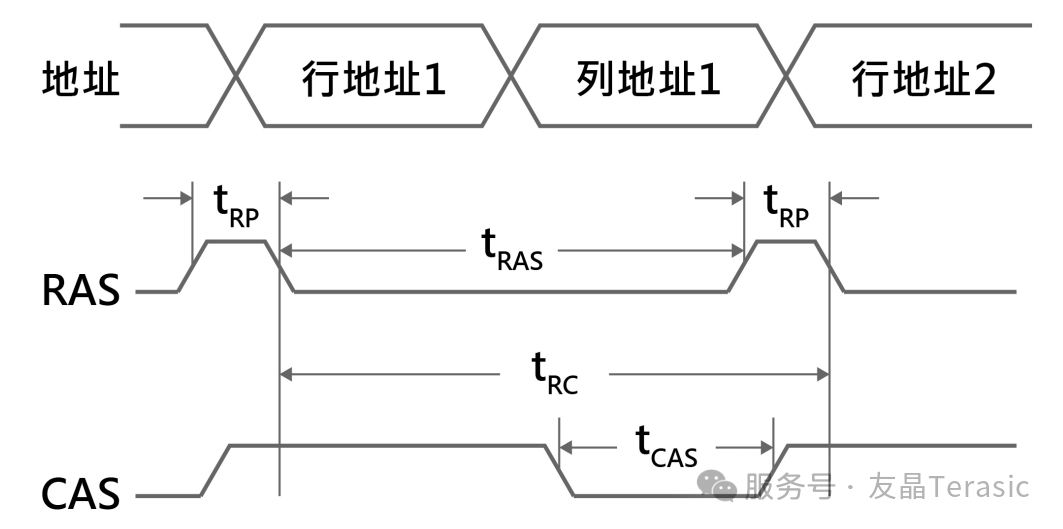

由于 DRAM 是以 MOSFET 为主要器件,电路中的杂散电容(Stray Capacitance)对存取时间的影响很大,每更换一次行地址时,都必须等待一段时间让控制电路充电,数据的存取才会正确,此充电时间称为预充电时间(Prechage Time, TRP),如下图所示。早期 DRAM 的行地址是由 RAS 信号的下降沿来锁住后送给行地址译码器处理,在此 RAS信号至少要维持一段建立行地址时间(tRAS),这段时间内再以 CAS 信号的下降沿来锁住列地址后送给列地址译码器处理,才能译码到一个正确的存储器单元地址,因此一个DRAM 的存取周期(tRC)可用预充电时间加上行地址建立时间来计算:tRC = tRP + tRAS。

这不算短的时间,使得 DRAM 无法成为高速的存取设备,但是低价大容量的特性怎么会让厂商轻易放弃呢?于是在商业的竞争下,经过阶段性的改良,同步动态随机存储器(Synchronous Dynamic Random Access Memory,简称 SDRAM)诞生。如前面所述, DRAM 在更换行地址时需有预充电时间的天生障碍,限制了分散数据的随机存取速度,但是对于可预知下一笔数据地址的突发模式(Burst Mode), SDRAM 采用存储器交错处理(Memory Interleaving)以及多管线(Multi-Pipeline)的技术,提升分配时间内读写的信息量,改善了在突发模式下的存取时间。由于在连续存取的应用中可达到与外部时钟同步的效率,故被称为同步动态随机存储器。

所谓突发模式是存取存储器时,分配一次存储器的地址,即可进行一连串的存或取动作 N 次,不需分配 N 次存储器的地址,可以省去寻址的时间。至于存储器交错处理是将存储器划分成多个BANK(通常为 2 个或 4 个BANK),如图:

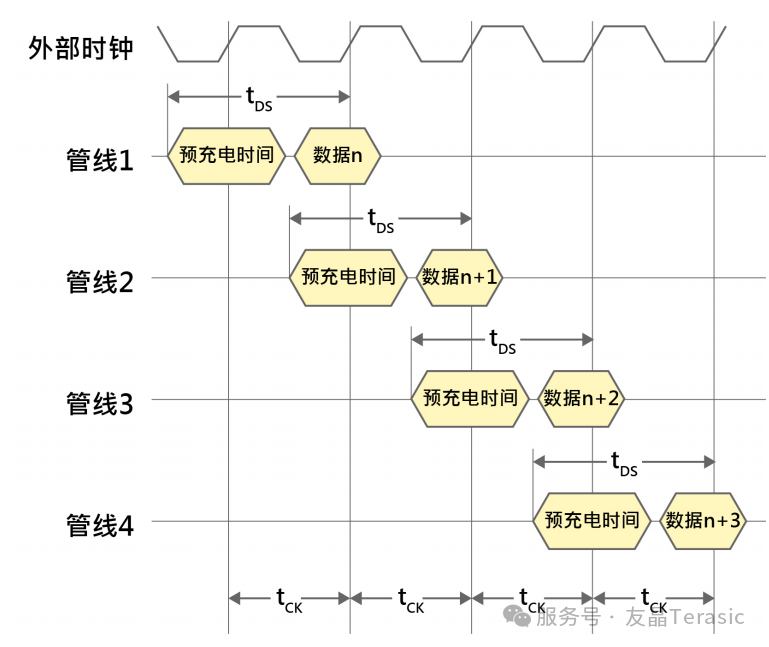

控制端可交错存取这些BANK的数据,举例来说,将保存于存储器的奇数地址和偶数地址分开,当上一个字符被更新时,下一个字符的存取可以不受到影响,减少了等待的时间,让存储器的存取更快,虽然不是 2 或 4 倍的速度,但还是快了许多。而多管线是指利用选择器的原理将存储器多个区块的数据轮流传送至数据端,下图即说明了一个 SDRAM 的存取时间 (tDS) 大于外部一个时钟时间 (tCK),但在多管线的架构下,外部仍可同步读取数据。

存储器交错处理与多管线硬件功能的结合,可以有效的忽略等待地址译码及预充电的时间。但值得注意的是,SDRAM 可以改善的是数据预选及输出的方式,并非数据真正的存取时间,所以对于突发模式下的第一笔数据的存取时间仍然无法改善。

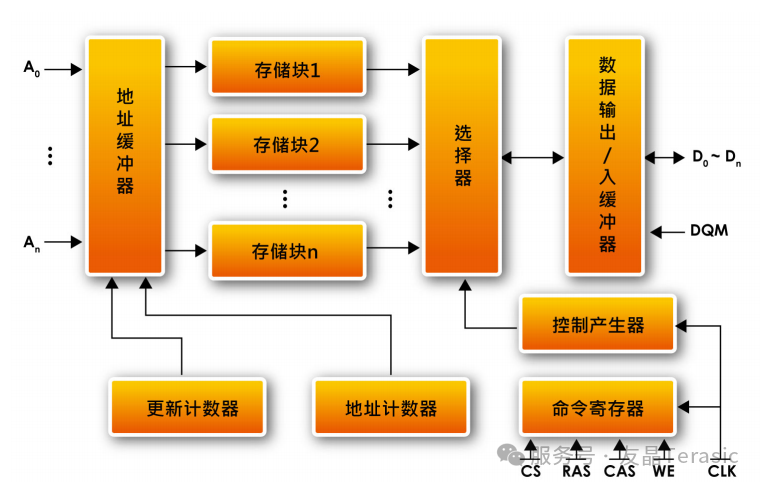

另外,因为 SDRAM 可以选择操作模式与调整突发存取的长度,与传统的 DRAM 在使用程序上有所不同,必须先对 SDRAM依序写入命令才能进行存取,下图为简化后SDRAM 的架构图。另外, SDRAM 的数据宽度均配合 CPU 的发展而生产,故有 8 位、16 位、 32 位、 64 位的产品。

DDR SDRAM

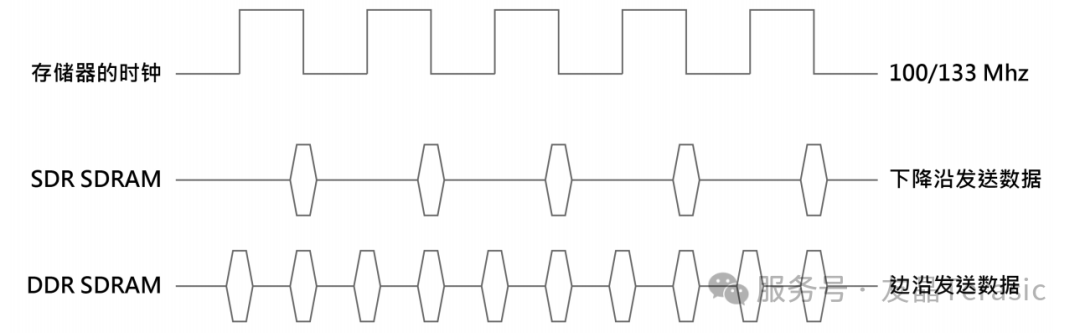

至于 DDR SDRAM ,即双倍数据率(Double Data Rate) SDRAM 的意思,相较于前面所介绍的 SDRAM 仅在存储器时钟下降沿存或取数据,他利用时钟的上升沿及下降沿都可存或取数据,故数据的传输速率为 SDRAM 的两倍。为了与 DDR SDRAM 区别, SDRAM 又常被称为 SDR SDRAM。比较下图中 SDR 与 DDR SDRAM 存取数据时序的差异,可知一个工作于 64 位 /100MHz 时钟下的 DDR SDRAM,每秒数据的传输量为 100M x 64bit x 2 / 8bit =1600MB,而 SDR SDRAM 则仅为其一半 800MB。此外 SDR SDRAM 的电源为 3.3V,而 DDR SDRAM 为 2.5V,DDR 的省电性较占优势。

DDR SDRAM发展很快,后来出现了DDR2 SDRAM、DDR3 SDRAM,而现在都已经有DDR6 SDRAM了,但它们的控制都基于SDRAM控制原理演变而来。

SDRAM总结

总而言之,SDRAM即同步动态随机存取存储器。“同步”是指其时钟频率与FPGA系统时钟频率相同,并且内部命令的发送与数据的传输都以此频率为基准;“动态”是指存储阵列需要不断的刷新来保证所存储数据不丢失;“随机”是指数据不是线性依次存储,而是自由指定地址进行数据的读写。

-

DRAM

+关注

关注

40文章

2373浏览量

188169 -

SDRAM

+关注

关注

7文章

449浏览量

57287 -

存储器

+关注

关注

39文章

7715浏览量

170856 -

MOS管

+关注

关注

110文章

2754浏览量

74931

原文标题:02-SDRAM控制器的设计——SDRAM简介

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

存储器的分类及其区别

存储器的分类及其区别

存储器的分类及其区别

评论