基于PLD的CCD Sensor驱动逻辑设计

0 引 言

视觉信息是客观世界中非常丰富,非常重要的部分。随着多媒体系统的发展,图像传感器应用越

2010-01-14 11:33:27 1861

1861

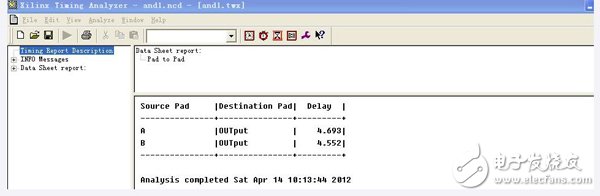

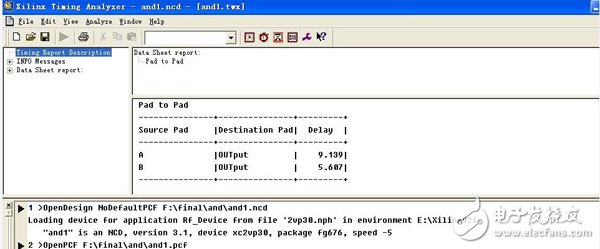

信号在FPGA器件中通过逻辑单元连线时,一定存在延时。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作电压、温度等有关。

2020-03-29 10:27:00 4067

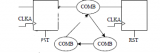

4067 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 1443

1443 芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 1843

1843 可编程逻辑系统通常部署在可能存在噪声的应用中。这种噪声会影响可编程逻辑设计接收的信号。

2023-08-30 10:24:59 3600

3600

组合逻辑电路PPT电子教案学习要点: 组合电路的分析方法和设计方法 利用数据选择器和译码器进行逻辑设计的方法 加法器、编码器、译码器等中

2009-09-16 16:05:29

电路的分析和设计方法。 2. 掌握译码器、编码器和数据选择器的功能及在组合逻辑设计中的应用。 &

2009-09-16 15:09:13

本帖最后由 gk320830 于 2015-3-9 20:12 编辑

组合逻辑设计原则--Combinational logic design principles-数字电路 (数字设计原理)[hide][/hide]

2009-09-26 12:51:11

组合逻辑设计实践- Combinational logic design practices-(数字设计原理与实践)

2009-09-26 12:52:53

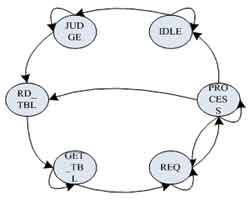

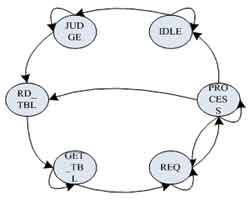

偏硬件:接口电路中的门组合电路;偏软件:算法、接口控制器实现中的状态机群或时序电路。随着逻辑设计的深入,复杂功能设计一般基于同步时序电路方式。此时,逻辑设计基本上就是在设计状态机群或计数器等时序电路

2021-11-10 06:39:25

影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

在数字电路中,常规介绍和解释:

什么是竞争与冒险现象:

在组合电路中

2023-11-02 17:22:20

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

冒险往往会影响到逻辑电路的稳定性。时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。如何处理毛刺

2018-08-01 09:53:36

图像采集系统的结构及工作原理是什么FPGA逻辑设计中的常见问题有哪些

2021-04-29 06:18:07

请教各位,FPGA在逻辑设计中有哪些注意事项?

2021-05-07 07:21:53

逻辑的基本概念做了较详细的介绍,并且列举了一个实例说明时序逻辑在大多数设计中更由于组合逻辑。组合逻辑在实际应用中,的确存在很多让设计者头疼的隐患,例如这里要说的毛刺。(特权同学,版权所有)任何信号在

2015-07-08 10:38:02

的瞬间,组合逻辑的输出常常产生一些小的尖峰,即毛刺信号,这是由FPGA内部结构特性决定的。毛刺现象在FPGA的设计中是不可避免的,有时任何一点毛刺就可以导致系统出错,尤其是对尖峰脉冲或脉冲边沿敏感

2012-09-06 14:37:54

实战应用,这种快乐试试你就会懂的。话不多说,上货。 数字电路中的组合逻辑 根据逻辑功能的不同特点,可以将数字电路分为两大类,一类称为组合逻辑电路(简称组合电路),另一类称为时序逻辑电路(简称

2023-02-21 15:35:38

`MCS-51单片机与FPGA接口的逻辑设计.........`

2013-06-08 11:25:29

MPEG-2编码复用器中的FPGA逻辑设计,看完你就懂了

2021-04-29 06:13:34

Sequential Logic Design principles 时序逻辑设计原则[hide][/hide]

2009-09-26 13:00:22

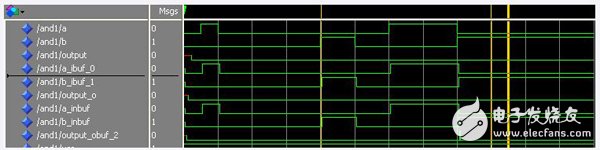

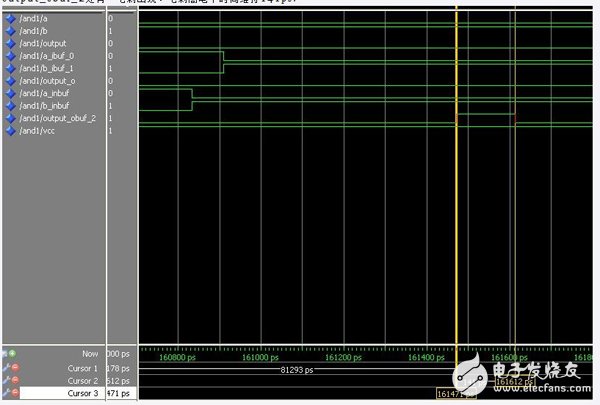

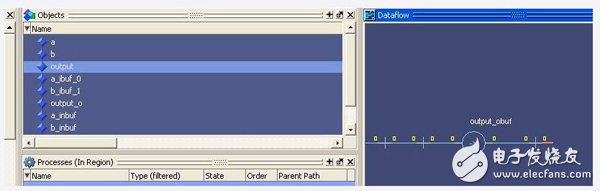

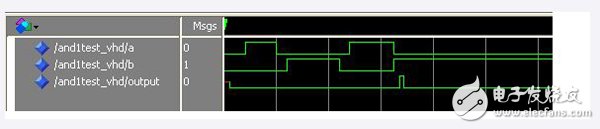

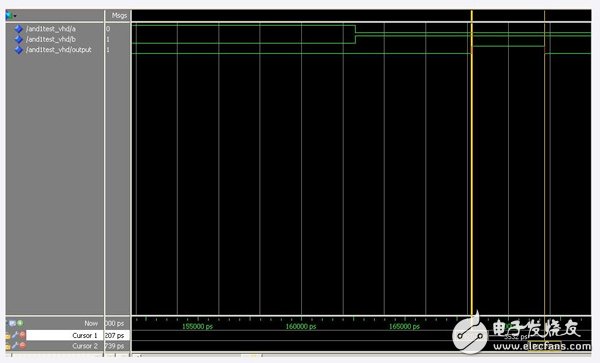

,因此毛刺现象在PLD、FPGA设计中尤为突出) 图2给出了一个逻辑冒险的例子,从图3的仿真波形可以看出,"A、B、C、D"四个输入信号经过布线延时以后,高低电平变换不是同时发生

2012-02-10 09:50:36

静态时序分析与逻辑设计

2015-05-27 12:28:46

本文为明德扬原创及录用文章,转载请注明出处!一、 什么是组合逻辑电路? 在数字电路中,根据逻辑功能的不同,我们可以将数字电路分成两大类,一类叫做组合逻辑电路、另一类叫做时序逻辑电路。本次主要讲解组合

2020-04-24 15:07:49

一般要求是时序逻辑)。在实际设计中,为了便于操作,我们可以首先考虑用时序逻辑,看是否能满足设计要求。如果无法满足目标要求,需要凑时序,那么就考虑改为组合逻辑。举个例子便于大家更好地理解,如下图所示

2020-03-01 19:50:27

交通灯控制逻辑设计n 1、红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号,实验电路用逻辑开关代替。n 2、主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿

2017-09-15 10:25:06

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。 如果布尔式中有相反的信号则可能产生竞争和冒险现象。 解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

2019-08-02 11:57:35

FPGA开发板上组合逻辑电路的实现,这些实例包括在数字逻辑设计课程中所熟知的部分中规模集成电路:优先编码器、多路复用器以及加法器,最后还将介绍算术逻辑单元ALU的实现。优先编码器实验原理在数字系统中

2022-07-21 15:38:45

逻辑电路如图3.17所示,以上面的组合逻辑和时序逻辑电路为例,输入信号x和y为随机信号,组合逻辑的输出信号z1在输入x和y发生变化并满足逻辑变化条件时立刻发生变化,当然了,这个变化在实际电路中也有一定

2017-11-17 18:47:44

华为 大规模逻辑设计指导书 方法 论

2019-11-22 22:52:12

本帖最后由 eyesee 于 2017-3-2 09:29 编辑

华为_大规模逻辑设计指导书

2017-03-01 11:56:34

华为_大规模逻辑设计指导书

2012-08-18 08:11:53

华为大规模逻辑设计指导书

2015-04-20 13:41:35

华为大规模逻辑设计指导书。非常详细地介绍了逻辑设计的规范要求及方法。

2020-01-27 17:58:38

华为静态时序分析与逻辑设计

2014-05-20 22:55:09

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

本文使用符合PCI电气特性的FPGA芯片进行简化的PCI接口逻辑设计,实现了33MHz、32位数据宽度的PCI从设备模块的接口功能,节约了系统的逻辑资源,且可以将其它用户逻辑集成在同一块芯片,降低了成本,增加了设计的灵活性。

2021-05-08 08:11:59

前言FPGA 可以实现高速硬件电路,如各种时钟,PWM,高速接口,DSP计算等硬件功能。这是Cortex-M 处理器软件无法比拟的。要实现FPGA 的逻辑设计,对于嵌入式系统工程师又是比较复杂和具有

2021-12-21 06:13:49

本帖最后由 daworencai 于 2016-1-21 14:46 编辑

岗位职责:1.负责部门存储系列产品的逻辑设计开发工作;2.负责存储系列产品的BCH算法优化、高速存储技术实现等;负责

2016-01-21 14:42:39

数字电路与逻辑设计数字逻辑电路的分析和方法,常用集成数字逻辑电路的功能和应用;主要内容包括:逻辑代数基础、组合逻辑电路分析和设计、常用组合逻辑电路及MSI组合电路模块的应用,时序逻辑电路的分析

2021-08-06 07:33:41

问题。

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。

那么 FPGA 产生竞争冒险的原因是什么呢?

信号在

2023-05-30 17:15:28

要使用哪种方法去验证 FPGA 的逻辑设计?FPGA的优缺点是什么?

2021-04-08 06:57:32

静态时序分析与逻辑设计

2017-12-08 14:49:57

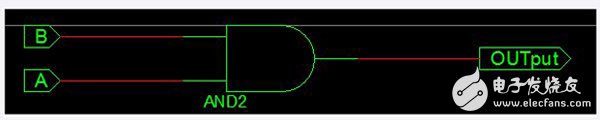

消除组合逻辑产生的毛刺—PLD设计技巧 Design of Combinational Circuit

What is Combinational Circuit

Combinational Circuit if

2008-09-11 09:34:18 29

29 组合逻辑电路实验分析一、实验目的 1.掌握组合逻辑电路的分析方法与测试方法; 2.了解组合电路的冒险现象及消除方法; 3.验证半加器、全加器的逻辑功

2009-07-15 18:35:50 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 时序逻辑设计原则 (Sequential Logic Design principles):A sequential logic circuit is one whose outputs

2009-09-26 12:54:35 33

33 时序逻辑设计实践 (Sequential Logic Design Practices)The purpose of this chapter is to familiarize you

2009-09-26 12:57:53 13

13 基于PLD芯片的时序逻辑设计与实现:原理图输入设计直观、便捷、操作灵活;1-1、原理图设计方法简介QuartusII已包含了数字电路的基本逻辑元件库(各类逻辑门及触发器),宏

2009-10-29 22:03:10 0

0 本文介绍了一种基于FPGA 的用自定义串口命令的方式实现MDIO 接口逻辑设计的方法,并对系统结构进行了模块化分解以适应自顶向下的设计方法。所有功能的实现全部采用VHDL 进行描

2009-12-26 16:48:44 103

103 电子技术--组合逻辑电路掌握组合逻辑电路的分析方法与设计方法掌握利用二进制译码器和数据选择器进行逻辑设计的方法理解加法器、编码器、译码器等中规模集成电

2010-04-12 17:52:29 0

0 摘要:给出了基于A S M 图的数字集成电路控制器的设计的主要电路实现方法,并给出了目前最常采用的方法——EDA法.关键词: A S M 图; 逻辑设计; E DA; On e Ho t

2010-04-26 11:25:44 14

14 摘要:“逻辑设计”课是近二、三十年随着信息类一批新专业(自动化、计算机、通信和信息等)陆续建立而开设的一门重要的学科基础课。只要掌握“逻辑设计”课的特点和主要问题

2010-05-25 10:10:29 0

0 ASIC与大型逻辑设计实习课

AgendaCell Base IC DesignModelSimLibraryProjectVHDL Compiler & SimulationSimulation WindowsTutorialLab

2010-06-19 09:45:20 0

0 目的: 掌握基本组合逻辑电路的实现方法。

2010-07-17 16:29:17 12

12 第二十一讲 组合逻辑电路中的竞争冒险

6.7.1 竞争冒险现象及其产生的原因一、竞争、冒险1.理想情况2.实际情况3.竞

2009-03-30 16:25:35 3436

3436

组合逻辑电路的分析与设计-逻辑代数

在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路称为组合逻辑电路。

2009-04-07 10:07:57 3922

3922

组合逻辑电路的设计

组合逻辑电路的设计与分析过程相反,其步骤大致如下: (1)根据对电路逻辑功能的要求,列出真值表; (2)由真值表写出逻辑表达

2009-04-07 10:12:22 14015

14015

组合逻辑电路中的竞争冒险

前面分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。实际上,从信号输入到稳定输出需要一定的时间。由于从输入

2009-04-07 10:13:03 11802

11802

高速数字记录系统中光纤下载卡的逻辑设计

数据记录及下载系统如图1所示,雷达信号预处理机将采样到的信号进行一系列处理工作,最后形成一路或多路的光纤数

2010-02-02 16:41:48 1129

1129

为了提高温度保护系统的可靠性,在温度保护的逻辑设计中可采用容错设计,即尽可能考虑测温环节在运行中容易出现的故障,并通过预先设置的逻辑措施来识别错误的温度信号,以防保护系统误动。

2011-01-21 11:16:21 1854

1854

组合逻辑中的竞争与冒险及毛刺的处理方法 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的(冗余)消去项,但是不

2011-01-24 18:12:53 0

0 组合逻辑设计实例_国外:

2011-12-16 15:08:59 24

24 《数字电路与逻辑设计》答案

2012-06-25 08:19:15 23

23 华为静态时序分析与逻辑设计,基础的资料,快来下载吧

2016-09-01 15:44:10 57

57 在线座谈回放资料:5月27日 Altera 如何令逻辑设计在新一代CPLD中尽显优势 (问答记录)

2017-01-08 14:27:49 0

0 组合逻辑中的竞争与冒险及毛刺的处理方法

2017-01-17 19:54:24 7

7 使用标准集成电路的逻辑设计课题

2017-09-19 11:41:06 19

19 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 9235

9235 通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

2018-06-23 08:49:00 2095

2095

根据逻辑功能的不同,可把数字电路分为组合逻辑电路(Combinational Logic Circuit)和 时序逻辑电路(Sequential Logic Circuit)两大类。

2018-07-20 08:00:00 0

0 本文档的主要内容详细介绍的是数字电路基础之组合逻辑电路的详细资料概述包括了:1.组合逻辑电路的特点2.组合逻辑电路的分析与设计方法3.常用组合逻辑电路的工作原理及其应用 4.加法器、比较器、译码器、编码器、选择器5.组合逻辑电路中的竞争和冒险现象。

2018-10-17 08:00:00 0

0 本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

2019-03-27 10:56:04 20

20 组合逻辑电路是无记忆数字逻辑电路,其任何时刻的输出仅取决于其输入的组合.

2019-06-22 10:53:20 50945

50945

本文档的主要内容详细介绍的是Verilog HDL语言组合逻辑设计方法以及QuartusII软件的一些高级技巧。

2019-07-03 17:36:12 20

20 组合逻辑电路的设计就是将实际的,有因果关系的问题用一个较合理、经济、可靠的逻辑电路来实现。一般来说在保证速度、稳定、可靠的逻辑正确的情况下,尽可能使用最少的器件,降低成本是逻辑设计者的任务。本文将

2020-01-21 16:46:00 3470

3470

组合逻辑设计法适合于设计开关量控制程序,它是对控制任务进行逻辑分析和综合,将元件的通、断电状态视为以触点通、断状态为逻辑变量的逻辑函数,对经过化简的逻辑函数,利用PLC逻辑指令可顺利地设计出满足要求且较为简练的程序。这种方法设计思路清晰,所编写的程序易于优化。

2020-05-22 08:49:00 4637

4637 本文档的主要内容详细介绍的是数字电路与逻辑设计实验报告模板。

2020-06-05 08:00:00 8

8 机载机电管理系统的通道故障逻辑设计

2021-06-22 14:15:49 16

16 一、逻辑设计 (1)组合逻辑设计 下面是一些用Verilog进行组合逻辑设计时的一些注意事项: ①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表

2021-06-23 17:45:10 6056

6056

和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

2022-08-25 09:01:52 2434

2434 我在数字逻辑设计方面并没有经验。也就是说,直到最近我才决定尝试设计自己的 CPU,并在 FPGA 上运行!如果你也是一名软件工程师,并对硬件设计有兴趣,那么我希望这一系列关于我所学到的知识的文章能够对你有所帮助,并让你感到有趣。本系列文章的第一部分中,将回答以下问题:

2022-11-01 09:25:03 2703

2703 上文中我们指出,不管我们是创建自定义 ASIC 芯片还是配置 FPGA,都可以使用相同的数字逻辑设计工具。

2022-11-01 09:23:39 3201

3201 在组合逻辑电路中,由于门电路的输入信号经过的通路不尽相同,所产生的延时也就会不同,从而导致到达该门的时间不一致,我们把这种现象叫做竞争。由于竞争而在电路输出端可能产生尖峰脉冲或毛刺的现象叫冒险。

2022-12-09 09:23:31 2759

2759 本文介绍开发组合逻辑电路时可能发生的意外开关事件,称为危险。 本文是关于使用逻辑门进行组合电路设计和仿真的介绍性系列文章的第二部分。在上一篇文章中,我们介绍了 组合逻辑电路 以及如何简化它们

2023-01-27 14:18:00 2709

2709

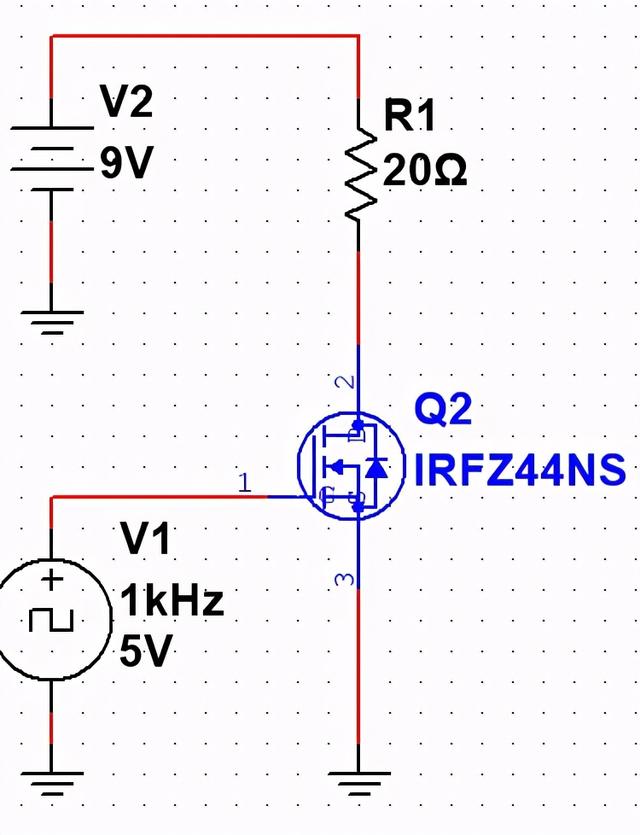

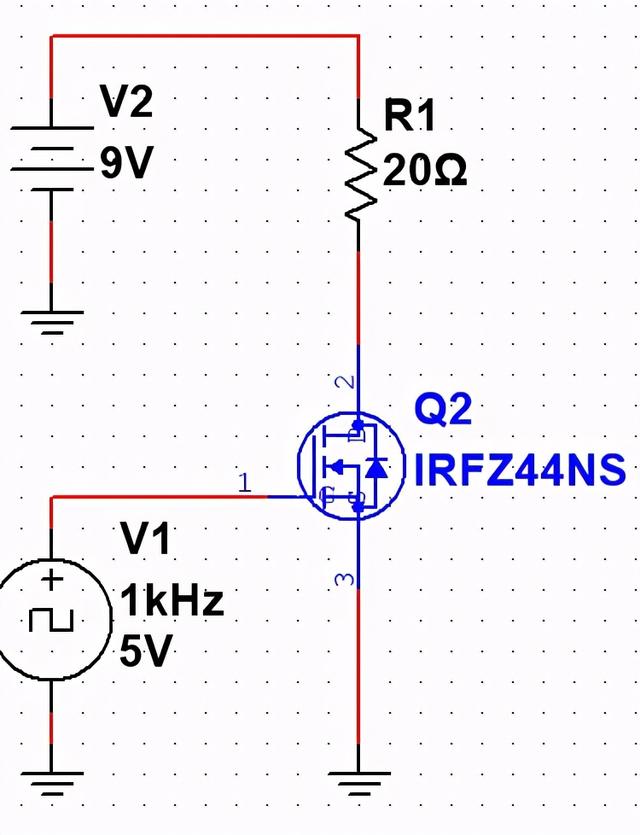

毛刺现象是我们每一个电子爱好者避之唯恐不及的,今天我们来学习一个毛刺现象以及如何规避它,进而掌握电感升压的原理。

2023-08-15 14:53:20 6590

6590

电子发烧友网站提供《基于TouchGFX的智能手表设计 —MVP 架构下的逻辑设计.pdf》资料免费下载

2024-01-05 11:21:38 1

1 当逻辑电路由多个逻辑门组成且不含存储电路,对于给定的输入变量组合将产生确定的输出,则这种逻辑电路称为组合逻辑电路。

2024-02-04 11:46:36 3337

3337

电子发烧友网站提供《数字电路与逻辑设计.ppt》资料免费下载

2024-03-11 09:21:44 12

12 电子发烧友网站提供《基于VHDL的组合逻辑设计.ppt》资料免费下载

2024-03-11 09:23:29 2

2 组合逻辑控制器是一种用于控制和管理复杂系统中各个组件之间交互的逻辑设备。它可以应用于各种领域,如计算机科学、通信、自动化控制等。在这篇文章中,我们将详细探讨组合逻辑控制器的实现方法、原理和应用。 一

2024-06-30 10:11:28 1147

1147

电子发烧友App

电子发烧友App

评论