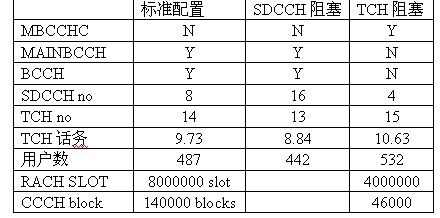

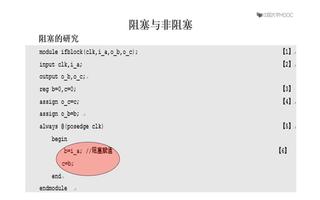

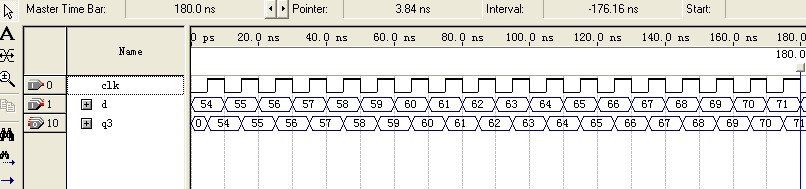

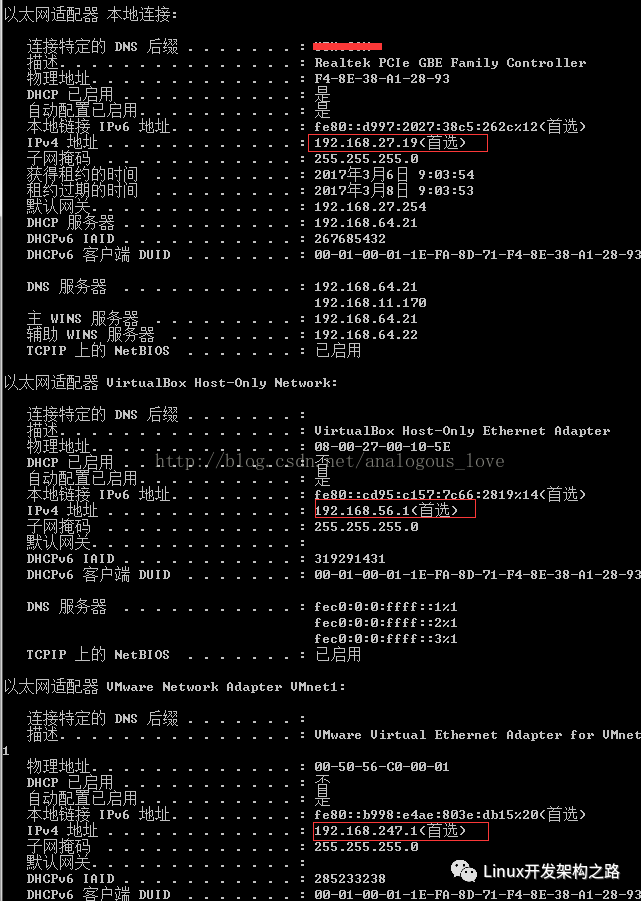

原文链接:学verilog 一个月了,在开发板上面写了很多代码,但是始终对一些问题理解的不够透彻,这里我们来写几个例子仿真出阻塞和非阻塞的区别,我们先上代码module LED ( CLK, RSTn, scan, flag , c, ,one,two,three,four); input CLK; input RSTn; input scan; output flag,c; output [3:0] one,two,three,four;/***********************************************************/ reg F1,F2; reg a,b; reg [3:0] one,two,three,four; /********************信号传递之间的非阻塞赋值***************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin F1 <= 1'b1; F2 <= 1'b1; end else begin F1 <= scan; F2 <= F1; end /*******************信号传递之间的阻塞赋值****************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin a = 1'b1; b = 1'b1; end else begin a = scan; b = a; end /******************数据加 非阻塞赋值 先判断后计数*****************************************/ always @ ( posedge CLK or negedge RSTn ) //one <= if( !RSTn ) begin one<=0; end else begin if(one==14) one<=0; else one<=one+1; end/***************数据加 非阻塞赋值 先计数后判断********************************************/ always @ ( posedge CLK or negedge RSTn ) // two<= if( !RSTn ) begin two<=0; end else begin two<=two+1; if(two==14) two<=0; end /**************数据加 阻塞赋值 先判断后计数*********************************************/ always @ ( posedge CLK or negedge RSTn ) //three = if( !RSTn ) begin three=0; end else begin if(three==14) three=0; else three=three+1; end/*************数据加 阻塞赋值 先计数后判断**********************************************/ always @ ( posedge CLK or negedge RSTn ) //four = if( !RSTn ) begin four=0; end else begin four=four+1; if(four==14) four=0; end /****************信号之间传递***********************/ assign flag = F2 & !F1;assign c = b & !a;/***************************************/ endmodule 2、我使用modesim 仿真,下面为我的 test bench `timescale 1 ps/ 1 psmodule LED_vlg_tst();// constants // general purpose registersreg eachvec;// test vector input registersreg CLK;reg RSTn;reg scan;// wires wire c;wire flag;wire [3:0] four;wire [3:0] one;wire [3:0] three;wire [3:0] two;// assign statements (if any) LED i1 (// port map - connection between master ports and signals/registers .CLK(CLK), .RSTn(RSTn), .c(c), .flag(flag), .four(four), .one(one), .scan(scan), .three(three), .two(two));/*initial begin // code that executes only once // insert code here --> begin // --> end $display("Running testbench"); end always // optional sensitivity list // @(event1 or event2 or .... eventn) begin // code executes for every event on sensitivity list // insert code here --> begin @eachvec; // --> end end endmodule*/initial beginCLK = 0;forever#10 CLK = ~CLK; endinitial beginscan = 0;forever#100 scan = ~scan; endinitial beginRSTn = 0;#1000 RSTn = 1;#1000;#1000;#1000;#1000;#1000;#1000;#1000;#1000;$stop;endendmodule 主要就是初始化一个CLK 和scan的信号,然后就是初始化一下复位,最后就是设置仿真时间,这样modesim 就不会一直处于仿真状态,消耗资源,也可以方便仿真。 其中quartus 与modesim 互相调用调试,可以关注我的博客,这里我就不具体讲解了! 3、modesim 波形图 大家注意到红线框内的数据变化,就能很清楚的理解 阻塞与非阻塞了! 微观分析 阻塞与非阻塞1、上代码,具体观察,a,b,c与F1,F2,flage 的变化 module LED ( CLK, RSTn, scan, flag , a,b,c,F1,F2,); input CLK; input RSTn; input scan; output flag,a,b,c; output F1,F2;/***********************************************************/ reg F1,F2; reg a,b; /***********************************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin F1 <= 1'b1; F2 <= 1'b1; end else begin F1 <= scan; F2 <= F1; end /***********************************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin a = 1'b1; b = 1'b1; end else begin a = scan; b = a; end /***********************************************************/ assign flag = F2 & !F1;assign c = b & !a;/***************************************/ endmodule 代码涵义就不讲解了 2、test bench 代码,与上面相同,这里不重复了 3、上图 看波形

深入分析verilog阻塞和非阻塞赋值

- Verilog(114289)

- 阻塞(8403)

- 非阻塞(2357)

相关推荐

热点推荐

FPGA基础篇(一):阻塞与非阻塞赋值,不只是比原始信号差一个时钟周期的问题!(深入剖析)

阻塞与非阻塞赋值 首先从名字上理解,阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看

2017-09-19 18:32:43 14061

14061

14061

14061Verilog语言中阻塞和非阻塞赋值的不同

来源:《Verilog数字系统设计(夏宇闻)》 阻塞和非阻塞赋值的语言结构是Verilog 语言中最难理解概念之一。甚至有些很有经验的Verilog 设计工程师也不能完全正确地理解:何时使用非阻塞

2021-08-17 16:18:17 7048

7048

7048

7048在testbench中如何使用阻塞赋值和非阻塞赋值

本文详细阐述了在一个testbench中,应该如何使用阻塞赋值与非阻塞赋值。首先说结论,建议在testbench中,对时钟信号(包括分频时钟)使用阻塞赋值,对其他同步信号使用非阻塞赋值。

2025-04-15 09:34:24 1092

1092

1092

1092

Verilog HDL语言编程的误区与经验

Verilog的两个误区:使用Reg类 型还是Net类型:Reg类 型只在过程块中被赋值;而Net类型则在过 程块外面被赋值或者驱动.阻塞赋值和非阻塞赋值:Verilog中竞争发生的条件:两个或多个

2019-03-26 08:00:00

Verilog阻塞和非阻塞原理分析

Verilog阻塞和非阻塞原理分析在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行

2009-11-23 12:02:57

Verilog中阻塞赋值和非阻塞赋值的正确使用

[table][tr][td] Verilog中有两种为变量赋值的方法。一种叫做连续赋值,另一种叫做过程赋值。过程赋值又分为阻塞赋值和非阻塞赋值。阻塞性赋值使用“=”为变量赋值,在赋值结束前不可以进行其他操作,在赋值结束之后继续后面的操作。这个过程就好像阻断了程序的运行。非阻塞赋值使用“

2018-07-03 03:06:04

Verilog流水线加法器always块中应该采用阻塞赋值(=),还是非阻塞赋值(<=)?

图一图二图三图四最近写了一个16位二级流水线加法器,并进行了一下仿真。发现在always块中采用阻塞赋值(=)和非阻塞赋值(

2016-09-09 09:18:13

Verilog过程赋值语句提问

时,dreg还是变成了areg这样不就是延时3个时钟周期了吗?为什么不是这样呢?另外,阻塞型赋值语句,规定是,顺序执行语句,每种状态一个接一个执行,非阻塞型赋值语句,规定是,并行赋值语句,当执行语句时同事计算

2017-09-20 15:10:01

verilog 非阻塞赋值的综合

刚学verilog,试了一下非阻塞赋值,代码如下, 很简单module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

verilog中的阻塞和非阻塞

这个是非阻塞赋值,b的值为0,仿真结果也是0module TOP(input clk,input rst,output reg b );reg a,c;always@(posedge clk or negedge rst)beginif(~rst)begina

2015-09-13 15:55:05

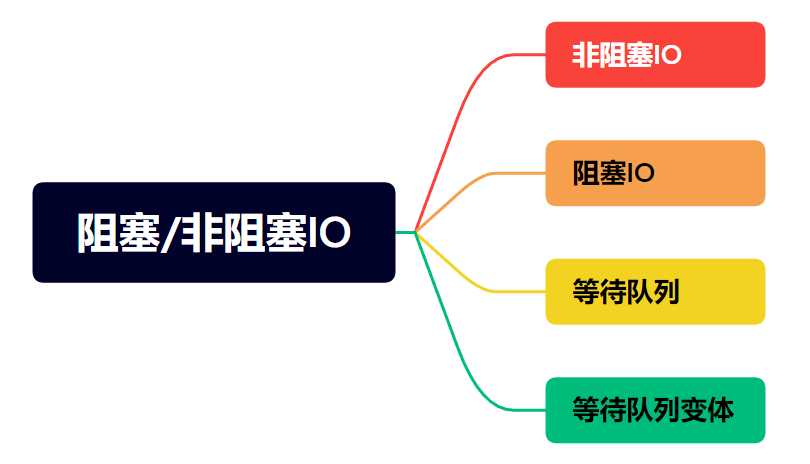

阻塞与非阻塞I/O

里面,因为硬件资源获得的同时往往伴随着一个中断。 注意:驱动程序需要提供阻塞(等待队列,中断)和非阻塞方式(轮询,异步通知)访问设备。 休眠(被阻塞)的进程处于一个特殊的不可执行状态。这点非常重要,否则

2018-07-09 08:19:59

阻塞(=)与非阻塞(<=)介绍

语句的执行,延迟后才执行赋值,这种赋值语句是不可综合的,在需要综合的模块设计中不可使用这种风格的代码。 非阻塞赋值操作符用小于等于号(即

2018-07-03 10:23:19

阻塞(=)与非阻塞(<=)介绍

语句的执行,延迟后才执行赋值,这种赋值语句是不可综合的,在需要综合的模块设计中不可使用这种风格的代码。 非阻塞赋值操作符用小于等于号(即

2018-07-09 05:08:55

非阻塞赋值容易错语法点讨论

本帖最后由 eehome 于 2013-1-5 10:05 编辑

非阻塞赋值容易错语法点讨论请教下大家!我发现光盘里的例程有一段是这样子的:always @(dac_sta

2012-12-22 09:53:14

FPGA在阻塞赋值中说是前边赋值阻塞后边赋值,但是看波形是同时变化

1,在阻塞赋值中,说是前边赋值阻塞后边赋值,但是看波形明明是同时变化,这是为什么?2,在if ,else if, else语句中说是顺序执行,是时钟跳一个周期判断一次吗,还是同时判断,如果是同时判断为什么说是顺序执行?3,是组合逻辑中用=,非组合逻辑中用

2019-05-29 01:09:27

fpga基础篇(一):阻塞与非阻塞赋值

`阻塞与非阻塞赋值首先从名字上理解,阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看

2017-04-05 09:53:11

linux串口通信阻塞与非阻塞问题。

一般情况下串口通信中read()函数都是阻塞的。当然也可以通过设置文件等方法把串口设为非阻塞的。这里就有一个问题,当串口设置为阻塞状况下,如果读不到数据程序应该挂起。这种所谓的读不到数据是指读不到

2011-07-14 15:57:26

【FPGA学习】Verilog HDL的过程性赋值如何写

语句完成执行;• 非阻塞性过程赋值:对目标的赋值是非阻塞的(因为时延),但可预定在将来某个时间发生。阻塞性过程赋值用操作符“=”完成,例如下面的实例:always@ (A or B or Cin

2018-09-26 09:16:55

【FPGA开源教程连载】第六章 阻塞赋值与非阻塞赋值

阻塞赋值与非阻塞赋值原理分析实验目的:掌握阻塞赋值与非阻塞赋值的区别实验平台:无实验原理:阻塞赋值,操作符为“=”,“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后

2016-12-25 01:51:24

【分享】Verilog中阻塞与非阻塞语句

移位寄存器:如果把上述代码中的两个赋值语句相互交换,如下所示,结果和上面是一样的。所以在一个begin---end中的非阻塞语句并不会因为放置的位置不同,出现不同的结果。关于非阻塞的例子,分析的貌似蛮

2016-11-03 20:26:38

【工程源码】 阻塞赋值与非阻塞赋值原理分析

的赋值语句会阻断其后语句的正常执行,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。非阻塞赋值,操作符为“

2020-02-24 20:09:13

【技巧分享】FPGA至简设计-阻塞赋值与非阻塞赋值

阻塞与非阻塞作者:小黑同学一、 概述1、阻塞赋值对应的电路往往与触发沿没有关系,只与电平的变化有关系。阻塞赋值符号“=”。2、非阻塞赋值对应的电路结构往往与边沿触发有关系,只有在触发沿时才有可能发生赋值的情况。非阻塞赋值符号“

2020-04-24 14:49:45

【连载视频教程(六)】小梅哥FPGA设计思想与验证方法视频教程之例解阻塞赋值与非阻塞赋值

,主要通过简单的例子对比了Verilog语法中阻塞赋值和非阻塞赋值的区别,通过证明非阻塞赋值多种赋值顺序生产电路的唯一性,与非阻塞赋值多种赋值书序生成电路的不确定性,来展示使用非阻塞赋对设计可预测性

2015-09-24 14:02:15

使用非阻塞的方式来处理并发的情况

如果我们要处理的情况符合下面的几种之一,我们可以考虑一下使用非阻塞的方式来处理并发的情况。有多线程的情况要处理,但是很少出现并发冲突的,比如以读取为主的涉及到的并发逻辑非常复杂,希望可以减低并发代码

2021-08-24 08:11:32

关于阻塞性赋值与非阻塞性赋值的困惑

@ (posedge GlobalClk)RegC = RegB;由于过程性赋值立即发生,即没有任何时延,所以根据首先执行哪一条always语句,RegC取不同的值,这就产生了竞争。书上说使用非阻塞性赋值可以避免产生竞争状态,为什么??求助...

2013-11-07 10:16:34

关于串口读写阻塞,没有设置非阻塞标志,为什么还能继续打印

我打开这个串口的时候没有设置非阻塞的标志,应该是默认阻塞的吧,但是上位机不向串口发送东西,也就是read没有读到东西的时候下面的printf还是会一直打印。我理解的阻塞就是程序一直等待在阻塞的地方,是不是我理解的有问题

2017-03-15 16:51:06

初学者读夏宇闻老师书上一个问题,是关于阻塞赋值和非.....

阻塞赋值操作符用等号(即 = )表示。为什么称这种赋值为阻塞赋值呢?这是因为在赋值时先计算等号右手方向(RHS)部分的值,这时赋值语句不允许任何别的 Verilog 语句的干扰,直到现行的赋值

2013-10-28 15:44:13

在verilog语句中,非阻塞赋值和小于等于均使用符号“<=”,如何区分<=所表示的含义?

)中,\"<=\"作为非阻塞赋值的一部分。

verilog中,一个语法结构不可能同时允许“表达式”和“语句”,

如果某处可以出现表达式,那么就不允许出现语句;

如果

2023-08-08 09:32:07

请问如何从阻塞过渡到非阻塞I2C?

使用 _IT 函数转移到一个非阻塞系统。只是将传输命令从 HAL_I2C_Master_Transmit 更改为 HAL_I2C_Master_Transmit_IT 突然将我所有的结果变成了屏幕上的乱码,而不是像我以前那样漂亮的文本。我需要做什么才能从阻塞 I2C 命令变为非阻塞 I2C 命令?

2023-02-06 06:00:18

飞凌嵌入式ElfBoard-文件I/O的深入学习之阻塞I/O与非阻塞I/O

可能会使程序阻塞等待,直到有数据可读时才会被唤醒返回。

普通文件的读写操作是不会阻塞的,不管读写多少个字节数据,read或 write一定会在有限的时间内返回,所以普通文件一定是以非阻塞的方式进行I/O

2025-12-01 13:07:30

Java非阻塞通信研究

本文针对Java NIO 的特性做出分析与阐述,对网络应用中阻塞通信与非阻塞通信、NIO的非阻塞工作机制以及网络通信中非阻塞套接字的实现等问题进行了研究和探讨,提出了系统地

2009-08-10 10:15:22 18

18

18

18GSM小区话务均衡及解决网络阻塞策略

本文详细的分析了网络阻塞产生的原因,并从基站硬件和网络参数上讨论了解决阻塞的一些方法。而且通过优化实例的说明能够有效的减少网络阻塞,提高话务量。<关键

2009-06-02 07:28:48 3244

3244

3244

3244

verilog中阻塞赋值和非阻塞赋值

阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别

2011-03-15 10:57:34 7239

7239

7239

7239Verilog非阻塞赋值仿真

原标题:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括号内外注为理解方便或有疑问的地方,原文里并没有。所有翻译都是为遵循共同进步的理想但并没有去努力得

2011-03-29 16:25:53 0

0

0

0Verilog HDL阻塞属性探究及其应用

本文通过Verilog事件处理机制,详细讨论了阻塞与非阻塞赋值的区别、联系及其应用示例。由本文可知,阻塞与非阻塞赋值灵活多变,底层实现也差异甚大。因而在数字电路设计时,依据

2011-08-28 17:59:19 862

862

862

862

Verilog编码中的非阻塞性赋值

One of the most misunderstood constructs in the Verilog language is the nonblockingassignment. Even

2012-01-17 11:28:13 0

0

0

0非阻塞模式LCD多级菜单实现与应用

提出一种非阻塞模式LCD多级菜单的设计,分析了菜单的树形结构,给出了菜单的状态转换模型及其菜单的核心数据结构. 并分析菜单实现算法的较小空间复杂度和给出了其数据结构的C51的实

2012-02-15 09:58:04 38

38

38

38Verilog HDL阻塞属性简介

VerilogHDL 中,有两种过程赋值方式,即阻塞赋值(blocking)和非阻塞赋值(nonblocking)。阻塞赋值执行时,RHS(righthandstatement)估值与更新LHS(lefthandstatement)值一次执行完成,计算完毕,立即更新。

2012-05-23 09:55:51 1598

1598

1598

1598

veriolg中阻塞赋值与非阻塞赋值区别

在一开始学到阻塞和非阻塞的时候,所被告知的两者的区别就在于阻塞是串行的,非阻塞是并行的。但是虽然知道这个不同点,有些时候还是很难真正区分用两者电路的区别,下载资料内以一个简单的串行流水线寄存器为例进行了分析。

2017-09-16 09:34:07 4

4

4

4从I/O的阻塞与非阻塞、I/O处理的单线程与多线程角度探讨服务器模型

这里探讨的服务器模型主要指的是服务器端对I/O的处理模型。从不同维度可以有不同的分类,这里从I/O的阻塞与非阻塞、I/O处理的单线程与多线程角度探讨服务器模型。

2018-01-08 16:13:51 7638

7638

7638

7638FPGA学习系列:5.阻塞赋值与非阻塞赋值

设计背景: 阻塞 (=)和非阻塞(=)一直是在我们FPGA中讨论的问题,资深的学者都是讨论的是赋值应该发生在上升下降沿还是在哪里,我们在仿真中看的可能是上升下降是准确的,但是在时间电路中这就

2018-05-31 11:40:14 7425

7425

7425

7425

数字设计FPGA应用:阻塞与非阻塞

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:06:00 2289

2289

2289

2289

阻塞赋值和非阻塞赋值的用法一篇文章就够了

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2020-01-30 17:41:00 22571

22571

22571

22571verilog中阻塞赋值和非阻塞赋值到底有什么区别

1、阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。

2020-04-25 08:00:00 0

0

0

0IEEE Verilog阻塞赋值和非阻塞赋值的区别

阻塞赋值对应的电路往往与触发沿没有关系,只与输入电平的变化有关系。非阻塞赋值对应的电路结构往往与触发沿有关系,只有在触发沿时才有可能发生赋值的情况。

2020-06-17 11:57:41 12065

12065

12065

12065

VerilogHDL语言:清阻塞赋值和非阻塞赋值

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微

2020-11-19 15:48:56 1533

1533

1533

1533基于阻塞赋值和非阻塞赋值的多级触发器级联实例

下面给出一个基于阻塞赋值和非阻塞赋值的多级触发器级联实例,要求将输入数据延迟 3 个时钟周期再输出,并给出对应的 RTL 级结构图和仿真结果。 (1)基于 D触发器的阻塞赋值语句代码如下

2021-05-08 14:47:05 2720

2720

2720

2720

简述阻塞赋值和非阻塞赋值的可综合性

阻塞赋值和非阻塞赋值的可综合性 Blocking Assignment阻塞赋值和NonBlocking Assignment非阻塞赋值,原本是软件进程管理的术语。由于Verilog团队是从C语言发展

2021-05-12 09:45:09 3264

3264

3264

3264

简述Verilog HDL中阻塞语句和非阻塞语句的区别

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。 Verilog语言中讲的阻塞赋值与非

2021-12-02 18:24:36 7318

7318

7318

7318

Verilog进行组合逻辑设计时的注意事项

由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”,原因将在“阻塞赋值和非阻塞赋值”中(现在还没有写)进行说明。

2022-03-15 10:40:20 2843

2843

2843

2843Verilog设计过程中的一些经验与知识点

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括块语句、阻塞赋值和非阻塞赋值 以及结构说明语句(initial, always, task, function)。”

2022-03-15 12:19:31 2954

2954

2954

2954时序逻辑中的阻塞和非阻塞

Verilog HDL的赋值语句分为阻塞赋值和非阻塞赋值两种。阻塞赋值是指在当前赋值完成前阻塞其他类型的赋值任务,阻塞赋值由=来完成;非阻塞赋值在赋值的同时,其他非阻塞赋值可以同时被执行,非阻塞赋值由《=来完成。

2022-03-15 13:53:08 3700

3700

3700

3700在时序逻辑中使用阻塞赋值会怎么样?

如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发,综合器推断时序逻辑。如前所述,所有阻塞赋值都在活动队列中进行计算和更新。读者请参阅之前分享的分层事件队列一文。

2022-09-06 09:44:02 4895

4895

4895

4895verilog中阻塞赋值和非阻塞赋值的区别

阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。

2022-12-19 16:49:28 9353

9353

9353

9353Verilog中阻塞和非阻塞赋值金规

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章的用法。其实,有时候概念稍微不清楚,Bug就会找到我们,下面一文扫清阻塞赋值和非阻塞赋值所有的障碍。

2023-06-01 09:21:57 2708

2708

2708

2708阻塞与非阻塞通信的区别 阻塞和非阻塞应用场景

阻塞通信(Blocking Communication):当进行阻塞通信时,调用者在发起一个I/O操作后会被阻塞,直到该操作完成返回才能继续执行后续代码。

2023-06-15 17:32:21 7290

7290

7290

7290虹科分享|关于阻塞函数和非阻塞函数

关于阻塞函数和非阻塞函数在CAN和LIN相关的开发库里,不可避免的会出现“收”和“发”的函数。如何快速有效的处理数据,是开发中重要的事项。

2022-07-05 14:38:43 2031

2031

2031

2031

网络IO模型:阻塞与非阻塞

阻塞 IO 模型 在Linux ,默认情况下所有的 socket 都是阻塞的,一个典型的读操作流程如图所示。 阻塞和非阻塞的概念描述的是用户线程调用内核 IO 操作的方式:阻塞是指 IO 操作需要

2023-10-08 17:16:51 1570

1570

1570

1570

什么是阻塞?怎么设计才能满足阻塞指标?

阻塞就是外部有阻塞干扰信号的时候,设备还可以正常运行。一般分为带内阻塞和带外阻塞,由于直放站都是做宽带设备,一般只提带外阻塞。

2023-10-10 11:22:37 3968

3968

3968

3968非阻塞的的connect()函数如何编写

由于网络编程涉及很多细节和技巧,一直想写篇文章来总结下这方面的心得与经验,希望对来者有一点帮助,那就善莫大焉了。 一、非阻塞的的connect()函数如何编写 我们知道用connect()函数默认

2023-11-11 16:23:29 2725

2725

2725

2725

verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别

Verilog是一种硬件描述语言,用于设计和模拟数字电路。在Verilog中,同步和异步是用来描述数据传输和信号处理的两种不同方式,而阻塞赋值和非阻塞赋值是两种不同的赋值方式。本文将详细解释

2024-02-22 15:33:04 2897

2897

2897

2897socket阻塞和非阻塞的区别是什么

在计算机编程中,socket 是一种通信端点,用于在网络中进行数据传输。Socket 可以是阻塞的或非阻塞的,这两种模式在处理数据传输时有不同的行为。 阻塞模式(Blocking Mode) 在阻塞

2024-08-16 11:13:43 1721

1721

1721

1721SystemView上下文统计窗口识别阻塞原因

SystemView工具可以记录嵌入式系统的运行时行为,实现可视化的深入分析。在新发布的v3.54版本中,增加了一项新功能:上下文统计窗口,提供了对任务运行时统计信息的深入分析,使用户能够彻底检查每个任务,帮助开发人员识别阻塞原因。

2024-08-20 11:31:18 990

990

990

990socket编程中的阻塞与非阻塞

在网络编程中, socket 是一个非常重要的概念,它提供了一个抽象层,使得开发者可以不必关心底层的网络通信细节。 socket 编程中的阻塞与非阻塞模式是两种不同的操作方式,它们对程序的响应性

2024-11-01 16:13:15 1154

1154

1154

1154 电子发烧友App

电子发烧友App

评论