FPGA/ASIC技术

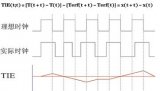

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。PLL和DLL:都是锁相环,区别在哪里?

一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的...

2017-02-11 13907

FPGA全局时钟和第二全局时钟资源的使用方法

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局...

2017-02-11 5519

Verilog设计中的一些避免犯错的小技巧

这是一个在设计中常犯的错误列表,这些错误常使得你的设计不可靠或速度较慢,为了提高你的设计性能和提高速度的可靠性你必须确定你的设计通过所有的这些检查。...

2017-02-11 845

赛灵思DCM概述和应用技巧

DCM:即 Digital Clock Manager 数字时钟管理,关于DCM的作用: 顾名思义DCM的作用就是管理,掌控时钟的专用模块。...

2017-02-11 1953

赛灵思Verilog(FPGA/CPLD)设计技巧

以下是一个在设计中常犯的错误列表这些错误常使得你的设计不可靠或速度较慢为了提高你的设计性能和提高速度的可靠性你必须确定你的设计通过所有的这些检查 。...

2017-02-11 1503

基于verilog的FPGA编程经验总结

用了半个多月的ISE,几乎全是自学起来的,碰到了很多很多让人DT好久的小问题,百度也百不到,后来还是都解决了,为了尽量方便以后的刚学ISE的童鞋不再因为一些小问题而纠结,把这几天的...

2017-02-11 1792

多核处理器会取代FPGA吗?

有人认为诸如图形处理器(GPU)和Tilera处理器等多核处理器在某些应用中正逐步替代现场可编程门陈列(FPGA)。理由是这些多核处理器的处理性能要高很多,例如,由于GPU起初主要负责图形绘...

2017-02-11 1418

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

最近在写代码的时候总是在思考,我写的这个能被综合吗?总是不放心,或是写完了综合的时候出问题,被搞的非常烦恼,虽然看了一些书,比如对组合逻辑用阻塞赋值,时序用非阻塞赋值,延...

2017-02-11 7185

在FPGA开发中尽量避免全局复位的使用?(5)

在FPGA设计中,我们往往习惯在HDL文件的端口声明中加入一个reset信号,却忽略了它所带来的资源消耗。仔细分析一下,竟会有如此之多的影响:...

2017-02-11 1324

在FPGA开发中尽量避免全局复位的使用?(4)

在某种意义上讲,这是一个上电之后的“终极的”全局复位操作,因为它不仅仅是对所有的触发器进行了复位操作,还初始化了所有的RAM单元。...

2017-02-11 772

在FPGA开发中尽量避免全局复位的使用?(3)

好消息是,在绝大多数设计中(白皮书说是超过99.99%?应该是老外写文档的习惯吧),复位信号的时序是无关紧要的——通常情况下,大部分电路都能够正常工作。...

2017-02-11 633

ISE13.1调用Modelsim10.0出现的一点小问题及解决过程

在System Generator做了点仿真,验证成功之后,自动生成了testbench文件,然后在ISE中打开生成的工程,调用Modelsim选择behavior仿真.........

2017-02-11 2424

如何在ISE中更新老版本的IP核

在ISE中打开以前做的一个工程时,总是不停地提示 INFO:sim:760 - You can use the CORE Generator IP upgrade flow to upgrade the selected IP Block_Memory_Generator v3.1 to a more recent version....

2017-02-11 4865

Intel的22nm 3D工艺牛,到底牛到什么程度?

intel的22nm 3D工艺牛,到底牛到什么程度,到底对业界有神马影响,俺也搞不太清楚。这不,一封email全搞定了。...

2017-02-11 1758

基于FPGA的交流电机驱动器的电流控制器4

之所以利用FPGA来实现控制功能,主要是为了充分利用其并行性,从而极大地降低计算延时。在高性能的电机调速系统中(此时控制系统的成本增加相比其整体成本可以忽略),将极大地提供控...

2017-02-11 1191

基于FPGA的交流电机驱动器的电流控制器3

正如之前所提到,仿真步骤在Matlab-simulink软件环境中已经演示过。它的目标是: 改变完整的控制系统的功能;根据控制系统的缺陷所需,找到每个控制变量合适的采样周期和定点格式改进。...

2017-02-11 1421

基于FPGA的交流电机驱动器的电流控制器2

FPGA技术允许在灵活的设计环境内开发特别的硬件结构。相比微处理器和DSP处理器的标准结构来说,FPGA的这项特点给设计者有了很大的自由度,这是因为它能建立特别的硬件结构,如此去匹配一...

2017-02-11 1250

基于FPGA的交流电机驱动器的电流控制器1

本文的主要目的在于讲述在数字控制器中使用FPGA作为组成部分的好处。出于这个目的,各种应用于直流电机驱动器的电流控制技术得到了设计和实施。...

2017-02-11 2063

一种基于FPGA的PXA270外设时序转换接口设计

ARCNET协议应用于高速动车组列车通信网络时,产生中央控制单元处理器PXA270与专用协议控制器件COM20020相连的时序不匹配问题,若用通用数字电路模块进行时序转换,PXA270需占用PXA270专门的资源...

2017-02-11 1452

利用Zynq SoC的片上存储空间实现AMP通信

上周我们实现了AMP(非对称多进程处理)模式,并且在ZynqSoC上实现了系统的启动和运行,在ZynqSoC的两个ARM Cortex-A9 MPCore处理器上尝试了最基本的软件应用。...

2017-02-11 7417

裸机AMP(非对称多进程处理模式)

在上一篇博客中,我们已经将Zynq SoC启动并运行起来,在AMP(非对称多进程处理)模式下使用了两个ARM Cortex-A9 MPCore处理器,然而因为上一篇博客已经相当长了,我没有详细的介绍软件方面的工...

2017-02-11 3962

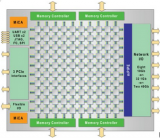

在Zynq SoC上实现双核非对称的多进程处理模式

在我的上一篇博客中我介绍了利用Zynq SoC上的两个ARM Cortex-A9 MPCore处理器执行不同的任务程序,实现非对称的多进程处理模式的概念。...

2017-02-11 3324

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |