FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。Petalinux的网络数据传输性能测试

介绍一种针对MicroBlaze软核处理器特别开发的嵌入式操作系统Petalinux,成功地实现了其在ML507开发板上的移植,并且通过LabVIEW软件在该系统上实现了基于TCP/IP协议的网络数据收发。同时,测试了...

2017-11-17 2801

利用捷变收发器来简化SDR平台设计复杂度并提高实际运算效能

有鉴于软件定义无线电(SDR)平台是实现5G等先进通讯系统不可或缺的工具,半导体厂推出专为SDR应用量身打造的新一代捷变(Agile)收发器射频芯片,其整合模拟讯号处理与强大滤波功能于小巧且低...

2017-11-17 2597

基于FPGA的智能卡验证平台设计

随着集成电路设计技术的发展和芯片集成度的提高,验证已经成为芯片设计流程中的主要瓶颈。本文设计了一个基于FPGA的智能卡验证平台,并对验证方法做了详细阐述。本文对于双界面智能卡...

2017-11-17 1469

基于Xilinx Zynq的物距测量系统设计与实现

为了对障碍物距离精确测量,基于最新Zedboard FPGA(现场可编程逻辑阵列)开发板,采用软硬件协同的设计 方法,设计了障碍物距离测量系统的软硬件。系统为智能小车平台提供了完整的距离测...

2017-11-17 2183

Xilinx Zynq-7000系列安全配置策略

ZYNQ7000与传统FPGA有着巨大的差异,它将自己定位为一款All Programmable Soc(软硬件可编程片上系统),视其为以FPGA作为外设的双核ARM A9处理器更加准切。它的启动过程体现了以处理器为核心这一特...

2017-11-17 10562

基于Zynq平台的动态智能家居系统的设计

由于传统智能家居无线传感器网络中传感器位置固定,需要布置的网络节点个数太多导致成本太高.鉴于以上原因,为了实现在减少Zigbee网络节点的前提下,又能实时捕捉用户所需信息的目标,...

2017-11-17 2639

基于FPGA的高精度同步时钟系统设计

介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时...

2017-11-17 8860

基于FPGA的速度和位置测量板卡的设计与实现

针对增量式光电编码器经典速度测量算法M/T法低速采样时间过长和位置测量算法精度不高的问题,本文基于定采样周期M/T法设计实现了速度和位置测量板卡。采用Xilinx公司的XC3S400 FPGA为核心控制...

2017-11-17 3082

SDN网络感知服务与最短路径的结构和分析以及流量统计

在一个真实的网络环境下,需掌握网络的实时动态,包括网络的资源以及网络流量状况,其中网络的信息包括交换机,端口,主机的信息,以及基于流的流量统计信息和基于端口的流量统计信息...

2017-11-17 2650

ADC中的数字下变频的分析和其高性能优势

高速ADC 现已具备足够的处理能力将DDC 功能带入信号链。如果系统不需要使用宽频带奈奎斯特率ADC 的完整带宽,则可通过DDC 滤除不想要的数据和噪声。这样能改善信号采集的SNR 和SFDR。较低的带...

2017-11-17 11484

SoC平台设计与DSP系统生成器相结合产生高性能的平台连接功能

FPGA 的应用不断拓展,同时FPGA 设计流程也随之不断演进。我们不再将FPGA 用作简单的胶合逻辑,甚至不再作为信号处理链的核心,用以将IP 与专有后端接口集成。相反,FPGA 正在转变为可编程片...

2017-11-17 1573

掌控频域的分析变换和其计算

一般在电子系统中,需要考查的信号是一个不断变化的电压、电流或频率。它可以是传感器的输出,也可能是系统其他部分生成的输出。在时域中,您可以测量信号的幅度、频率和周期,以及信...

2017-11-17 9495

使用FPGA优化视频水印操作的OpenCL应用

赛灵思SDAccel开发环境为内存限制问题提供优化方法.视频流和下载通常会耗掉消费者绝大部分互联网流量,同时也是云计算技术发展的主要推动力。对视频流和下载需求的持续增长,正在驱动视...

2017-11-17 1165

基于SDAccelTM 开发环境减少FPGA在应用中使用时造成的障碍

FPGA 一直有望超越CPU 和GPU 实现方案,拥有更高的算法性能以及更低的功耗范围。但直到现在因为编程模式未能如愿以偿。而这一编程模式又是有效利用FPGA 所必须的。SDAccel 支持具备系统内即时...

2017-11-17 1344

利用Digilent Spartan-3 优秀性能来实现Oberon系统

Digilent Spartan-3 开发板是由于其成本低、操作简便,这使其适于教育机构,以获得整套课堂教学套件。一个重大优势就是该开发板上有静态RAM,使得接口连接非常简单直观(甚至用于字节选择)...

2017-11-17 1713

基于各种用户自定义的测试数据序列来评估RF-DAC多频带发射器线性性能

在原型设计的早期阶段,关键RF 组件的线性性能评估是一个关键问题,但通过我们的软硬件平台,在不影响性能的条件下可以快速进行这项评估。然后,可以添加RF 功率放大器并使用所建议的平...

2017-11-17 2628

“ 大白兔”: 实现超高精度时间传输以及无损的全面数据传输

“大白兔”是一项前景光明的技术,能够解决智能电网、电信以及高频率交易等各类终端应用领域的同步需求问题。“大白兔”不仅能解决相位同步等问题,同时还能以亚纳秒精度为分布在遥远...

2017-11-17 9719

基于Xllinx Vivado HLS的小型无人机平衡仪设计

小型无人机在航拍、灾害救援、防火等领域得到广泛运用,但是无人机操作复杂,尤其是控制飞行姿态平稳、航线准确和降落平滑,对地面人员的操作水平要求较高。操作问题容易造成无人机的...

2017-11-17 2437

ucos iii在zynq上的移植

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置ZYNQ处理器系统以及FPGA架构集成软外设。然后,您将使用μ...

2017-11-17 9323

加速器一致性接口

Zynq PS上的加速器一致性接口(Accelerator Coherency Port, ACP)是一个兼容AXI3的64位从机接口,连接到SCU(Snoop Control Unit),为PL提供异步缓存一致性直接访问PS的入口。处理器可以标记ACP上的传输为一...

2017-11-17 4440

机器视觉边缘检测算法步骤

本文解读边缘检测相关算法的步骤。 1、滤波:边缘检测算法主要是基于图像强度的一阶和二阶导数,但导数的计算对噪声很敏感,因此必须使用滤波器来改善与噪声有关的边缘检测器的性能。...

2017-11-17 4324

基于ARM与神经网络处理器的存储体的数据交换的通信方案

首先介绍了人工神经网络的模型和算法以及FPGA的实现,并通过对网络结构的分析设计了FPGA端的数据存储系统。然后分析了ARM端和FPGA端各自的功能,在此基础上把两者结合在一起,设计了一种利...

2017-11-17 2145

提升网络容量/传输率 5G转向高密度小基站组网设计

小型基地台将走红5G通讯世代。5G通讯网络将一改过去高度仰赖大型基地台的布建架构,而大量使用小型基站,让电信营运商能以最具成本效益的方式弹性组网,从而提高网络密度与覆盖范围,...

2017-11-17 3860

自定义NI电网自动化系统

本篇技术白皮书提供了可用于修改NI电网自动化系统(NI Grid Automation System)随附功能或重新编程系统功能的一系列可用开发工具和IP核。 1. NI应用程序功能 NI电网自动化系统随附了一个默认功能,...

2017-11-17 1476

支持25G/28G背板运作 FPGA实现TB级网络应用突破

Romi Mayder/Frank Melinn (任职于赛灵思) 早在两年前IEEE报告就指出,2015年通讯网络的传输容量要求将达1Tbit/s,到2020年更必须支持到10Tbit/s。 该报告还指出,2015年固网和行动网络装置数量将多达一百...

2017-11-17 3164

什么是NI电网自动化系统?NI电网自动化系统介绍

本白皮本提供了NI电网自动化系统(NI Grid Automation System)的概述以及设计该系统时所采用的NI技术的深层解析。 1. NI电网自动化系统概述 NI电网自动化系统是一款可编程的智能电子设备(IED),专为简...

2017-11-17 2637

JESD204B与LVDS接口并行 管线式ADC延迟问题分析及解答

JESD204B为业界标准序列通信链接,数据转换器与现场可编程门阵列(FPGA)、数字信号处理器(DSP)、特定应用集成电路(ASIC)等装置间的数字数据接口因此能化繁为简,这项标准减少装置间路由进而降...

2017-11-17 3942

如何在Xilinx FPGA上快速实现JESD204B?操作步骤详细说明

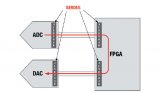

JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的 B 修订版支持高达 12.5 Gbps串行数据速率,并可确保 JESD204 链路具有可重复的确定性延迟。随着转换器的速度和分辨...

2017-11-17 7223

Zynq的JPEG图像压缩系统对图像的有效压缩、较低损失的实现方法

介绍了基于Zynq平台实现的JPEG图像压缩系该系统利用Zynq片上AXI总线实现了ARM与FPGA核间高吞吐率的数据交互操作,并结合了ARM和FPGA在嵌入式系统开发中各自的优势,对软硬件功能的实现进行了明...

2017-11-17 8268

FPGA开发之算法开发System Generator

现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4. Vivado HLS。 本文主要讲述第二种方法的配置方法。 system Generator Sy...

2017-11-17 8990

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |