FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。基于FPGA的振动信号采集系统设计及实现

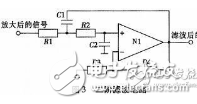

针对机械设备运行中的振动监控,设计振动信号采集系统,提出了一种基于FPGA的振动信号采集系统的设计方案。重点阐述了系统硬件结构组成、信号调理电路和数据采集模块的设计,同时对A...

2017-11-17 8521

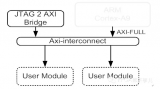

谈JTAG to AXI Master对于系统的控制和调试

在一个SOC系统中,通常会有CPU,各种总线,以及各种各样的外设,接口等模块,以及运行在CPU上的软件系统(裸跑或者带操作系统)。这样的系统,通常调试起来都会比较费时费力,不论是对硬...

2017-11-17 6330

在Zynq平台运行SmallRTOS实时操作系统详细步骤

SmallRTOS是一个源代码开放的、易于移植的、面向深度嵌入式应用的微内核实时操作系统,主要应用领域为工业控制,智能传感器开发,智能终端等。...

2017-11-17 6706

基于图像增强的去雾快速算法的FPGA实现

本文提出了一种使用亮度映射的图像去雾快速算法。此算法通过调整室外多雾场景图像的对比度,提高了雾中物体的辨识度。算法的复杂度低、处理延迟小,实时性高,利于FPGA的实现。实现时...

2017-11-17 5930

基于LVDS的超高速ADC数据接收设计

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解...

2017-11-17 8566

无线系统基于SDR快速原型制作平台的设计步骤

无线系统的概念与设计实现之间存在巨大的差异。要缩小这种差异通常都要涉及到几组来自各领域的工程师团队(比如RF、SW、DSP、HDL和嵌入式Linux®),并且很多情况下项目在开发的早期阶段便...

2017-11-21 7315

ZYNQ 7系列FSBL的启动过程与配置方法

ZYNQ 7系列所有可编程器件均可以在安全模式下通过静态存储器配置或者在非安全模式下通过JTAG或者静态存储器配置。 (1)JTAG模式主要用于开发和调试 (2)NAND、并行NOR、串行NOR、SD卡闪存均可...

2017-11-17 27515

基于SRIO的FPGA间数据交互系统设计与应用

基于时分长期演进(timedivision- longtermevolution,TD-LTE)射频一致性测试系统中数据交互的分析研究,为了很好地满足现场可编程门阵列(fieldprogrammablegatearray,FPGA)间的大容量数据交互,设计了...

2017-11-17 5160

FPGA中RocketIO GTP收发器的高速串行传输实现方案

提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收发器设计的一个高速串行传输实现方案,详细阐述了硬件设计要点和软件实现概要,系统实测表明,该方案能在某信号处理系统两个板卡之间稳定...

2017-11-21 9123

V5 FPGA配置回读

通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA,被配置的FPGA以下简称DUT,产生配置时序的FPGA简称配置FPGA。首先硬件上应将M[2:0]接成110,即Slave SelectMAP模式,该模式下总线宽度分...

2017-11-17 10694

networkx高效开发SDN应用路由算法

为保证网络连通,控制器需应用相应的图论算法,计算出转发路径,完成数据转发。在开发SDN应用时,为完成基础的路径计算,时常需要开发者独立编写网络算法,不仅麻烦,性能和代码可复用...

2017-11-17 1834

基于Zynq的图像视频处理、显示平台

视频通过HDMI接口进来,然后经Video Input模块做格式变换,送入VDMA,该VDMA的作用是把数据送入在DDR3中所开辟的帧存中去。另一种是通过摄像头等设备获取视频源,经PS/PL将数据送入DDR3。就我目前...

2017-11-17 8236

简析Zynq芯片中PS和PL之间的9个双向读写的通信端口

Zynq芯片中,PS(ProcessorSystem)和PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是: M_GP0 M_GP1 S_GP0 S_GP1 S_AXI_HP0-3 S_AXI_ACP 这些端口的特性和适合的使用场景都不太一样,其...

2017-11-17 13167

低成本的采用FPGA实现SDH设备时钟芯片技术

介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实...

2017-11-21 2671

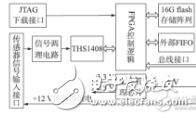

基于FPGA的超声数据采集装置的设计与实现

为了实现对某航天器在地面及飞行过程中的超声数据进行高精度、高速采集的功能,根据测量系统的技术要求,设计数据采集装置的硬件电路和时序控制逻辑。为了满足恶劣的环境测试要求,设计采...

2017-11-17 4144

基于MicroBlaze处理器的BPIFlash操作

本文主要介绍MicroBlaze在 FPGA中的应用,并结合实际工程介绍如何设计MicroBlaze微处理器与BPI Flash接口以及如何提高BPI Flash的烧写速度,同时也简单介绍利用MicroBlaze微控制器实现FPGA的动态可重构。...

2017-11-17 5891

JESD204B SystemC module 设计简介(一)

本设计致力于用SystemC语言建立JESD024B的协议标准模型,描述JESD204B的所有行为,并且能够保证用户可以通过该JESD204B的SystemC库,进行JESD204B行为的仿真和RTL代码的编写。设计以最新的版本JESD204...

2017-11-17 3539

SDAccel 开发环境运用

赛灵思 FPGA 器件主要由可编程逻辑架构组成,能让应用设计人员利用空间和时间并行性,最大化算法性能或大型应用中关键内核的性能。位于这种架构核心的是由基于查找表的逻辑元、分布式存...

2017-11-17 1622

Zynq SoC的特性及其设计实现

赛灵思 Zynq®-7000 All Programmable SoC 系列代表了嵌入式设计的新局面,为嵌入式系统工程设计群体带来前所未有的高性能和灵活性。这些产品在单个器件上集成了特性丰富的双核 ARM® Cortex-A9 MPCor...

2017-11-17 3585

运行Linux的ZedBoard设计实例

FPGA 和软件工程师要分别开发各自的功能,再根据集成测试计划进行组成和测试。这种方法持续运用了多年,但赛灵思 Zynq®-7000 All Programmable SoC 以及即将推出的赛灵思 Zynq UltraScale+TM MP-SoC 等功能...

2017-11-17 2752

用TI Designs加快你的FPGA电源设计

如果处理器和现场可编程门阵列FPGA全部由同样的电压供电运行,并且不需要排序和控制等特殊功能的话,会不会变的很简单呢?不幸的是,大多数处理器和FPGA需要不同的电源电压,启动/关断序...

2017-11-17 1489

包络跟踪基础的原理与测试方案

以前手机可以待机好几天都不需要充电。现在尽管手机电池技术不断革新,然而一些新的需求,例如更多内部无线电例如更多内部射频传输、更大更高分辨率的屏幕,使得电池电量比以往任何时...

2017-11-17 6704

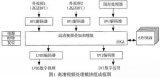

机载高清视频处理模块的软硬件设计

现代飞机中各种信息传感器的使用越来越广泛,座舱显示系统需要处理的数据也越来越多。为了使飞行员能够认读更多更清晰地视频信息,研究了机载高清视频处理模块的硬件设计和逻辑软件算...

2017-11-17 1215

数字下变频中抽取滤波器的设计及FPGA实现

针对软件无线电接收机数字下变频中高速数字信号的降采样需求,利用半带滤波器及级联积分梳状滤波器,设计了一种半带滤波器前置的多级抽取滤波器架构。通过Simulink搭建系统模型验证之后...

2017-11-17 6523

AXI4Stream总线的FPGA视频系统的开发研究

基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司提出,该协议专门针...

2017-11-17 5375

多普勒相位程序设计与实现

多普勒相位作为被测目标信息获取的重要来源,其计算精度成为基于FPGA实现合成孔径雷达实时回波模拟技术的关键要素。本文针对多普勒相位计算过程中存在的数值开方运算以及FPGA中专用开方...

2017-11-17 2521

一种基于FPGA硬件求解函数的简化方法

本文研究了一种运用FPGA进行数据处理的方法,包括:提取输入数据的高log2M个比特位的数据,作为高有效位,根据预先设置的目标函数的计算表格,查找所述高有效位对应的目标函数值y(n)以及...

2017-11-17 2917

基于FPGA的图像采集与存储系统设计

设计了一种针对具有大数据量特点图像数据采集、存储及长线回读的测控系统。在控制信号的作用下,此测控系统将CMOS传感器采集的大容量数据存储到Flash芯片中。存储完成后,通过LVDS总线,...

2017-11-17 3774

基于FPGA水下激光距离选通成像处理

水下激光距离选通成像中要对水下距离选通图像进行增强处理。水下图像通常具有噪声大、对比度差、照度不均匀的特点。通过分析水下图像的成像特点,针对引起图像降质的因素进行增强算法...

2017-11-17 4538

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |