FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。LabVIEW的RIO与I/O对比

NI可重配置I/O(RIO)产品可在灵活的开发平台上实现高精度测量,适用于需要高速闭环控制的系统级应用。这些应用有时需要比核心系统可提供的更多的通道数或分布更广的架构。而扩展I/O系统可...

2017-11-18 6331

数据流编程以及LabVIEW多核编程

因为NI LabVIEW是数据流编程语言,开发者们可以编写并行的应用程序,这些应用程序可以直接映射到并行的硬件(如多核心处理器和FPGA等)上以获得最优异的性能。这篇白皮书讨论了什么是数据...

2017-11-18 2138

FPGA通用接口JESD204转换器接口标准详解

随着转换器分辨率和速度的提高,对于效率更高的接口的需求也随之增长。一种新型转换器接口——JESD204——诞生于几年前,其作为转换器接口经过几次版本更新后越来越受瞩目,效率也更高...

2017-11-18 4415

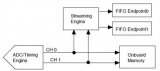

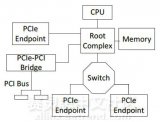

NI点对点数据流技术在FPGA模块的实例

NI点对点数据流(P2P)技术使用PCI Express接口在多个设备之间直接,点对点传输,而不必通过主处理器或存储器。这可使同一个系统中的设备共享信息而不必占用其它的系统资源。以下设备可支持...

2017-11-18 6547

NI FlexRIO设备的FGPA模块和适配器模块分析

NI FlexRIO设备包括了可采用NI LabVIEW FPGA模块进行编程的现场可编程门阵列(FPGA)模块,以及能提供高性能模拟和数字I/O的适配器模块。适配器模块是可互换的,并可以在LabVIEW FPGA编程环境下定义...

2017-11-18 2202

从三方面来看NI可重复配置I/O(RIO)技术

NI可重复配置I/O(RIO)技术能够让您通过使用可重复配置的现场可编程门阵列(FPGA)芯片和NI LabVIEW图形化开发工具,实现自定义的测量硬件电路。RIO核心包括FPGA芯片和外围电路,它们能够让...

2017-11-18 2711

在FPGA里浮点数与定点数表示法原理展示

浮点数与定点数表示法是我们在计算机中常用的表示方法 所以必须要弄懂原理,特别是在FPGA里面,由于FPGA不能像在MCU一样直接用乘除法。 首先说一下简单的定点数,定点数是克服整数表示法...

2017-11-18 9303

NI嵌入式系统编程教程(FPGA与软件工具)

设计工程师通常使用C等编程语言来开发基于微处理器或微控制器架构的嵌入式系统。 C语言的普及催生了用于程序库、编译器和操作系统等工具的大型技术生态系统。现场可编程门阵列(FPGA)...

2017-11-18 14889

freertos使用指南与各类型函数详细说明

FreeRTOS 内核支持优先级调度算法,每个任务可根据重要程度的不同被赋予一定的优先级,下面说明了各类函数的具体应用,包括API函数从任务创建到联合程序部分的具体过程演练步骤。...

2017-11-18 9890

浅析FreeRTOS源代码的编程标准与命名约定

编程标准 (Coding Standard) FreeRTOS 源代码遵守 MISRA (Motor Industry Software Reliability Association) 规范。 与 MISRA 标准有出入的地方如下: • 两个 API 函数具有两个出口点。之所以这样是为了效率。 •...

2017-11-18 1706

使用NI FlexRIO时我们应当了解和注意的十大点

NI FlexRIO是NI公司的应用FPGA技术的最新产品族。它为LabVIEW FPGA提供了灵活的、可定制的I/O,以创建高性能、可重新配置的仪器。通过一个开放的、可定制的信号前端,可以满足一个测试系统或嵌...

2017-11-18 7063

关于JESD204B转换器与FPGA匹配的设计关键点

随着更多的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA供应商多年来一直支持千兆串行/解串(SERDES)收发器。然而在过去...

2017-11-18 1839

Vivado设计之Tcl定制化的实现流程

其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源...

2017-11-18 4128

LabVIEW FPGA为NI 9144 带来的分布式I/O实时部署

这篇文章讨论了使用分布式I/O进行实时部署系统的设计。美国国家仪器公司推出了NI 9144扩展机箱,用于确定性以太网中的NI CompactRIO和可编程自动化控制器(PAC)系统。该C系列模块的8槽机箱,...

2017-11-18 2823

浅析如何在项目浏览器窗口管理FPGA应用

本文将讲述如何通过项目浏览器窗口管理FPGA应用的组件,包括FPGA VI和主VI、FPGA终端、终端范围的选项(例如,FPGA I/O、FPGA FIFO和FPGA终端时钟)。下列示意图显示了由FPGA终端、一个FPGA时基时钟...

2017-11-18 711

适用于需要处理大型数据集的NI LabVIEW多核分析和稀疏矩阵工具包介绍

NI LabVIEW多核分析和稀疏矩阵工具包提供了高性能的LabVIEW多线程分析库,是在线或离线的大数据集处理应用的理想工具。实际上,许多现实世界的问题可以表示为大型线性代数计算,而该工具包...

2017-11-18 3144

FreeRTOS 中的链表和链表元素的定义

FreeRTOS 内核中采用双向循环链表来进行任务调度,对任务总数没有限制,同一优先级的任务数也没有限制。相对于uC/OS-II 来说是一个大的优点。不过,有利必有弊。采用双向链表后代码相对来说...

2017-11-18 2622

关于FreeRTOS配置项操作解读

FreeRTOS 是高度可配置的。所有的可配置项都在FreeRTOSConfig.h 文件中。每一个Demo 程序中都包含了一个配置好的FreeRTOSConfig.h 文件,可以以Demo程序中的FreeRTOSConfig.h 文件作为模板,在其基础上加以修...

2017-11-18 2653

如何使用PICOBLAZE?PICOBLAZE开发流程介绍

PicoBlaze™是一款结构紧凑的8位软核微控制器,FPGA工程师可在其所选的赛灵思FPGA中对其进行实例化。一旦实现,该处理器完全包含到仅使用逻辑Slice和Block RAM的FPGA架构中;无需外部易失性和非易...

2017-11-18 4250

如何优化赛灵思内核以便在CPRI远程无线电头端设计中使用Vivado IPI

新型基于FPGA的设计使用IP核的数量和种类日趋繁多。Vivado®设计套件中的IP集成器 (IPI)工具和赛灵思通信IP让设计人员能够更加轻松快速地将IP模块连接在一起。 为了更好地阐明IPI方法的强大之处...

2017-11-18 2581

FPGA框架与FPGA设计规则

鉴于FPGA在如此多应用中的重要地位,采取正式且注重方法的开发流程来处理FPGA设计比以往更加重要。该流程旨在避免开发周期后期因发现设计缺陷而不得不进行费时费钱的设计修改,而且该缺...

2017-11-18 2164

使用Virtex-6器件和免费WebPACK工具实现实时四倍上采样的方法

许多信号处理应用都需要进行上采样。从概念上讲,对数据向量进行M倍上采样的最简单方法是用实际频率分量数的(M-1)倍个零填充数据向量的离散傅里叶变换(DFT)[1],然后将零填充向量...

2017-11-18 1870

利用FPGA对大规模MIMO信道进行特性描述与实时分析

由24个FPGA、96个天线以及一个802.11定制模块构建的系统可对多用户MIMO传播环境进行实时分析。 多用户MIMO(MUMIMO)是一种无线通信技术,采用基础架构节点(例如基站和接入点)上的多个天线为...

2017-11-21 2679

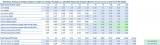

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议分析

针对较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试平台;然后设计并分别实现了三种协议的高速数据通信,...

2017-11-18 13404

基于动态重构技术的FPGA电路容错性能评估系统

(1) 与加入冗余保护的RS编码器相比,未加冗余保护的RS编码器可靠性较差,因此三模冗余可有效提高编码器的可靠性; (2) 分布式三模冗余与全局三模冗余的保护效果较好,全局三模冗余的可...

2017-11-17 1653

控制算法与工业网络的结合FPGA SoC加速马达开发

工业设计人员可望借助快速建立原形技术和模块基础设计,将马达控制算法移至FPGA SoC环境中,藉此开发出以FPGA SoC为核心的马达驱动系统,从而大幅减少与设计复杂性,同时降低系统成本并提...

2017-11-17 1300

Cadence OrCAD FPGA System Planner为在PCB板的FPGA设计提供支持

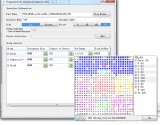

Cadence OrCADFPGA System Planner为FPGA和PCB之间的协同设计提供了一种全面的、可扩展的解决方案,它能使用户创建一个正确的、最优的引脚分配。FPGA的引脚分配是根据用户的指定、基于接口的连接(...

2017-11-17 6831

PicoBlaze处理器软核中的KCPSM6应用技巧与案例

PicoBlaze是8位微处理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA与CoolRunner-II系列以上的CPLD器件设计中以IP核的方式提供,使用是免费的 。常见的版本有KCPSM3和KCPSM6。其中KCPSM支持7系列的Xilin...

2017-11-17 4370

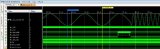

dds通过增加幅度控制等配合依托MCU的交互界面和功放实现所需要的波形

dds通过增加幅度控制、正交调制、载波相乘、触发控制等配合依托MCU的交互界面和功放,就变成了一个复杂的信号源了。...

2017-11-17 2207

分类算法的概述以及其优缺点

分类是一种重要的数据挖掘技术。分类的目的是根据数据集的特点构造一个分类函数或分类模型(也常常称作分类器),该模型能把未知类别的样本映射到给定类别中的某一个。为了提高分类的...

2017-11-17 11097

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |