FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。基于声纳探测技术的水下三维场景实时成像系统

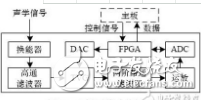

针对目前水下三维声纳实时成像系统前端信号通道多、波束形成计算量大的问题,提出一种基于现场可编程门阵列(FPGA)的水下三维场景实时成像系统。采用FPGA阵列控制多路信号同步采样,优化...

2017-11-18 16746

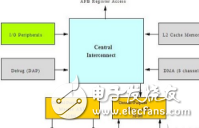

MicroBlaze如何与ZynqSoC和平共存

赛灵思Zynq-7000All Programmable SoC已具有很强的板载处理能力。但是Zynq应用处理单元(APU)中强大的双Cortex-A9处理器和相关外设的存在并不妨碍您在同一封装中添加一个或多个MicroBlaze处理器,只要能让...

2017-11-18 7114

SMC主机接口模块设计导入Xilinx环境

SMC主机接口模块可轻松将通过Synphony模型编译器创建的设计集成在赛灵思嵌入式平台中。 Synphony模型编译器(SMC)是一款Synphony提供的、基于模型的工具,其可综合在Simulink®及MATLAB®中创建的设...

2017-11-18 4966

转换器JESD204B与LVDS的综合比较

根据最新JESD204B标准构建的转换器非常适合新型高速FPGA。在采用这些器件进行设计时,应考虑I/O注意事项。随着数据转换器架构和FPGA不断采用更高级更小型化几何体,系统设计人员面临着新的...

2017-11-18 2729

教你如何为Xilinx设计创建创建自定义XBD文件

创建自定义赛灵思板级描述(XBD)文件不仅有助于节省时间,而且还能确保设计项目按计划推进。为您设计的任意开发板创建一个XBD文件并非难事。 FPGA厂商推出了许多出色的评估板和专用开发...

2017-11-18 3220

如何安装实时操作系统RTOS

要想最大限度地发挥Zynq All Programmable SoC的优势,您需要一款操作系统。本文将介绍如何安装实时操作系统—这里特指μC/OS-III。要想从最大限度地发挥赛灵思Zynq®-7000All Programmable SoC处理系统的地...

2017-11-18 6802

验证设计和创建可实现的设计

验证RTL模块或FPGA是否满足要求可能颇具挑战。但有些方法可用来优化验证流程,以确保验证成功。验证FPGA或RTL模块可能是一个非常耗时的过程,因为工程师要极力确保设计能够按照规范要求并...

2017-11-18 1010

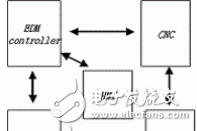

基于LabVIEW和CompactRIO开发的EDM过程控制器

FPGA硬件平台均采用统一图形语言LabVIEW编程,仅用两个多月的时间就完成了整个系统的开发,功能强大。挑战:快速开发一种分布式的电火花放电加工EDM(Electrical Discharge Machining)过程控制器,它将...

2017-11-18 1980

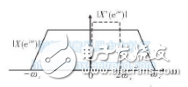

基于FPGA的多相滤波结构的信道化设计

随着现代电子战中电磁环境的日益复杂,军用接收机需具备同时处理多个信道信号的能力,即具备全概率截获能力。信道化接收机可将一个复杂信号分成多个信道,从而方便后续处理。文中利用...

2017-11-18 6443

基于数字滤波平方的定时同步算法的研究

文中对适用于高速突发通信的基于数字滤波平方的定时同步算法进行了研究。通过对在高速数据传输通信中,该定时同步环路的定时误差估计模块进行并行结构实现,大幅降低了系统对于时钟的...

2017-11-18 7145

基于FPGA和处理器的集成式电源管理方案

该解决方案在单芯片IC上集成多个开关稳压器、LDO和监控/看门狗定时器,由于机器视觉系统的尺寸不断变小,而这些系统的处理能力持续飞速增长,电源管理正进一步成为新机器视觉系统的重要...

2017-11-18 1678

基于DM648的图像处理逻辑设计与实现

介绍了一种基于DM648和FPGA构架的图像处理方案,阐述了图像处理模块的组成原理和结构,并对模块内部电路设计和FPGA内部图像处理逻辑进行了重点介绍。木文设计的图像处理模块能够支持对高...

2017-11-18 2952

基于FPGA和PWM的多路信号发生器设计

基于运放的信号发生器精度低且稳定性和可调节性差,而基于DDS的信号发生器则成本高、电路复杂。为此提出了基于FPGA+PWM的多路信号发生器设计方法。该方法硬件上无需DAC与多路模拟开关,由...

2017-11-18 7586

基于FPGA多波束成像的声纳系统设计

给出了一种基于FPGA的多波束成像声纳整机的硬件电路设计方案,介绍了该方案中各分系统的具体电路实现,以Xilinx公司的FPGA芯片作为核心器件,根据干端PC下发的控制指令实现对180个基元的发...

2017-11-18 4905

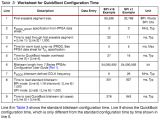

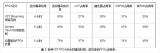

QuickBoot基础知识与在FPGA逻辑远程更新的应用

对于成熟的电子产品,高效稳定的工作是非常重要的一项指标。而一款刚推向市场的产品则需要研发人员或者技术维护人员进行必要的维护或者更新,以求达到更稳定的效果。对于FPGA的逻辑更...

2017-11-18 9539

基于ZYNQ SOC的电机控制及实例分析

工业设计人员可以利用快速原型与基于模型的设计将电机控制算法移至Zynq SoC环境。 自20世纪90年代以来,电机驱动开发人员一直采用多芯片架构实施电机控制与处理需求。 在这种架构中,离散...

2017-11-18 12143

NI VST FPGA软件编程使用步骤与实例教程

本文介绍 NI VST FPGA软件包含多层代码,提供了从底层控制到高层抽取的一切,拥有RF信号分析仪和RF信号发生器的功能。底层组件实现了具体硬件的标准功能,包括信号校准、前端控制,以及基...

2017-11-18 10476

NI LabVIEW Real - Time和Microsoft Windows Embedded Standard7三大问题突显性能对比

为了满足您的部署需要,NI提供了两种嵌入式操作系统:NI LabVIEW Real - Time和Microsoft Windows Embedded Standard7(WES7)。每种操作系统对于不同的任务和操作具有不同的优势。 LabVIEW Real-Time保证了关键...

2017-11-18 4837

FPGA(现场可编程门阵列)的基础知识及其工作原理

高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA)。无论你使用图形化设计程序,ANSI C语言还是VHDL语言,如此复杂的合成工艺会不禁让人去想FPGA真实的运...

2017-11-18 18429

仪器驱动的FPGA扩展介绍与实例应用

仪器驱动的FPGA扩展弥合了开放式FPGA非并行灵活性和标准仪器驱动兼容性之间的代沟。通过仪器驱动的FPGA扩展,您将能够以非常简便的方法同时实现这两个方面,使更多测试工程师可以利用FP...

2017-11-18 1419

基于FPCA可编程逻辑技术的时钟恢复技术与系统同步详解及应用

随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件...

2017-11-18 2065

Xilinx 7系列设备和NI cRIO-9068控制器创新详解

Robert Bielby—Xilinx公司策略市场和业务规划高级总监 新的NI cRIO-9068可重配置机箱和NI PXIe-7975R NI FlexRIO FPGA模块采用的是Xilinx 7系列完全可编程FPGA和SoC设备。如果要深入理解NI新的可重配置I/ O(RIO...

2017-11-18 3281

基于Zynq-7000 AP SoC实现高效马达控制设计实例

碳足迹、绿色能源和气候变化屡现新闻头条,引人瞩目。为保证我们的后代有一个洁净的生活环境,我们必须立即行动起来。为此,发达国家的政府以税费的方式来降低碳排放和能源使用。由于...

2017-11-18 4741

FPGA VI或程序生成规范的引用的基础教程

主VI可用于与运行在FPGA终端上的FPGA VI或位文件通信。主VI可运行在计算机上或RT终端上。每个主VI必须打开运行在FPGA终端上的FPGA VI、程序生成规范或位文件的引用。可打开与主VI同属一个LabVIE...

2017-11-18 3249

FPGA中主控VI等待和确认信号终端与等待和确认多个中断步骤教程

某些FPGA终端允许通过FPGA VI生成中断以通知主控VI事件。例如,数据已准备好、产生错误或任务完成。如要判定终端是否支持中断,请访问FPGA终端属性对话框的常规页面的终端信息部分。 等待和...

2017-11-18 2412

采用流水线进行FPGA VI吞吐量优化设计

流水线是一种可用于增强FPGA VI吞吐量的技术。在流水线设计中,用户可利用FPGA的并行处理功能提高顺序代码的有效性。如要实现流水线,必须将代码拆分为不同的级并连线每级的输入和输出端...

2017-11-18 3934

底层FPGA实现的简要概述

每个FPGA芯片(FPGA)是由有限个带有可编程连接预定义资源组成。这些互连资源通过LabVIEW FPGA模块实现用户设计的数字电路。用户创建FPGA VI时设计一个电路示意图,以说明FPGA逻辑块的连接方式。编...

2017-11-18 1144

集成Xilinx内核生成器IP至FPGA VI详细步骤

LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI的程序框图。 2、右键单击程序框图显示函...

2017-11-18 2498

FPGA VI中不同的Xilinx内核生成器IP设计实现与子模板说明

所属选板:FPGA模块VI和函数 必需:FPGA模块。本主题的内容可能与您所安装的LabVIEW选板不匹配,LabVIEW选板上显示的对象取决于操作系统、已获得许可证的产品以及终端。 使用Xilinx内核生成器...

2017-11-18 1831

基于FPGA的振动信号采集处理系统设计并实际验证

在振动信号采集和处理系统设计中,信号的处理时间与可靠性决定着系统应用的可行性。本文设计了一种基于FPGA的振动信号采集处理系统,该系统通过振动信号采集电路、抗混叠滤波电路、A...

2017-11-18 4848

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |