FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。在FPGA平台下实现基于平方倍频法的BPSK调制信号载频估计单元设计

根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。利用ModelSim仿真环境对载频估计功能进行仿真,验证了平方倍频法对BPSK信号进行载波信号估...

2017-11-18 4552

基于FPGA的LVDS过采样技术研究并用Xilinx评估板进行验证

针对LVDS接口,研究并实现了一种基于FPGA的LVDS过采样技术,重点对LVDS过采样技术中系统组成、ISERDESE2、时钟采样、数据恢复单元、时钟同步状态机等关键技术进行了描述,并基于Xilinx FPGA进行了...

2017-11-18 8303

Zynq-7000系列特征概述

相比较经典的FPGA,Zynq-7000系列最大的特点是将处理系统PS和可编程资源PL分离开来,固化了PS系统的存在,实现了真正意义上的SOC(System On Chip)。 1. Zynq-7000系列特征概述 Zynq-7000系列是全可编程...

2017-11-18 20215

基于FPGA的抖动及消抖的方法

抖动的产生,通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及...

2017-11-18 10972

NI系统级模块(SOM)采用可重配置的FPGA技术

基于Zynq SoC,NI SOM经过广泛的测试与验证,并配有完整的软件协议栈。 嵌入式设计团队肩负着处理众多棘手问题的重担。他们需要跟上最新技术并提供众多新功能以保持竞争优势;同时,对于每...

2017-11-18 2743

基于FPGA时序优化设计

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还...

2017-11-18 3877

xilinx Vivado HLS工作方式的优势与案例

不同层面的协议处理常见于各种新型通信系统,因为任何信息交流都需要使用某种通信协议。通信协议一般包含数据包。数据包由发送方创建,由接收方重新组合,这些操作都要遵循协议规范...

2017-11-18 10780

软件可靠性设计研究及应用

无论您的终端应用是什么,可靠性都将是设计的主要考虑因素之一。实现可靠性的方法多种多样。在考虑设计可靠性时,大部分工程师都将注意力集中在一个综合性度量标准:平均故障间隔时间...

2017-11-18 2684

在Vivado下利用Tcl实现IP的高效管理

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动添加到当前工程中;另一种是利用Manage IP,创建独立的IP工程,缺省情况...

2017-11-18 6153

存储器领域的现状

赛灵思有90%的客户在使用DDR存储器。DDR4是倍受青睐的DDR存储器系列的最后一代。众多竞争者们正在虎视眈眈,意图抢占更大的DDR4市场份额。 存储器领域正在发生翻天覆地的变化,这一变化的根...

2017-11-18 2570

Virtex UltraScale器件的优点

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex UltraScale 系列具有前所未有的高性能、系统集成度和带宽,适用于有线通信、测试测量、航空航天...

2017-11-18 2369

宇宙微波背景辐射中发现引力波

一个南极多学科科学家小组最近窥到了宇宙大爆炸的余晖。3月17日该小组宣布BICEP2试验在宇宙微波背景辐射(CMB)的B模偏振中找到了引力波的第一个证据。目前科学家们在寻找另一个印迹:C...

2017-11-18 1947

JESD204B接口及协议状态过程

在使用我们的最新模数转换器(ADC)和数模转换器(DAC)设计系统时,我已知道了很多有关 JESD204B接口标准的信息,这些器件使用该协议与FPGA 通信。...

2017-11-18 3428

XDC路径的鉴别、分析和约束方法

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC是...

2017-11-18 7014

XDC的时钟约束及优势

Xilinx©的新一代设计套件 Vivado 中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家告诉你,其实用好 XDC...

2017-11-18 4119

Tcl在Vivado中的基础应用

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握...

2017-11-18 5381

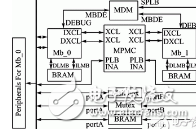

基于双MicroBlaze软核处理器的SOPC系统

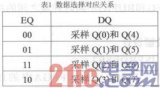

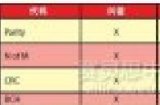

设计了一款基于双MicroBlaze软核处理器、面向嵌入式领域的SOPC系统,在信息处理繁忙的情况下,实现两软核处理器之间的同步、通信和中断功能,提高信息吞吐率和系统灵活性,降低设备尺寸。...

2017-11-18 4465

基于FPGA的图形生成与视频处理系统的设计与实现

本文对基于FPGA的机载视频图形显示系统架构进行设计和优化。从实时性、BRAM资源占用和DDR3吞吐量三方面进行分析,改进帧速率提升算法来提高实时性;改进视频旋转算法来降低BRAM资源占用;...

2017-11-18 3332

基于FPGA+DSP的海德汉编码器结构及设计

在现代工业控制系统中,对电机的控制是其重要组成部分。编码器作为电机角位移的检测装置,为系统提供重要反馈信号。本文介绍了一个适合嵌入式系统的基于DSP和FPGA的海德汉光电编码器信...

2017-11-18 4522

使用LabVIEW进行GPU计算

具有并行处理架构的平台,例如FPGA和GPU,在快速分析大型数据集方面得到了广泛应用。这两项技术可以减轻运算密集型算法对CPU造成的负担,在高度并行的平台上进行处理。FPGA灵活性高、处理...

2017-11-18 5534

基于CompactRIO的高级可编程自动控制器

全新NI cRIO-907x CompactRIO集成系统是一种高级可编程自动控制器(PAC),它在单个机箱中集成了工业实时处理器及一块可配置FPGA,降低了用于高容量机器控制、监控等应用的CompactRIO系统的成本。...

2017-11-18 3034

借助智能DAQ获得高级数据采集技术

多功能智能DAQ设备配有自定义式板载处理功能,最大限度地为系统定时及触发提供灵活性能。 与控制设备功能的固定ASIC不同,智能DAQ采用基于FPGA的系统定时控制器,令所有模拟和数字I/O能够根...

2017-11-18 4723

在Vivado下利用Tcl脚本对综合后的网表进行编辑过程

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合...

2017-11-18 8401

基于FPGA的Vivado功耗估计和优化

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一...

2017-11-18 7915

基于FPGA的机载显示系统架构

本文设计一种基于FPGA的机载显示系统架构,能够实现2D图形绘制,构成各种飞行参数画面,同时叠加外景视频图像。BRAM资源占用方面,视频旋转算法需要279个36Kb的BRAM;DDR3吞吐量方面,系统吞...

2017-11-18 3031

使用JESD204B同步多个ADC

许多通信、仪器仪表和信号采集系统需要通过多个模数转换器(ADC)对多个模拟输入信号进行同时采样。随后,经过采样得到的数据需被处理以实现各个通道的同步,然而他们各自有不同的时延...

2017-11-18 5310

构建JESD204B链路的步骤

JESD204B 协议中的三个状态对于在链路的 TX 和 RX 之间构建有效数据链路非常重要,它们是:代码组同步 (CGS)、初始信道对齐序列 (ILAS) 和用户数据。今天我将探讨在 TX 与 RX 之间必然会出现的信...

2017-11-18 13874

JESD204B标准及演进历程

在从事高速数据撷取设计时使用FPGA的人大概都听过新JEDEC标准「JESD204B」的名号。近期许多工程师均联络德州仪器,希望进一步了解 JESD204B 接口,包括与FPGA如何互动、JESD204B如何让他们的设计更...

2017-11-18 14941

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |