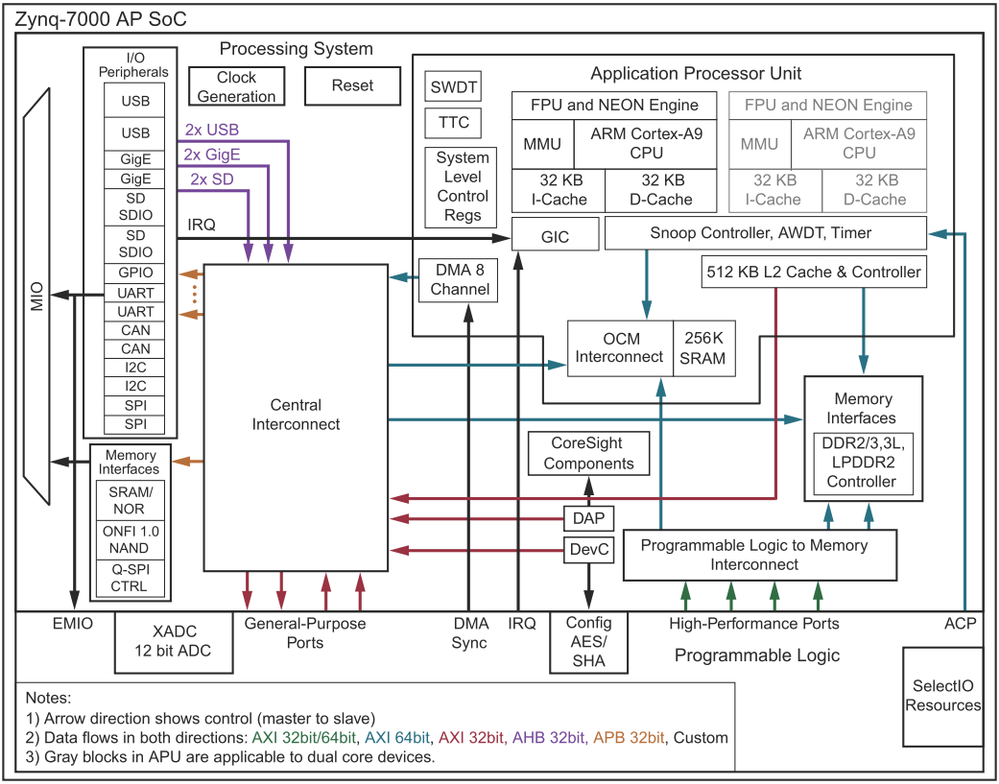

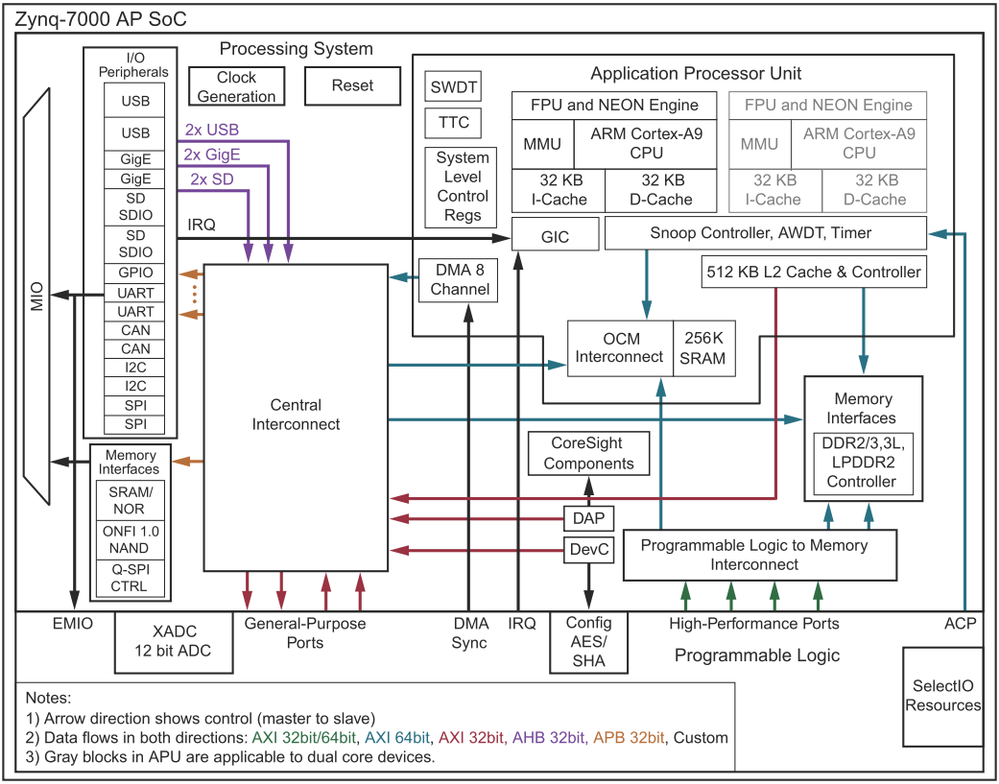

ZYNQ概述 ZYNQ内部包含PS和PL两部分,PS中包含以下4个主要功能模块: Application processor unit (APU) Memory interfaces I/O

2020-11-03 12:33:13 6201

6201

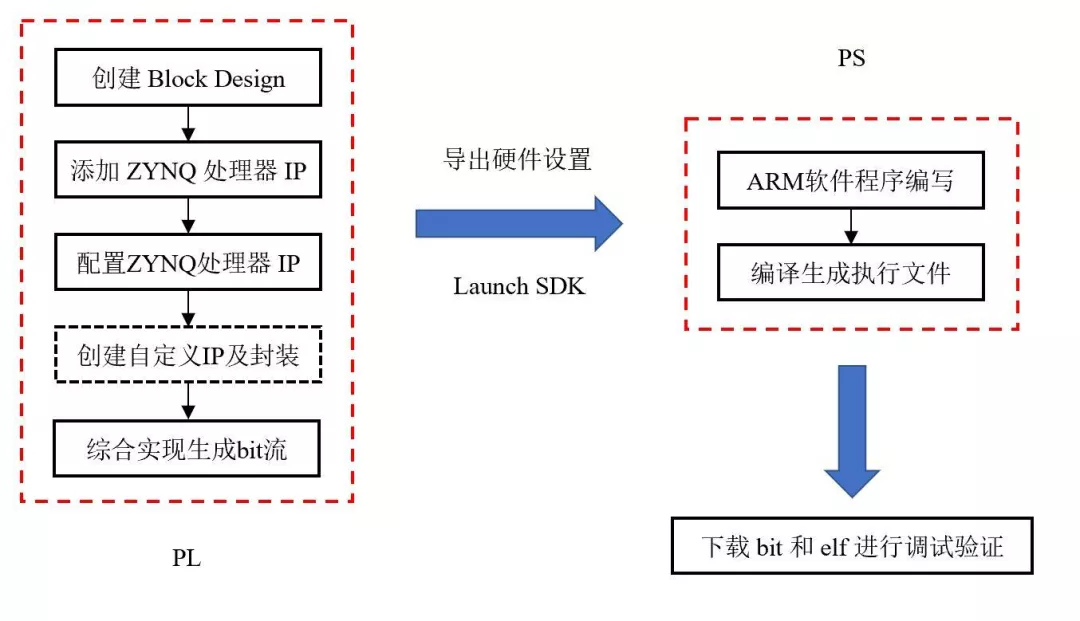

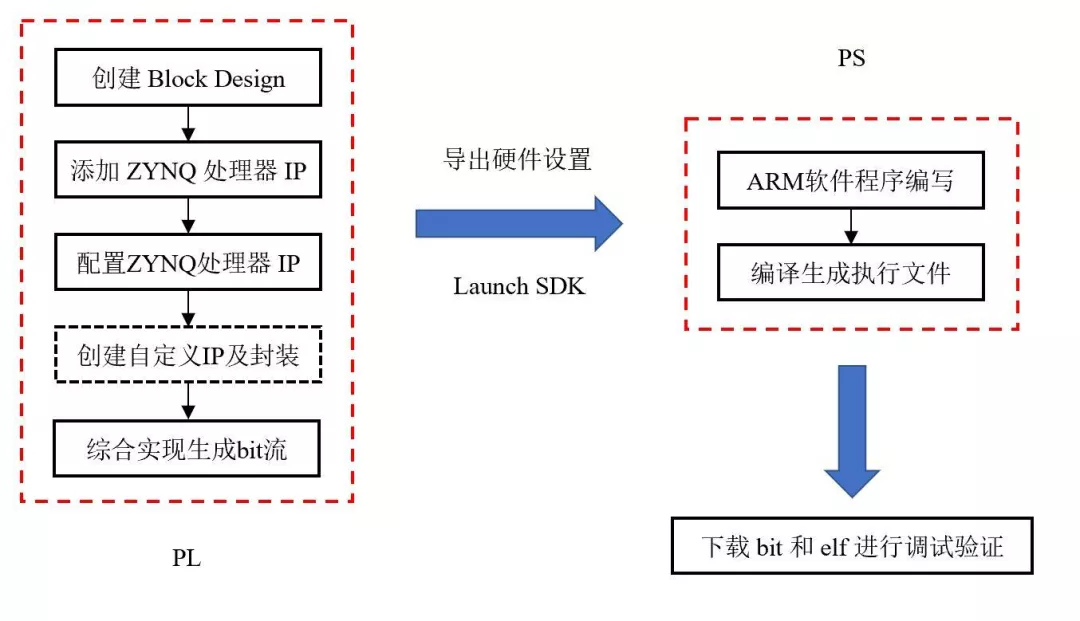

。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 9769

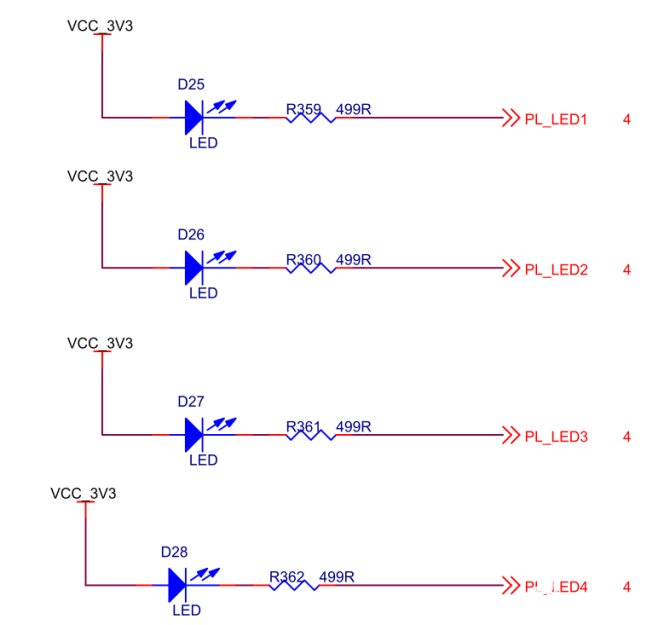

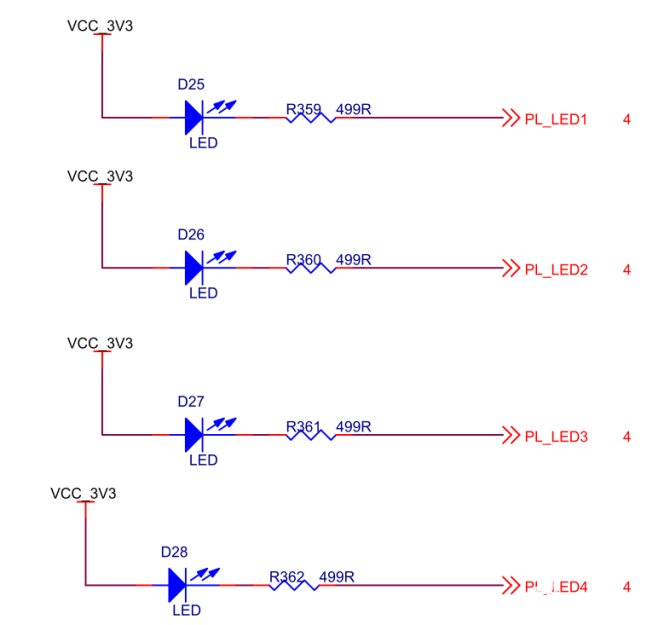

9769 对于ZYNQ来说PL(FPGA)开发是至关重要的,这也是ZYNQ比其他ARM的有优势的地方,可以定制化很多ARM端的外设,在定制ARM端的外设之前先让我们通过一个LED例程来熟悉PL(FPGA)的开发流程,熟悉Vivado软件的基本操作,这个开发流程和不带ARM的FPGA芯片完全一致。

2021-01-21 13:28:08 18886

18886

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 16464

16464

/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 19446

19446

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 3710

3710

上篇主要是分享了Vivado编译软件远程调试的方法。杰克使用Vivado软件进行远程连接,主要是用于固化程序以及FPGA(PL端)的异常排查。而本篇主要内容是对使用Vitis软件远程调试的方法进行总结和分享。

2023-05-25 14:36:58 4231

4231

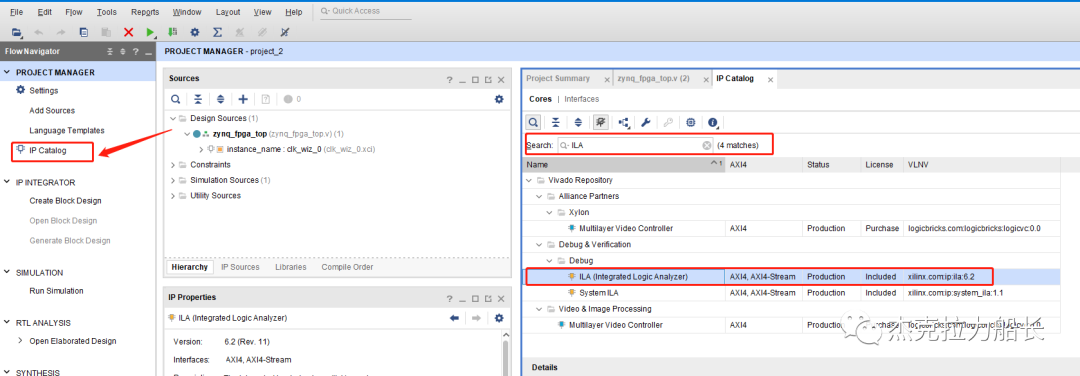

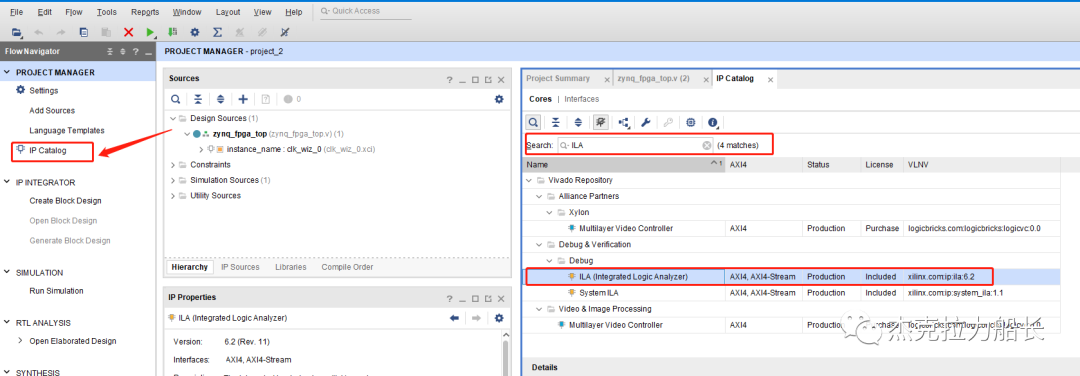

两大主流厂商的软件集成逻辑分析仪供使用,Altera的Quartus自带SignalTap、Xilinx的Vivado自带ILA逻辑调试工具。

2023-10-01 17:08:00 7441

7441

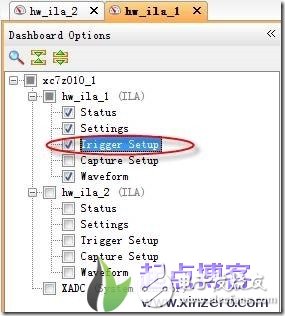

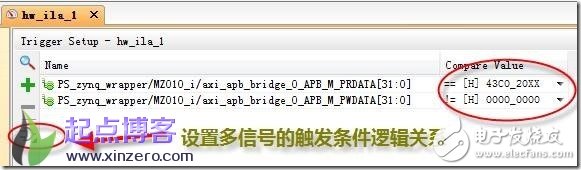

ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD Zynq 7000 SoC)之间可以进行Cross Trigger。这个功能在你需要在不同时钟域的两个ILA核心之间触发,或者在处理器和ILA核心之间执行硬件/软件跨触发时非常有用。

2023-11-30 10:17:59 2422

2422

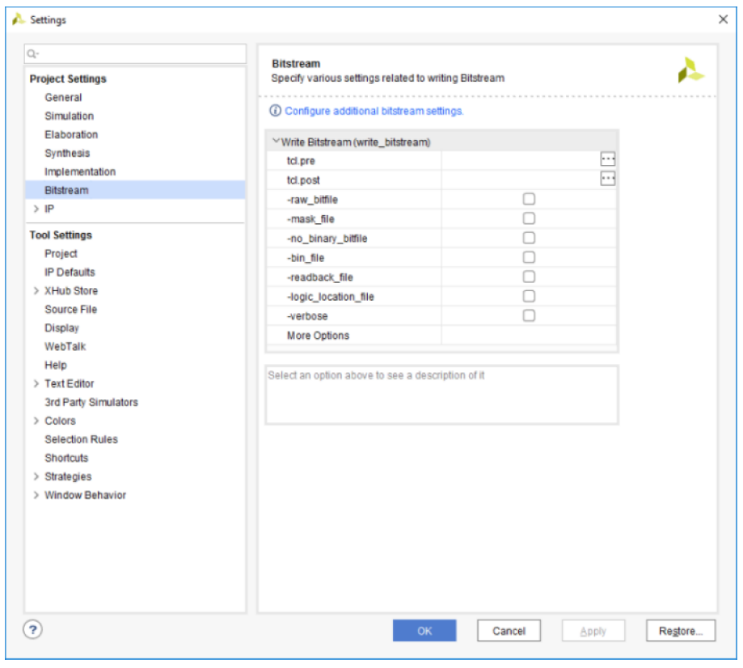

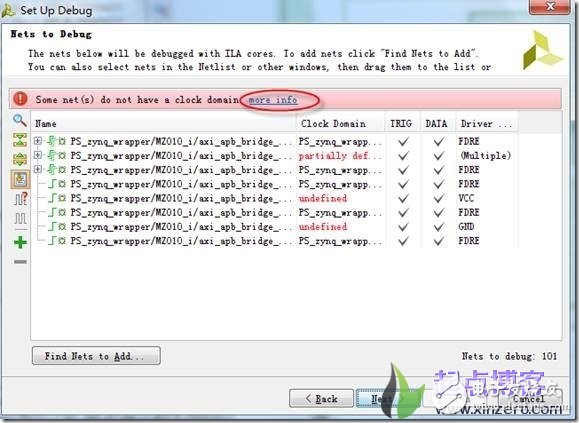

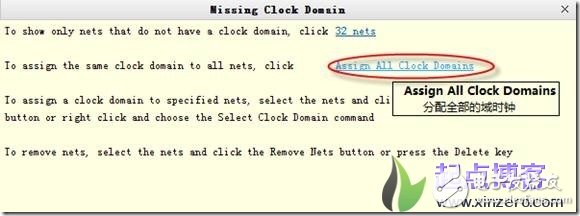

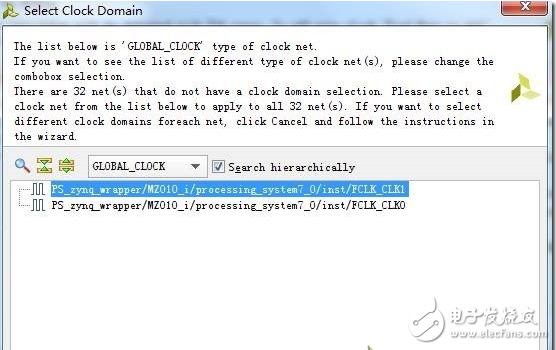

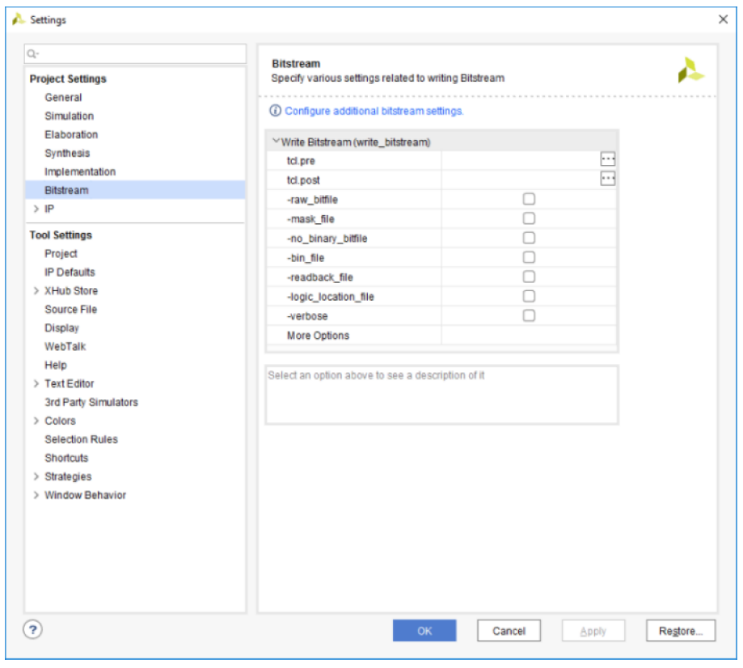

当我有一个ILA核心存在时,我的设计通常会失败,我在程序框图中标记了网络上的调试。我注意到当Vivado使用调试向导修改xdc文件时,存在这种约束set_property

2018-10-29 14:12:56

请问在Xilinx Vivado之中,没有PL的工程,能否直接开启SDK程序,并固化程序到ZYNQ的芯片之上

2021-03-29 17:22:00

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 06:49:13

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 07:05:36

。

实操演示

下面做一个从uart打印hello world的实验,只用PS,不用PL部分,程序从SD卡启动,跑在PS的内部RAM。

zynq 7000的PS虽然也是CPU,但是开发方法不像普通

2024-05-03 19:28:17

今天给大侠带来简谈Xilinx Zynq-7000嵌入式系统设计与实现,话不多说,上货。Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA的并行执行

2021-11-09 06:43:27

CPUCPU为Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平台升级能力强,以下为Xilinx Zynq-7000特性参数:电源接口和开关采用12V3A

2021-12-30 07:55:37

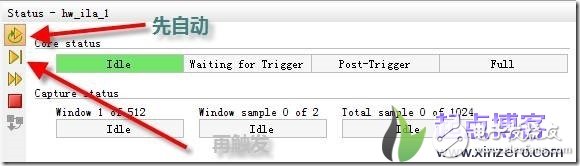

base_cameralink_loop.ltx调试文件,如下图下载界面所示: 1.1.5.3 运行结果说明ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集Cameralink并行信号以及错误

2023-02-24 10:00:56

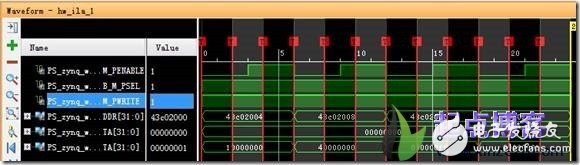

说明ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集GTX收发本地并行信号以及错误检测信号的时序波形。ILA抓取波形如下图所示: ILA抓取信号说明如下:ERR_COUNT[0:7]:接收数据

2023-02-20 17:27:57

(9-1)次FLOPs。所以近似来看1FLOPs ≈ 2MACs。ZYNQ PL****端算力指标参考Xilinx官方文档Zynq-7000 SoC Data Sheet: Overview (DS190

2022-12-15 21:19:38

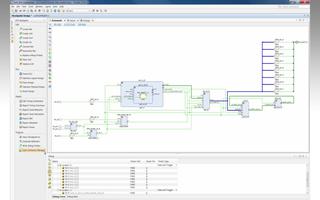

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机

2021-05-28 14:28:28

建立这部分请参考我上篇讲述搭建操作系统的文章二、VIVADO工程设置zynq核的搭建也请参照上篇文章,不过需要增加一些内容;双击zynq核,进入zynq的配置;选择PS-PL Configuration,选中General—>Enable Clock Resets—>FCLK_RESET

2021-12-17 06:42:06

使能信号,即DSP读使能,低电平有效。DSP端:为输出接口;ZYNQ PL端:为输入接口。1.1.3 例程使用1.1.3.1 加载运行ZYNQ程序1.1.3.1.1 打开Vivado工程打开Vivado

2023-03-08 16:46:37

据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印,如下图所示:1.1.3.3.2ZYNQ PL程序运行结果ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集EMIF16总线

2023-03-21 15:30:37

的ILA调试窗口,可以实时抓取采集SRIO本地总线信号时序波形。SRIO本地总线信号说明如下(详细定义请参考数据手册Xilinx文档pg007_srio_gen2.pdf):SRIO本地发送总线信号

2023-02-21 14:51:50

ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2022-02-17 07:37:36

运行ZYNQ程序1.1.3.1.1 打开Vivado工程打开Vivado示例工程: 工程打开后界面如下图所示: 1.1.3.1.2 下载ZYNQ PL程序下载bit流文件FPGA_DSP_GPIO.bit,如下

2023-06-16 16:02:47

程序运行结果ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集SRIO本地总线信号时序波形。SRIO本地总线信号说明如下(详细定义请参考数据手册Xilinx文档

2023-02-02 21:43:20

问题:与先前的关注相关,在为ZYNQ使用XIP时可以Iprogram PL吗?XIP链接:http://www.wiki.xilinx.com/Zynq-7000+AP+SoC+Boot+-+Booting+and+Running+Without+External+Memory+Tech+Tip

2020-03-19 10:33:09

在用Vivado实现某个工程时,功能仿真正确,时序满足要求,比特流也能生成,但是在ILA调试和下板子时,无法得到正确的结果信号,请问各位大神可能是什么问题?

2017-12-11 11:10:47

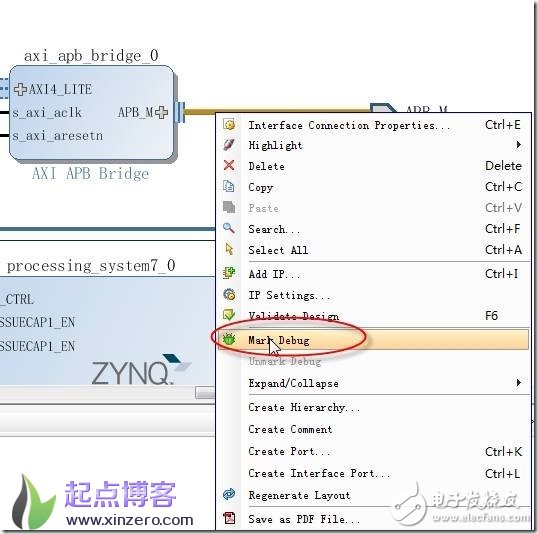

在使用vivadao在线调试功能时,对需要抓的信号MARK DEBUG,调用了ILA测试核,添加了时钟约束,但是总是显示no nets matched的warning,最后烧到片子里界面没有跳转到在线调试界面,无信号,显示没有添加ILA,问题出在哪里呢?求大神解答

2015-06-08 11:19:27

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的时钟方案是zynq PS FCLK_CLK0-->时钟向导IP输入(Primitive PLL)的输入。合成

2018-11-05 11:40:53

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

大家好,我在使用Arty(Artix 7 FPGA)进行调试时遇到了一些麻烦。背景:我使用ILA在Zybo(Zynq)和Nexys 4 DDR(也是Artix 7)上调试我的程序,一切正常。我

2020-08-26 15:20:18

前四期测评计划:

一、开箱报告,KV260通过网线共享PC网络

二、Zynq超强辅助-PYNQ配置,并使用XVC(Xilinx Virtual Cable)调试FPGA逻辑

三、硬件加速之—使用PL

2023-09-16 14:15:14

熟悉了一下Vivado的开发流程。Vivado的开发流程如下:由于首次使用ZYNQ系列的板子,所以还是不是很熟悉。这几天对ZYNQ做了一定的了解,其实ZYNQ里面总的来说分两大板块,PS+PL,PS

2015-05-23 15:08:25

到可编程逻辑单元部分(PL), ARM处理器的子系统也可以独立工作,这与以前的FPGA有本质区别,其是以处理器为中心的。 Zynq就是两大功能块,PS 部分和 PL部分,说白了,就是ARM的SOC部分

2021-01-07 17:11:26

关于Zynq的理论部分,文大部分截图摘抄自《zynqbook》ZYNQ架构双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样

2021-07-23 10:11:25

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM处理器和FPGA。ZYNQ与传统的嵌入式CPU相比,具有强大的并行处理能力。开发人员利用FPGA强大的并行处理能力,不仅

2021-01-15 17:09:15

大家好,我最近买了一个新的Zynq xc7z020板。我的另一块电路板与我目前的设计相得益彰。然而,当我尝试使用位文件和直接从Vivado的程序管理器中的.ltx文件直接编程PL时,我会收到以下

2019-10-16 09:34:16

对于ZYNQ来说PL(FPGA)开发是至关重要的,这也是ZYNQ比其他ARM的有优势的地方,可以定制化很多ARM端的外设,在定制ARM端的外设之前先让我们通过一个LED例程来熟悉PL(FPGA

2021-01-07 16:12:59

大家好我是FPGA世界的新手,我试图在Zynq-7000 AP SoC XC7Z020-CLG484上实现一些简单的工具实际上我只使用PL实现了一个简单的计数器(因此没有PS被配置/初始化),每隔1

2020-04-01 08:46:16

[Chipscope 16-119]实现调试核心u_ila_0 failed.ERROR:无法为u_ila_0生成核心。中止IP生成操作。错误:[Chipscope 16-218]尝试从IP缓存

2018-10-26 15:10:15

,请将对应案例目录拷贝至Windows非中文路径下。备注:Windows路径有长度限制,路径太长将会导致工程打开出错。在进行本文如下操作前,请先按照调试工具安装文档安装Xilinx Vivado开发工具

2021-11-11 09:38:32

为配置PL逻辑的控制器),也可以同时配置PS和PL逻辑,可见Zynq芯片可以灵活的搭建嵌入式平台实现不同的功能。这个通过模块图就可以看得更清楚了。http://www.xilinx

2016-10-05 14:05:31

你好我在Zynq 7010设计上添加了一个UART 16550 IP,中断直接连接到Zynq INTC。在petalinux中导入硬件设计后,pl.dtsi结构似乎没问题,但是当我编译图像并启动板

2020-04-08 07:50:34

亲爱的Xilinx,是否有可能更新ug873 zynq ctt的vivado版本?谢谢。伟

2020-03-27 09:41:17

灵活性也就越小。在Xilinx的FPGA器件中,IP核设计是非常重要并且必不可少的一部分,应该说,前述的软IP、固IP和硬IP,在我们Zstar板载的Zynq上都能够找到踪影。而对于Vivado来说

2019-09-06 08:13:18

/1XTQtP5LZAedkCwQtllAEyw提取码:ld9c 1概述基于Vivado的板级调试介绍,可以参考文档《玩转Zynq-基础篇:基于Vivado的在线板级调试概述.pdf》。这里我们以zstar_ex54工程为例,对FPGA的在线逻辑

2019-10-28 11:14:02

PL代码中VIO的配置和例化PL工程中,需要将作为开关量控制或状态显示的信号连接到VIO IP核的接口中。具体可以参考文档《玩转Zynq-工具篇:基于Vivado的Virtual IO在线板级调试

2019-11-21 10:04:31

`玩转Zynq连载5——基于Vivado的在线板级调试概述 更多资料共享 链接:https://share.weiyun.com/5s6bA0s Vivado在线调试概述FPGA的板级调试方法有很多

2019-05-24 15:16:32

今天给大侠带来简谈Xilinx Zynq-7000嵌入式系统设计与实现,话不多说,上货。

Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA

2024-04-10 16:00:14

方法不同的是,ZYNQ 7000 SoC总是最先启动PS内的处理器,这样允许PS上运行的基于软件程序用于启动系统并且配置PL,这样可以将配置PL设置成启动过程的一部分或者在将来的某个时间再单独的配置

2024-05-08 16:23:11

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 58287

58287

在Vivado下在线调试是利用ILA进行的,Xilinx官方给出了一个视频,演示了如何使用Vivado的debug cores,下面我根据这个官方视频的截图的来演示一下: 官方的视频使用的软件版本为

2017-02-08 08:52:44 3314

3314 Xilinx 的客户们分享了各种 Zynq SoC 的成功应用。这些成功案例详细描述了挑战、解决方案和所取得的成果。如欲了解其他 Xilinx 客户如何利用 Zynq SoC 将

2017-02-09 03:35:13 370

370 《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 4268

4268 Xilinx基于QEMU系统模拟器Xilinx/QEMU可用于模拟运行Zynq Linux的运行与调试。

2018-07-04 07:50:00 10066

10066 在对zynq进行Linux驱动开发时,除了需要针对zynq内ARM自带的控制器适配驱动外,还需要对zynq PL部分的IP核进行驱动开发。对于ARM来说,zynq PL部分的IP核就是一段地址空间

2018-06-30 15:10:00 10289

10289 1、 背景介绍 在zynq中,由于有PL部分的存在,操作系统需要对PL部分的物理地址进行操作,也就是对操作相关IP核的寄存器。除了在驱动中进行映射外(参看前一篇文章点击打开链接),可以直接在用户态进行地址映射访问。

2018-06-30 03:11:00 7783

7783

这个设计是根据avnet的PL dma带宽测试程序修改过来的,只使用了其中的HP0一个PLDMA。分为两个部分进行设计,第一部分是关于vivado中的block design部分,就是通过ip进行

2017-11-21 10:42:33 10025

10025

Xilinx Zynq™-7000

2018-06-04 13:47:00 4421

4421 FPGA设计中的信号连接到ILA核的时钟和探针输入如图1。这些信号附加到探针输入,以设计速度采样,并使用片上块RAM(BRAM)存储。核参数指定探针的数量、跟踪样本深度和每个探针输入的宽度。使用与FPGA的JTAG接口连接的自动实例化调试核心集线器与ILA核进行通信。

2018-08-04 10:29:00 2914

2914

Zynq-7000 PL端HDMI的显示控制 Zynq-7000 PS到PL端emio的使用 Vivado 专家文章:Tcl 是什么? Zynq-7000 ARM端MIO的使用 Zynq

2019-09-15 14:57:00 4227

4227 其实这儿便很简单了,可以直接在画布上添加一个ILA核,再把想要的信号线连进来就行了呀,都不需要在代码里定义这个ILA核。不过这样做就说明你还没能灵活的使用Xilinx的在线调试工具了,因为还有更简单的办法哈哈。

2018-11-14 10:47:56 7490

7490

Zynq-7000 AP SoC硬件和软件开发流程中,用于嵌入式软件开发的工具就是Xilinx SDK。Xilinx SDK是一个基于Eclipse的IDE,内含Xilinx提供的丰富的工具和软件包

2020-05-31 08:40:00 3277

3277 Xilinx合作伙伴和客户展示了他们如何使用Zynq仿真平台。

2019-01-03 13:14:43 5438

5438 了解使用Vivado 2016.1中引入的ECO流程进行调试的好处,以及在ECO布局中替换ILA调试探针所需的步骤。

2018-11-29 06:01:00 4313

4313

了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3838

3838 了解Xilinx FSBL如何操作以启动Zynq器件。

包括程序执行概述,调试技巧以及有关特定引导设备的信息。

还包括FSBL角度的启动安全性简要概述。

2018-11-23 06:32:00 5155

5155 了解如何使用Xilinx SDK创建Zynq引导映像。

我们将在通过Xilinx SDK创建Zynq引导映像时查看可以选择/添加的引导参数和分区。

2018-11-23 06:24:00 4428

4428 Vivado在使用A7芯片时,使用内部逻辑分析仪时,在非AXI总线下最多只能绑定64组信号(例化一个或者多个ILA模块,信号组数相加不能超过64),如果超过64组会出现错误。

2018-11-23 09:38:55 2045

2045 Zynq-7000所有可编程SoC应用程序开发都从Zynq硬件平台开始。该硬件平台定义了如何配置ARM处理系统(PS),并为可编程逻辑(PL)提供实际的硬件设计。该硬件平台必须在vivado中配置

2019-02-13 17:49:46 28

28 FPGA的调试是个很蛋疼的事,即便Vivado已经比ISE好用了很多,但调试起来依旧蛋疼。即便是同一个程序,FPGA每次重新综合、实现后结果都多多少少会有所不同。而且加入到ila中的数据会占用RAM资源,影响布局布线的结果。

2020-03-08 17:35:00 12847

12847 ZYNQ中包含了两个部分,双核的arm和FPGA。根据XILINX提供的手册,arm模块被称为PS,而FPGA模块被称为PL。

2020-03-15 17:13:00 8302

8302 Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2022-02-08 14:19:49 2342

2342

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将

2022-02-08 11:48:37 2198

2198

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

2022-02-08 11:35:19 28930

28930

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

2021-01-22 07:52:04 20

20 初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将

2021-01-26 07:30:29 20

20 UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

DDR PHY 与电路板调试:

Zynq UltraScale...

2021-02-23 06:00:10 15

15 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 71

71 刚学ZYNQ的时候,看到里面反复提到PS和PL,还以为PS是PhotoShop的意思,PL是哪种型号的简称。 稍微了解之后才知道,ZYNQ是ARM和FPGA的组合,PS是programming

2021-06-18 16:09:46 11175

11175 ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2021-12-22 19:11:29 10

10 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

2022-10-19 09:11:55 2023

2023 电子发烧友网站提供《Xilinx Zynq上FreeRTOS的Tracealyzer.zip》资料免费下载

2022-12-07 14:59:27 5

5 Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 9161

9161 本文介绍广州星嵌DSP C6657+Xilinx Zynq7035平台下Xilinx Zynq7035算力指标。

2023-07-07 14:15:01 2499

2499

ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

2023-08-11 09:36:34 13623

13623

《Vivado Design Suite 用户指南:编程和调试》 文档涵盖了以下设计进程: 硬件、IP 和平台开发 : 为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD

2023-10-25 16:15:02 1642

1642

资料\Demo\All-Programmable-SoC-demos\”目录下。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linu

2023-01-03 15:50:37 19

19 ILA应该是调试AMD-Xilinx FPGA最常用的IP。

2024-05-01 10:43:00 2308

2308

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心。

2025-10-15 10:33:19 737

737

电子发烧友App

电子发烧友App

评论