这篇文章记录ZYNQ7020的PS端的基本开发流程,关于PL端的开发流程,参考之前文章,这里放个超链接。

本篇文章,以配置一个PS端的UART外设,并打印一句话《hello ZYNQ7020,Author:liushuhe 2020.11.26》来演示

ZYNQ7020的基本开发流程,本篇文章需要一点点的C语言知识,不会也不影响实验的,跟着步骤做就行了。

一、任务分工

ZYNQ芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,虽然PS端的ARM是硬核,但是在ZYNQ当中也要将ARM硬核添加到工程当中才能使用,FPGA工程师负责把Vivado工程搭建好,提供好硬件给软件开发人员,软件开发人员便能在这个基础上开发应用程序 ,软件开发人员,不用关心FPGA的部分。

二、FPGA工程师搭建硬件平台

我们这里演示搭建一个带UART和arm A9处理器的硬件平台

1.1、建立vivado工程

创建一个“ps_uart”的工程,具体过程,参考我文章开头超链接文章;

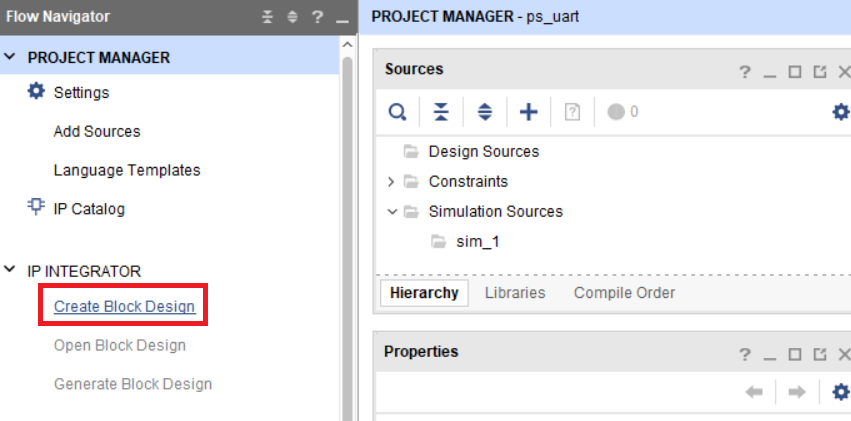

1.2、点击“Create Block Design”,创建一个Block设计,也就是图形化设计

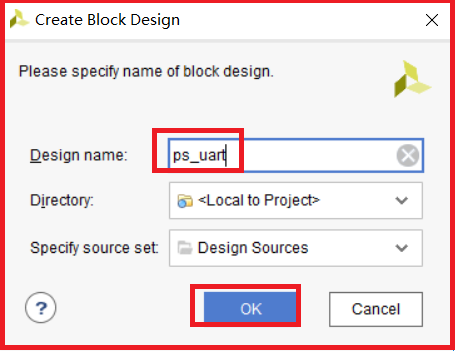

1.3、“Design name”可以不修改,我改成ps_uart便于识别

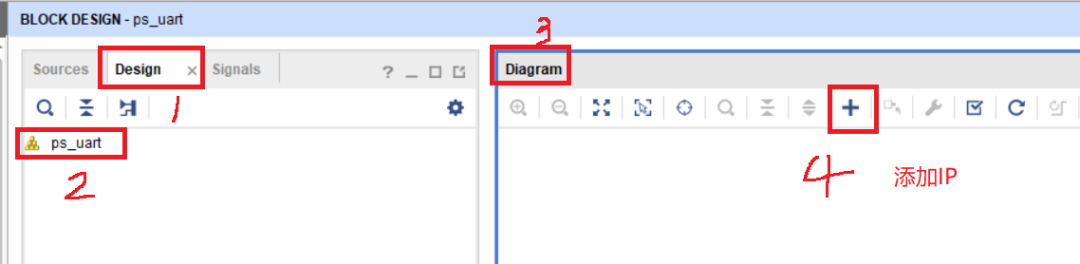

1.4、点击“Add IP”快捷图标

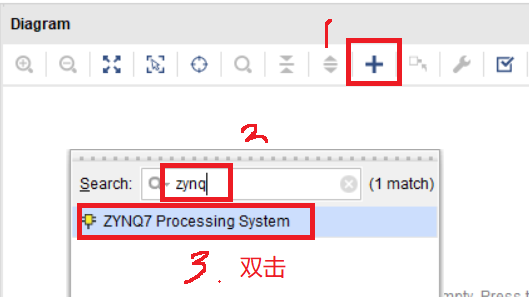

1.5、搜索“zynq”,在搜索结果列表中双击“ZYNQ7 Processing System

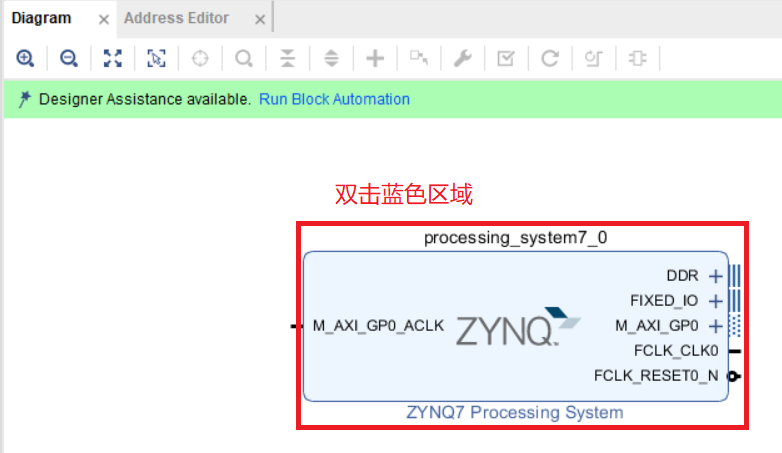

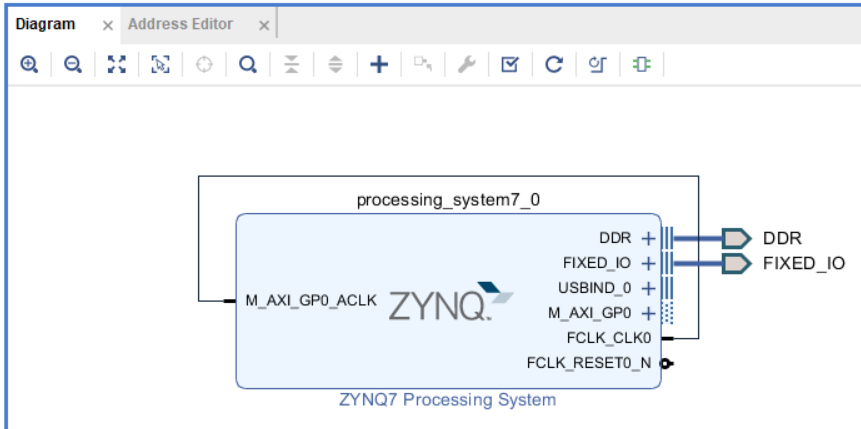

1.6、双击Block图中的“processing_system7_0”(直接双击蓝色区域),配置相关参数

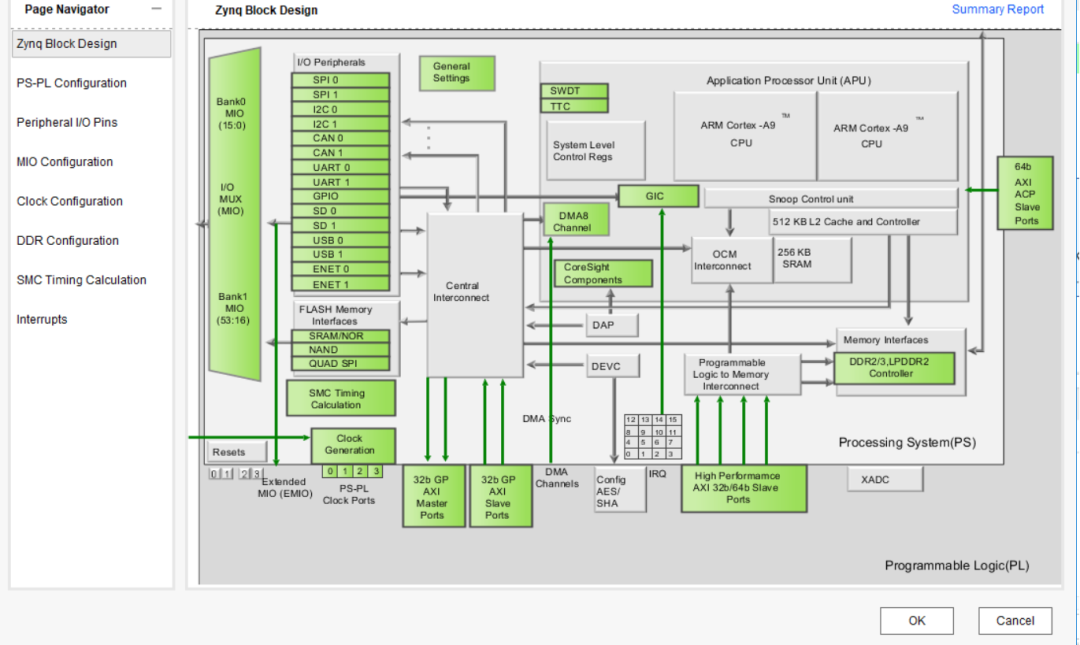

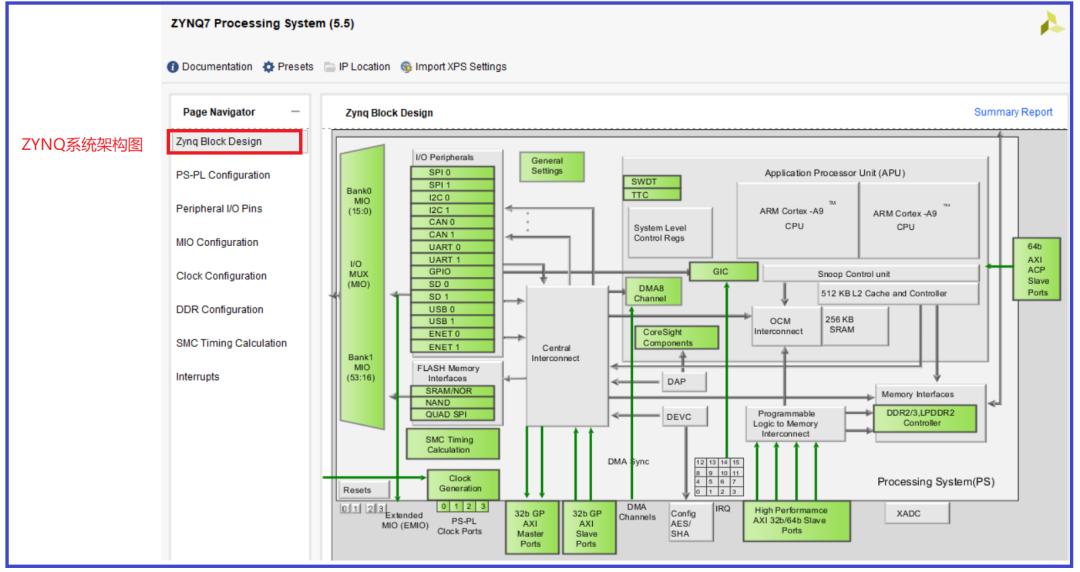

1.7、首先出现的界面是ZYNQ硬核的架构图,可以很清楚看到它的结构,可以参考 官方文档,在官网搜索ug585 即可

1.8、图中绿色部分是可配置模块,可以点击进入相应的编辑界面

1.9、也可以在左侧的窗口进入编辑 ,下面分别介绍左侧选项代表的功能;

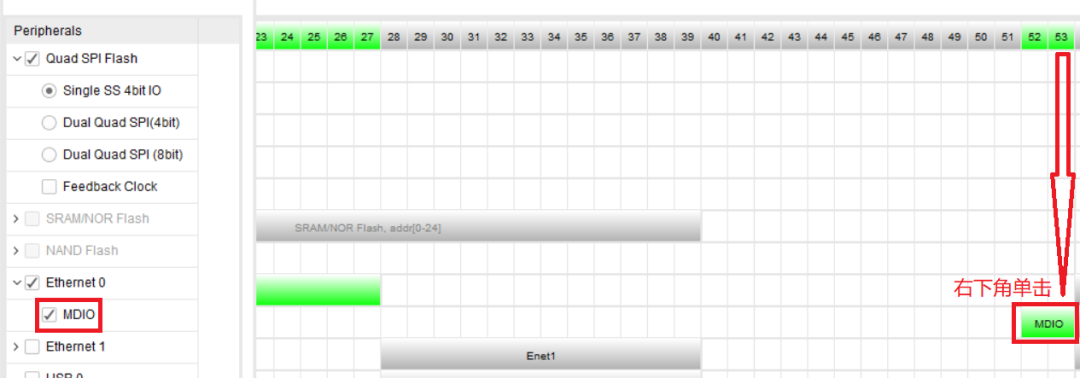

2.0、Zynq 块设计参数配置,单击绿色块右下角,可以进行参数配置

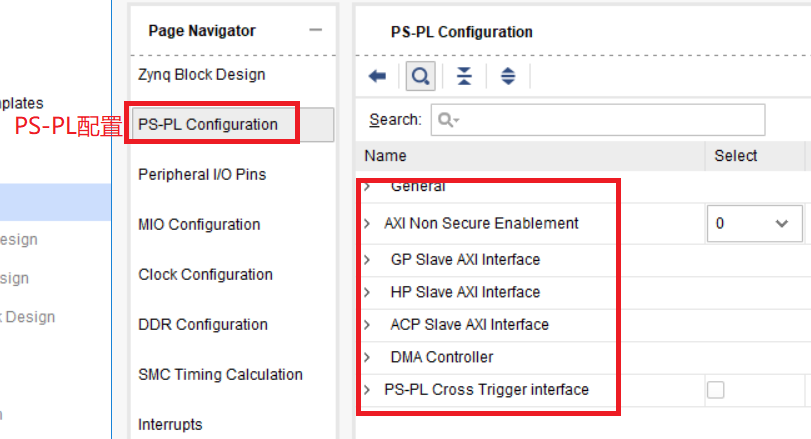

2.1、PS-PL Configuration 配置界面,主要是进行PS与PL之间接口的配置,主要是AXI接口,这些接口可以扩展PL端的AXI接口外设

核。

2.2、我们这篇文章是PS开发流程,关于PS-PL Configuration 配置在这里保持默认,在后面的实验中我再补充

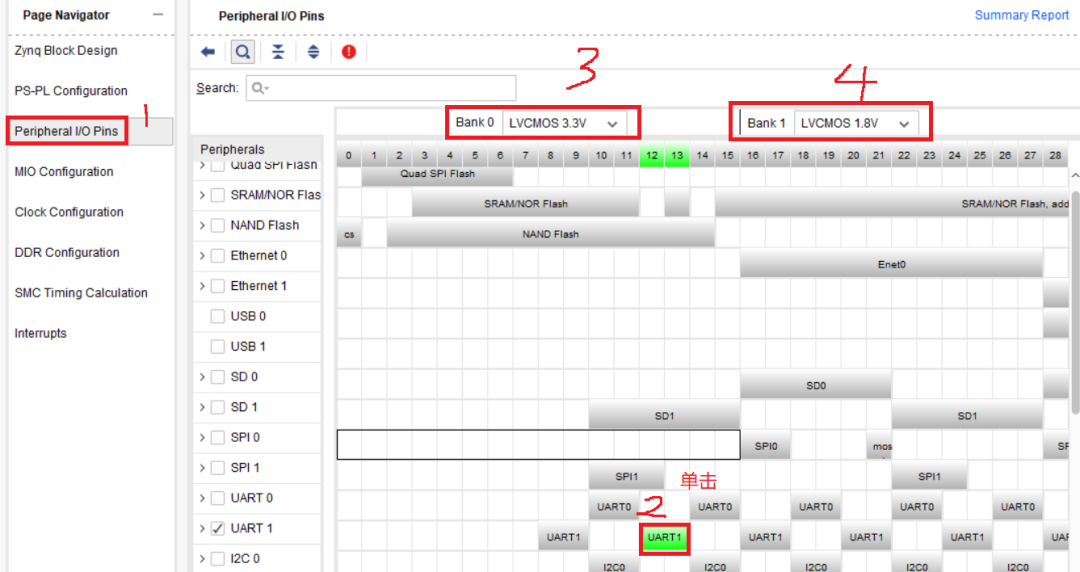

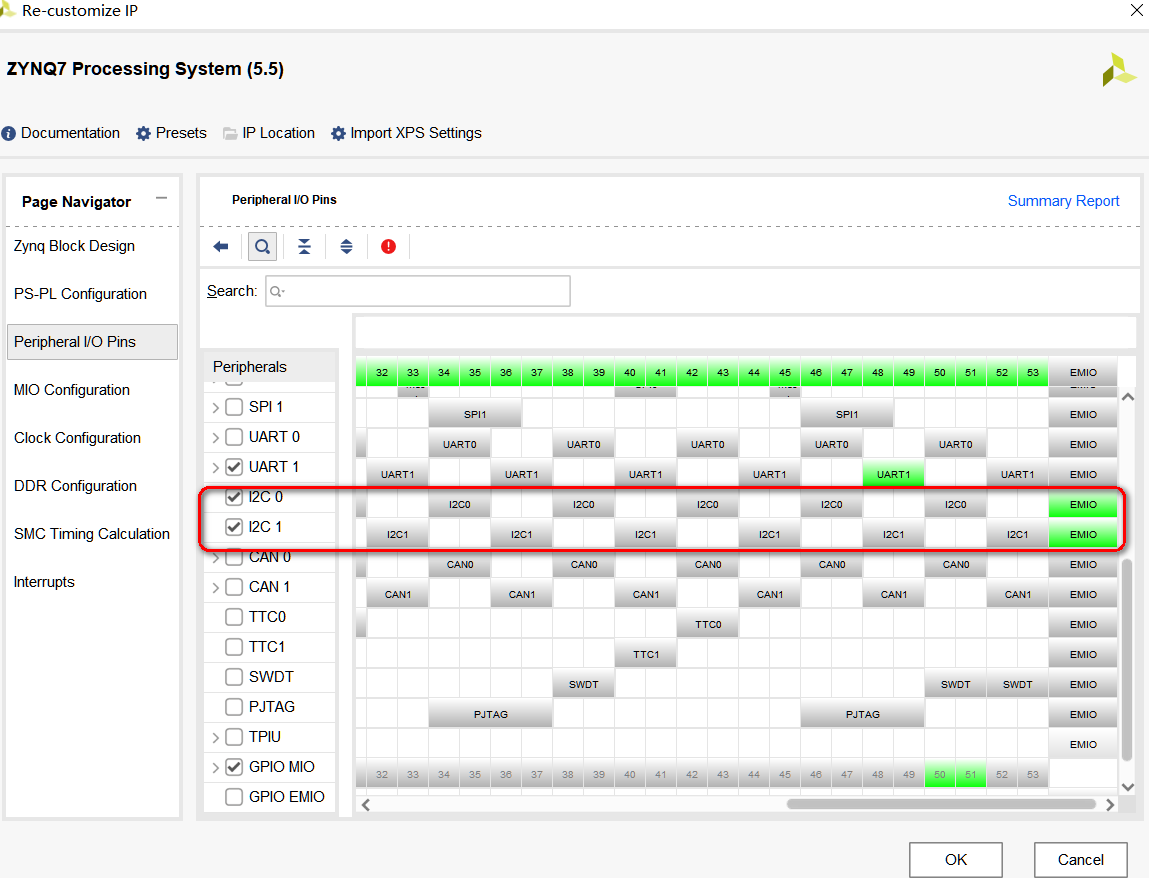

2.3、外设配置,ZYNQ的PS端外设很多是复用的 ,同一引脚可以配置为不同的功能

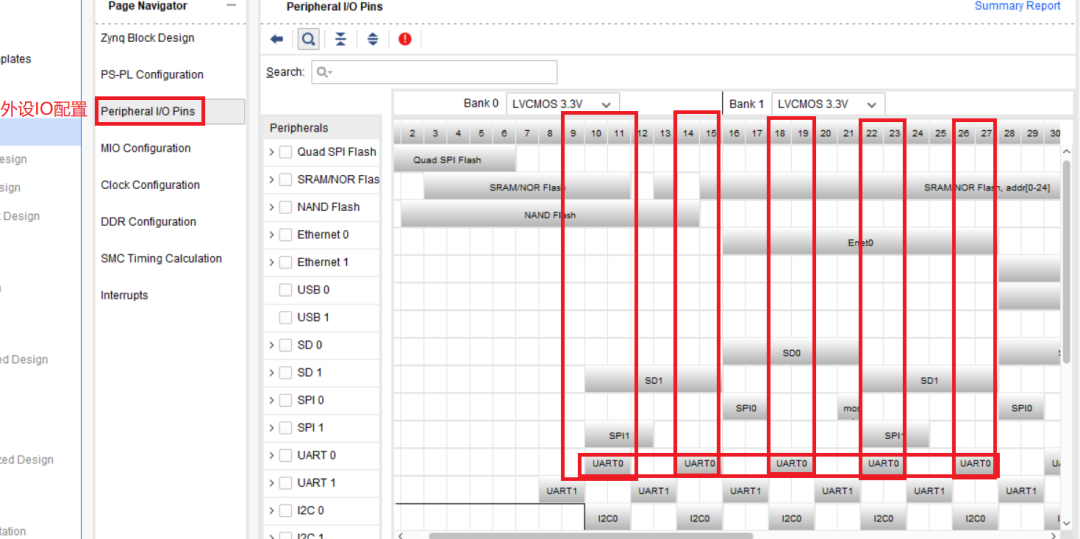

zynq内部只有2个串口,UART0、UART1、我们看UART0可以接在(10、11)/(14、15)/(18、19)/(22、23)/(26、27)

2.4、配置串口,我们的ps_uart需要一个串口来打印消息,查看ZYNQ7020开发板的原理图

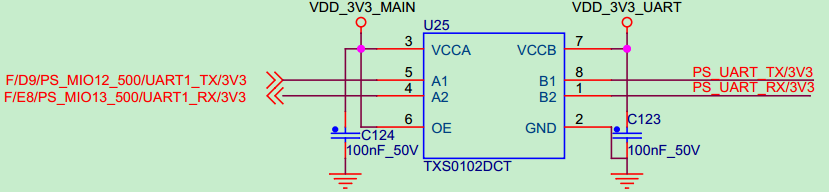

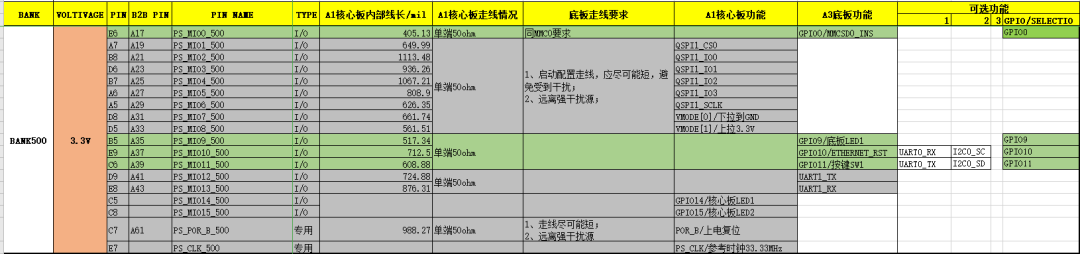

从原理图看出,ZYNQ的PS端的串口,连接的是MIO12、MIO13端口,并且电源是3.3v

2.5、从I/O分配看,MIO12、MIO13是串口1,在MIO12、MIO13引脚对应串口上单击,会看见该模块变为绿色,即代表分配成功

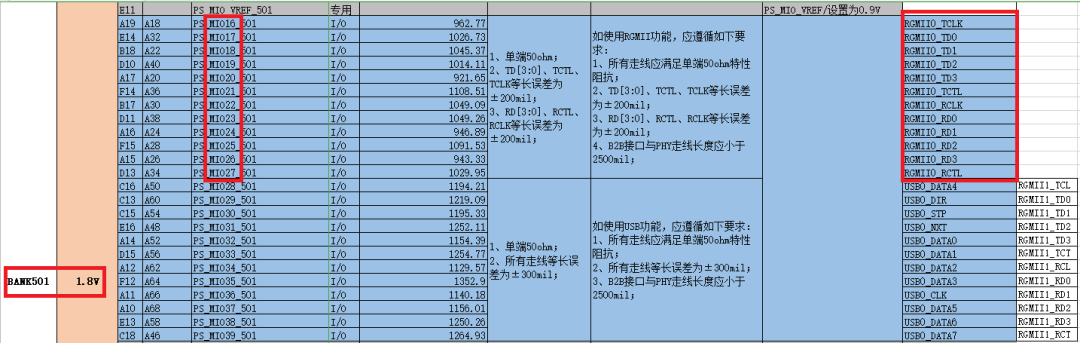

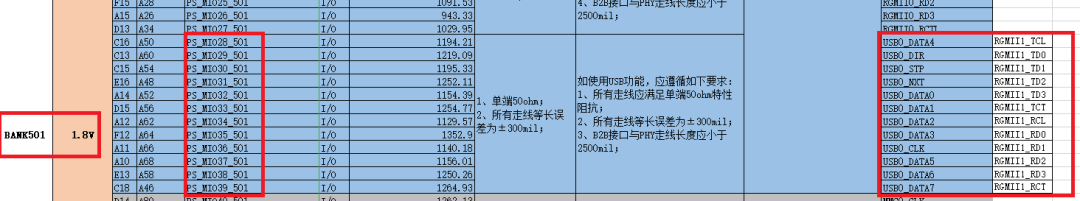

关于BANK0、BANK1的电压,由于创龙没有给核心板的原理图,但是给了一个WORD的描述文档,大家也要熟悉这个方式

国内很多厂家都是这样,属于技术保密

按照上述表格分配UART1电压和引脚

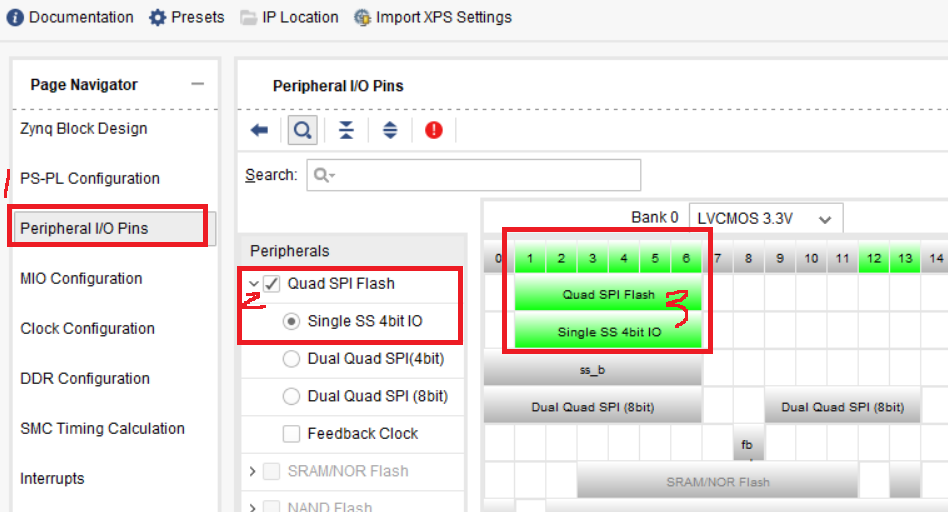

2.6、配置QSPI,QSPI可以作为ZYNQ的启动存储设备,ZYNQ可以通过读取QSPI中存储的启动文件加载ARM和FPGA

从核心板word表格和创龙给的例程,得知我们选择Quad SPI Flash为Single SS 4bit IO

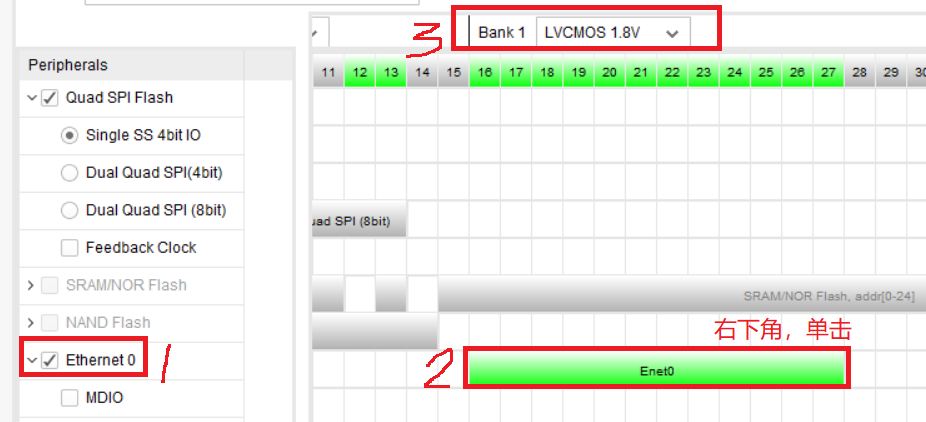

2.7、配置以太网,在PS端设计有以太网接口

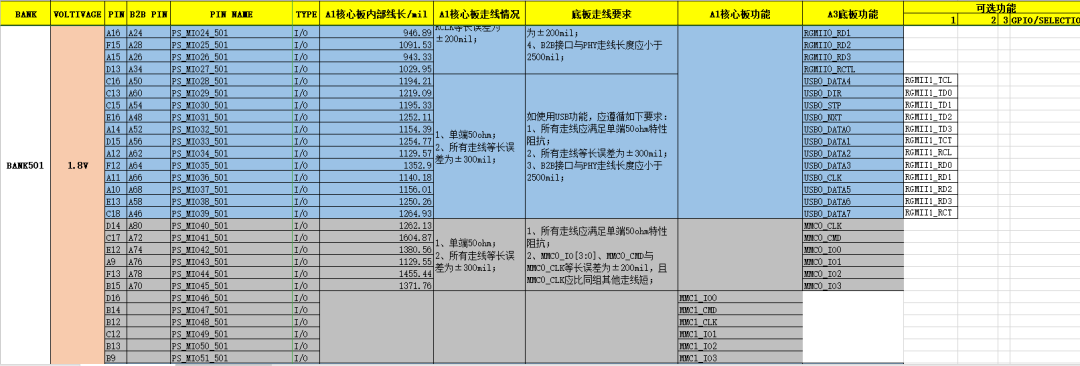

1、根据原理图选择Ethernet 0到MIO16-MIO27

电压是1.8v

2、配置PHY寄存器配置接口,选择MDIO并配置到MIO52-MIO53

2.8、配置USB0到MIO28-MIO39

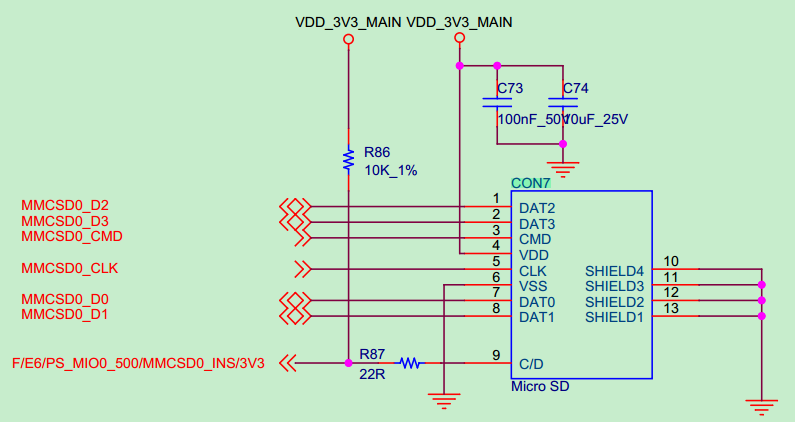

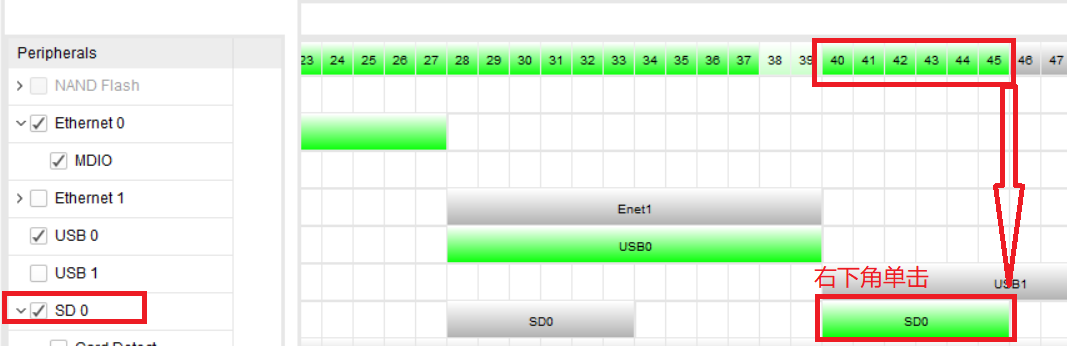

2.9、ZYNQ还可以SD卡启动

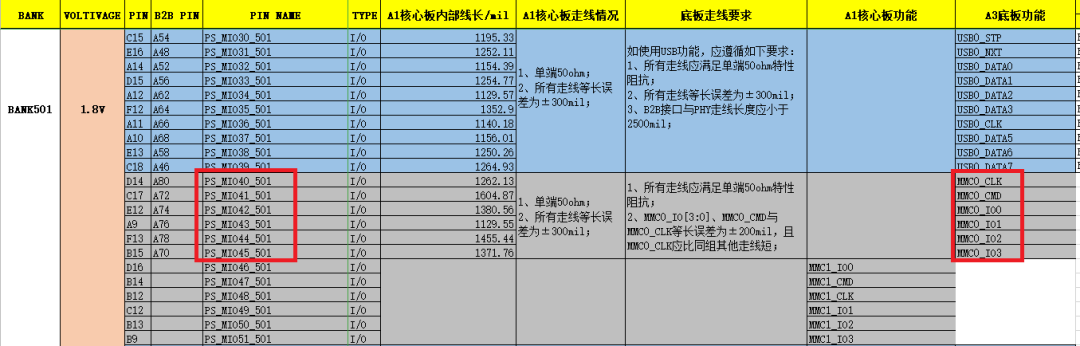

查看底板原理图,选择 SD 0,配置到 MIO40-MIO45,选择Card Detection MIO0,用于检测 SD 卡的插入。

1、配置SD0

2、选择Card Detection MIO0,用于检测SD卡的插入

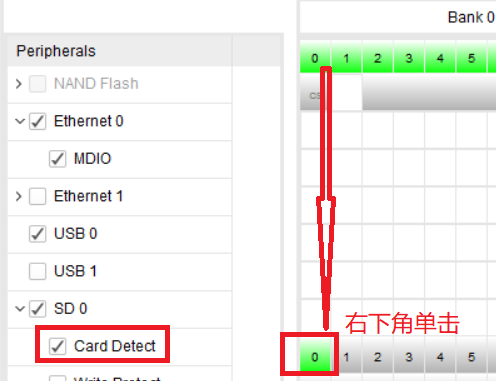

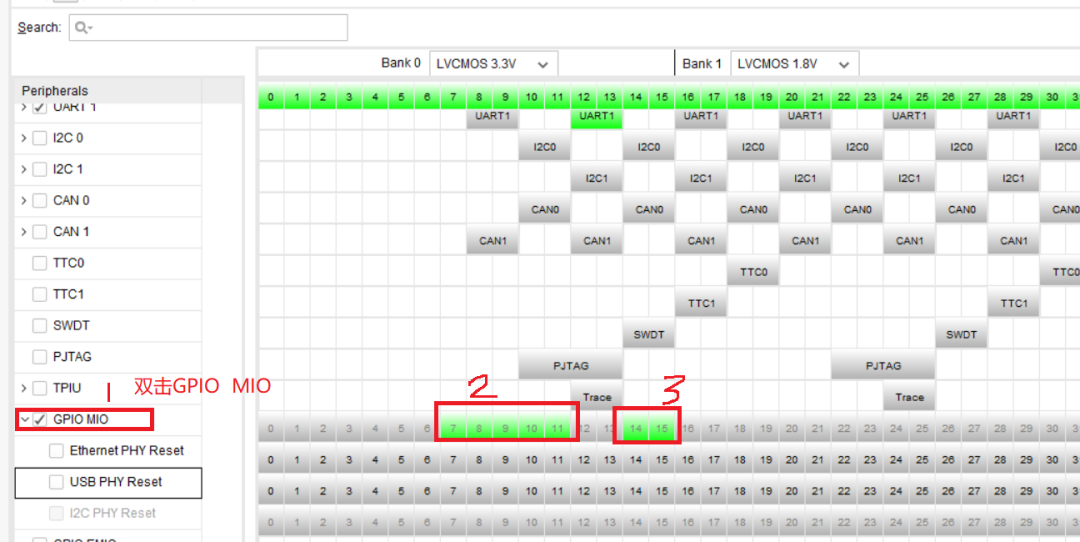

3.0、控制剩余未分配的MIO,用作GPIO ,打开GPIO MIO,PS便可以配置

1、双击GPIO MIO当出现打钩的提示时,软件会自动把我们未使用到的IO分配为GPIO

2、到这里引脚分配全部完成,如果以后做实验需要配置其他外设,可以参考这个文章,作相应的修改即可

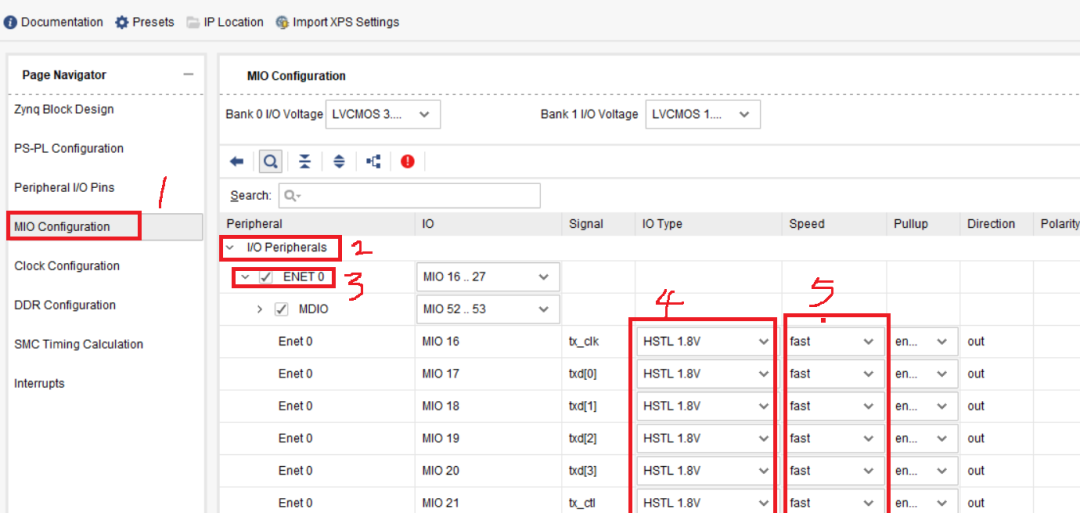

3.1、MIO配置

修改 Enet0的电平标准为 HSTL 1.8V, Speed 为 fast,这些参数非常重要,如果不修改,网络可能不通。其他部分保持默认。

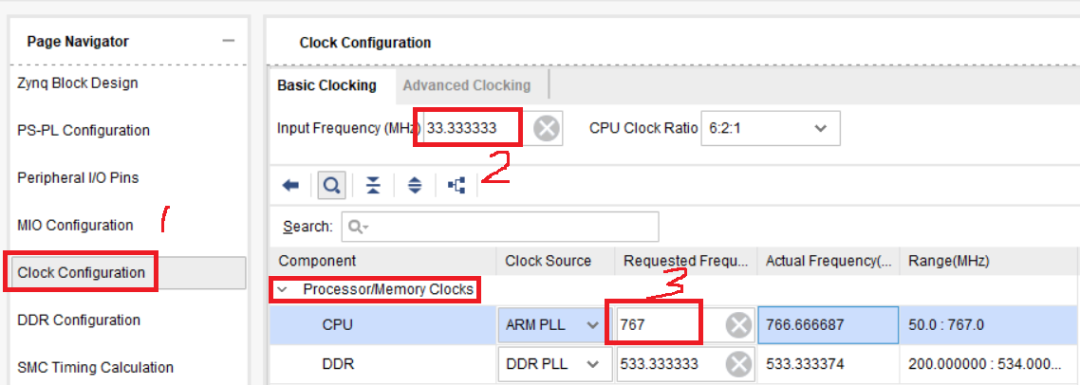

3.2、时钟配置

在“Clock Configuration”选项卡中我们可以配置PS时钟输入时钟频率,这里默认是33.333333,和板子上一致,不用修改,

CPU 频率改为 767Mhz,同时 PS 还可以给 PL 端提供 4 路时钟,频率可以配置,这里不需要,所以保持默认即可。

还有 PS 端外设的时钟等也可以进行配置,这里保持默认。

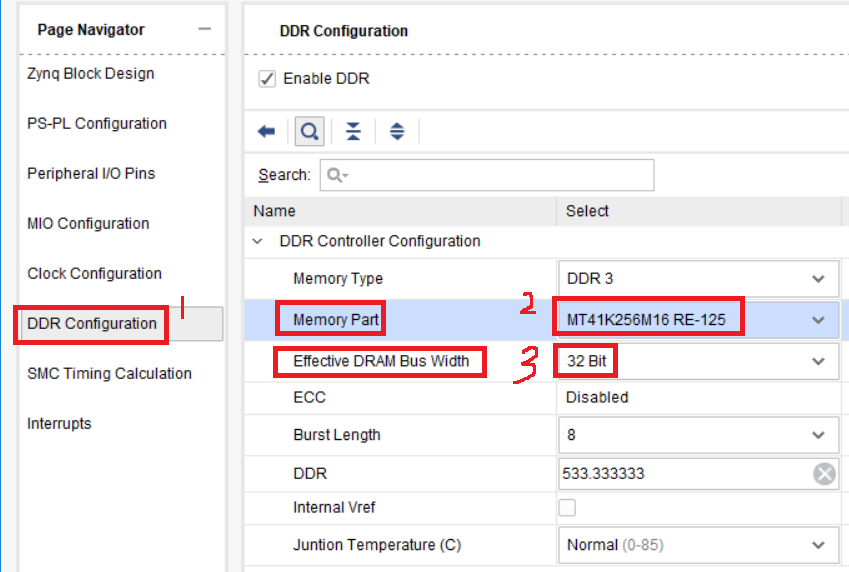

3.3、DDR3配置

在“DDR Configuration”选项卡中可以配置PS端ddr的参数

根据创龙的例程,内存芯片我们选择《MT41K256M16 RE-125》,Effective DRAM Bus Width 选择《32bit》

其他部分保持默认,点击OK

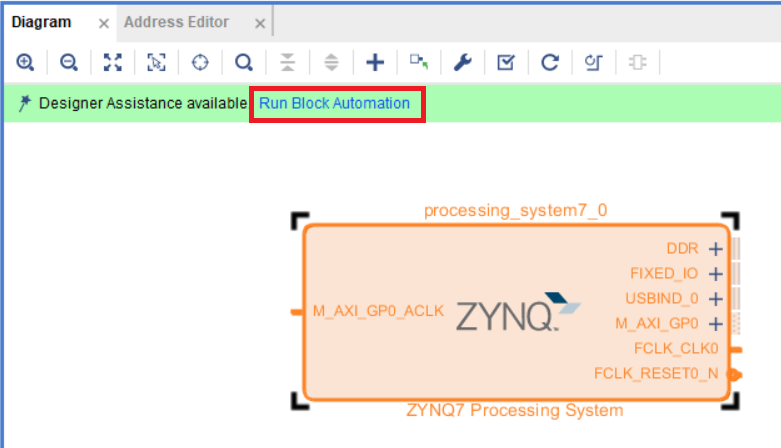

3.4、到这里ZYNQ核的配置完成,我们配置参数及导出硬件信息

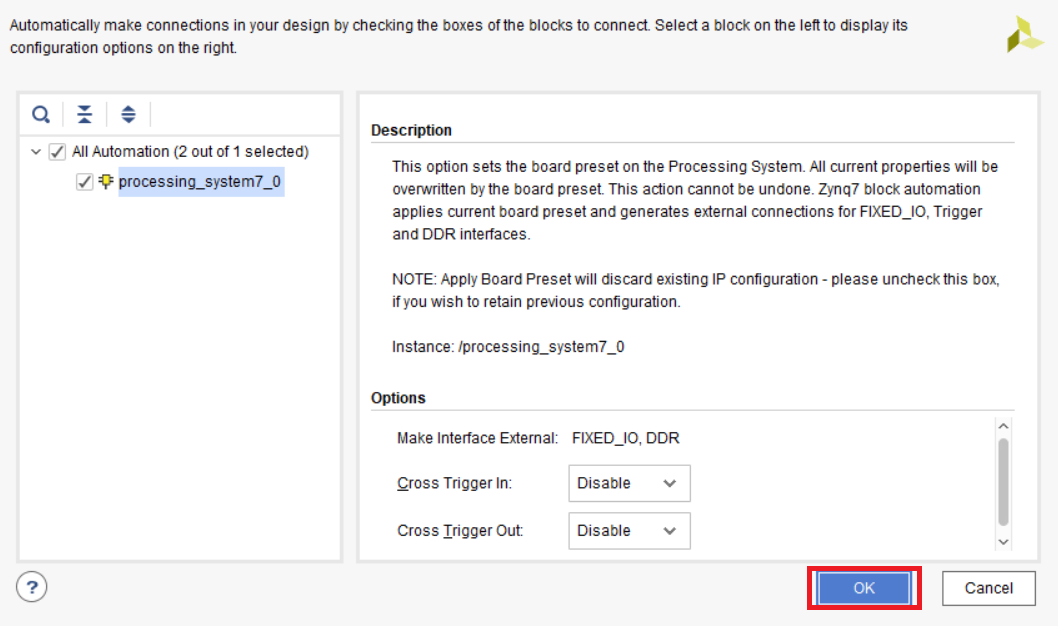

1、点击“Run Block Automation”,vivado软件会自动完成一些导出端口的工作

2、按照默认点击“OK”

3、连接FCLK_CLK0到M_AXI_GP0_ACLK,按Ctrl+S保存设计

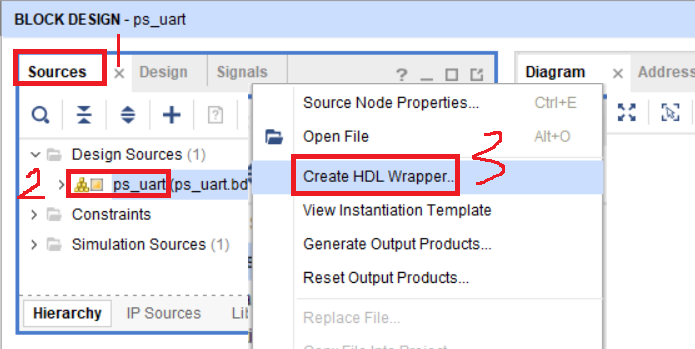

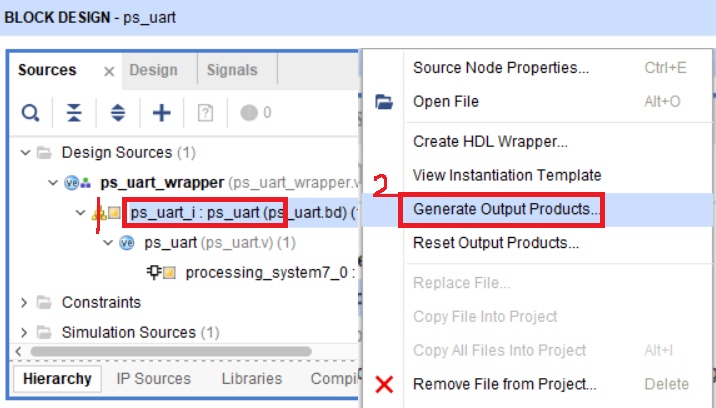

4、选择Block设计,右键“Create HDL Wrapper...”,创建一个Verilog或VHDL文件,为ps_uart生成HDL顶层文件

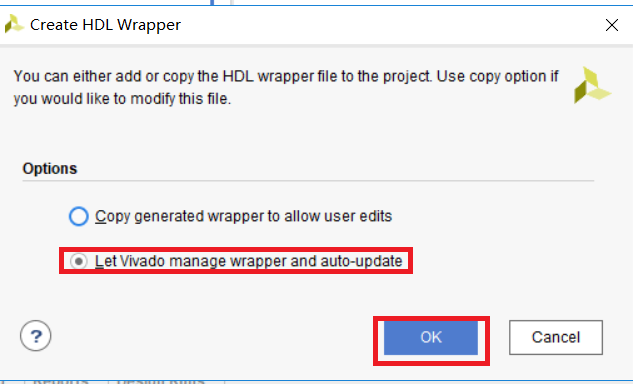

5、在弹出对话框,选择让vivado软件自动更新 顶层文件

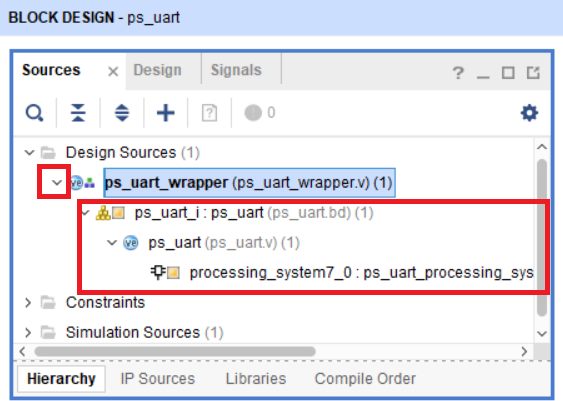

6、展开设计可以看到PS被当成一个普通IP来使用 ,之前生成那个顶层文件,其实就是为了把我们的硬件配置

生成一个IP核,供我们调用

7、选择block设计,右键“Generate Output Products”,此步骤会生成block的输出文件,包括IP,例化模板, RTL 源文件, XDC 约束,第三方综合源文件等等。供后续操作使用。

8、点击“Generate”

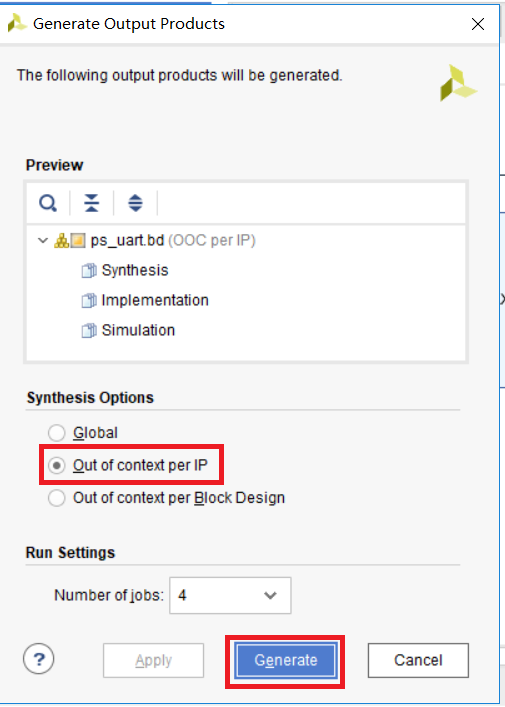

9、PS端的引脚不需要绑定 ,因为在生成的IP文件包含了PS端引脚分配的XDC文件

在IP Sources,Block Designs->ps_uart->Synthesis中,可以看到处理器的XDC文件,绑定了PS端的IO,因此不需要再新建XDC绑定这些引脚

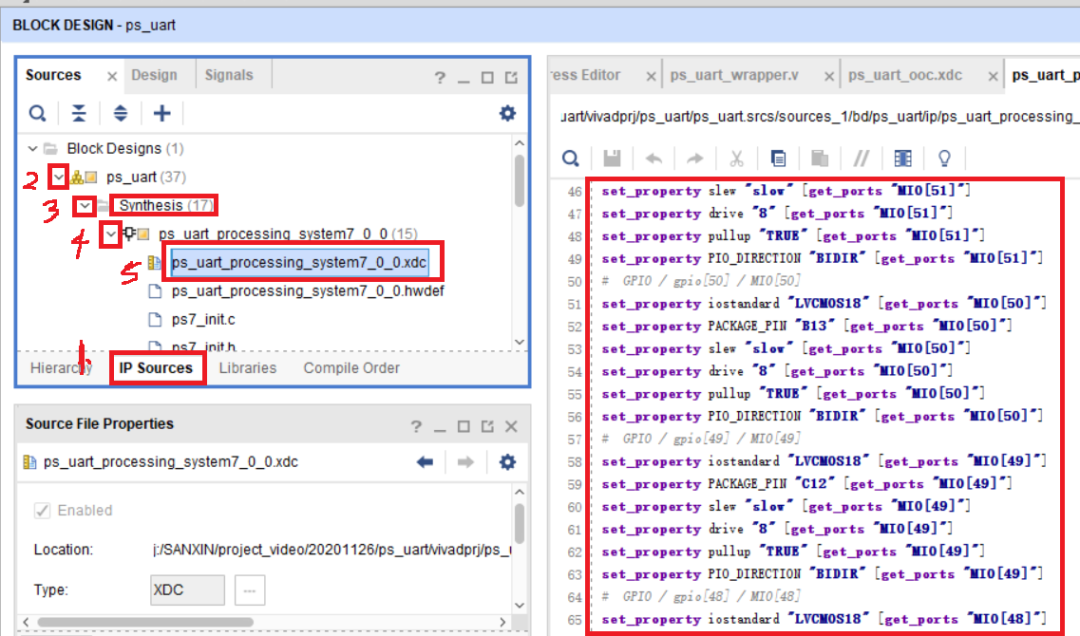

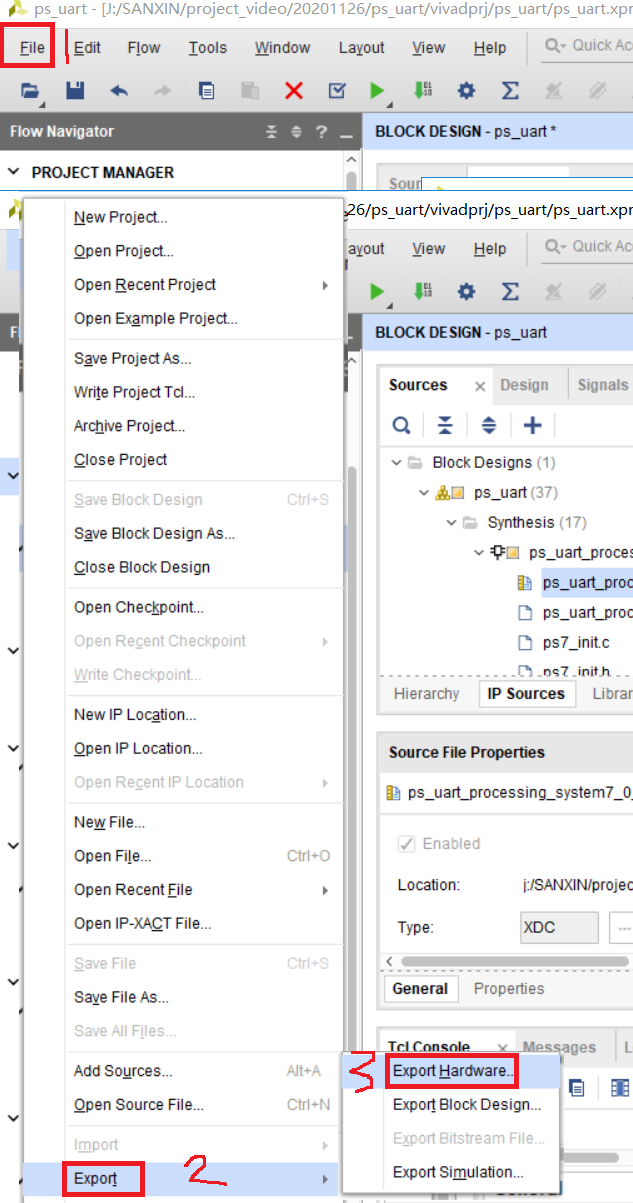

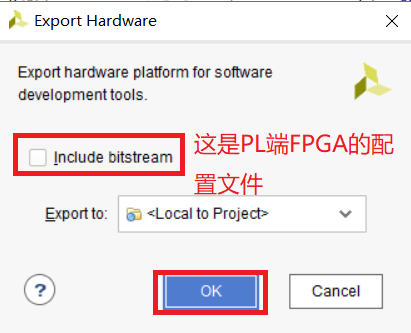

10、在菜单栏“File -> Export -> Export Hardware...”导出硬件信息,这里就包含了 PS 端的配置信息。

11、在弹出的对话框中点击“OK”

12、因为我们这个实验仅仅是使用了PS的串口,不需要PL参与,这里就没有使能“Include bitstream” ,关于PS-PL的联合实验,我会另写一篇

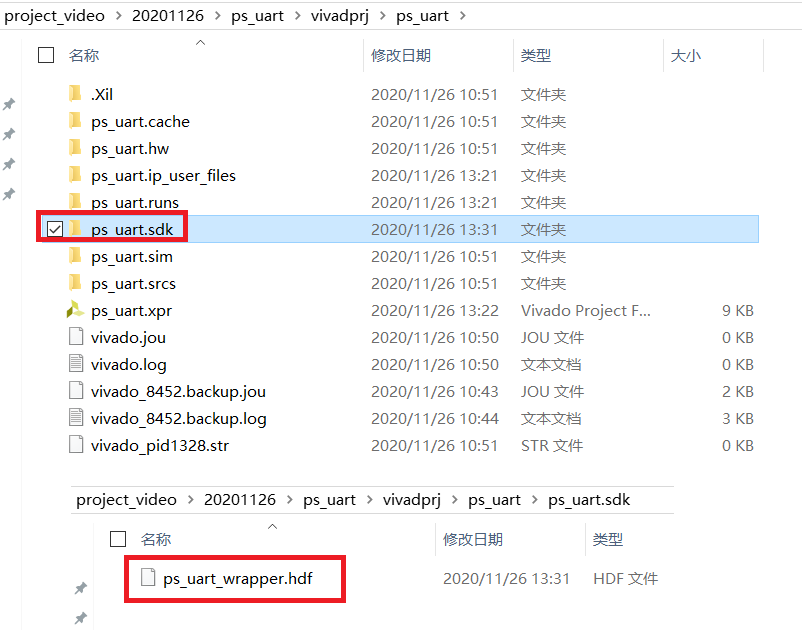

13、此时会多出 xx.sdk 文件夹,并且有个 hdf 文件,这个文件就是这个文件就包含了 Vivado 硬件设计的信息,供软件开发人员使用。

14、到此为止, FPGA 工程师工作告一段落,剩下的工作交给ARM软件开发人员。

二、ARM软件编写C语言程序,在串口打印一句话《hello ZYNQ7020,Author:liushuhe 2020.11.26》

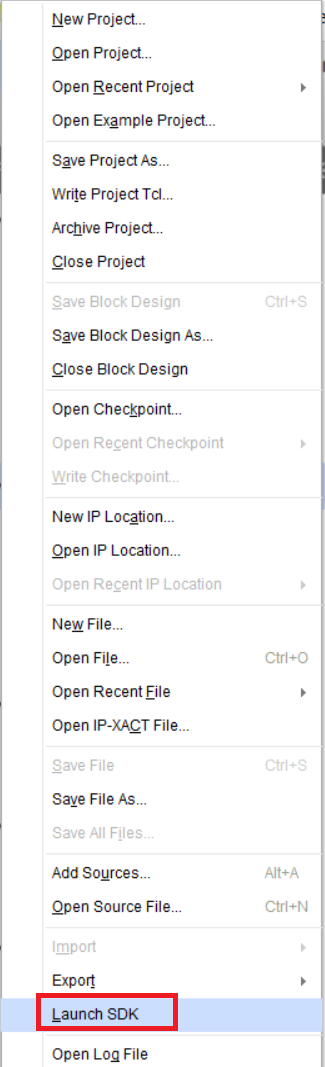

1、点击Vivado菜单“File -> Launch SDK”,启动SDK

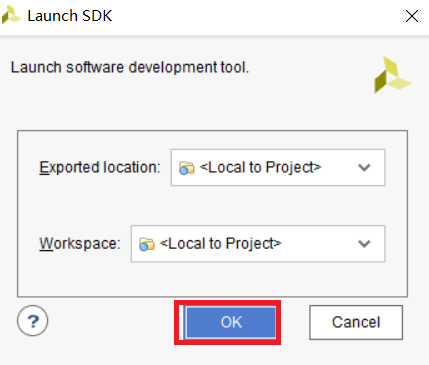

2、在弹出的对话框选择OK

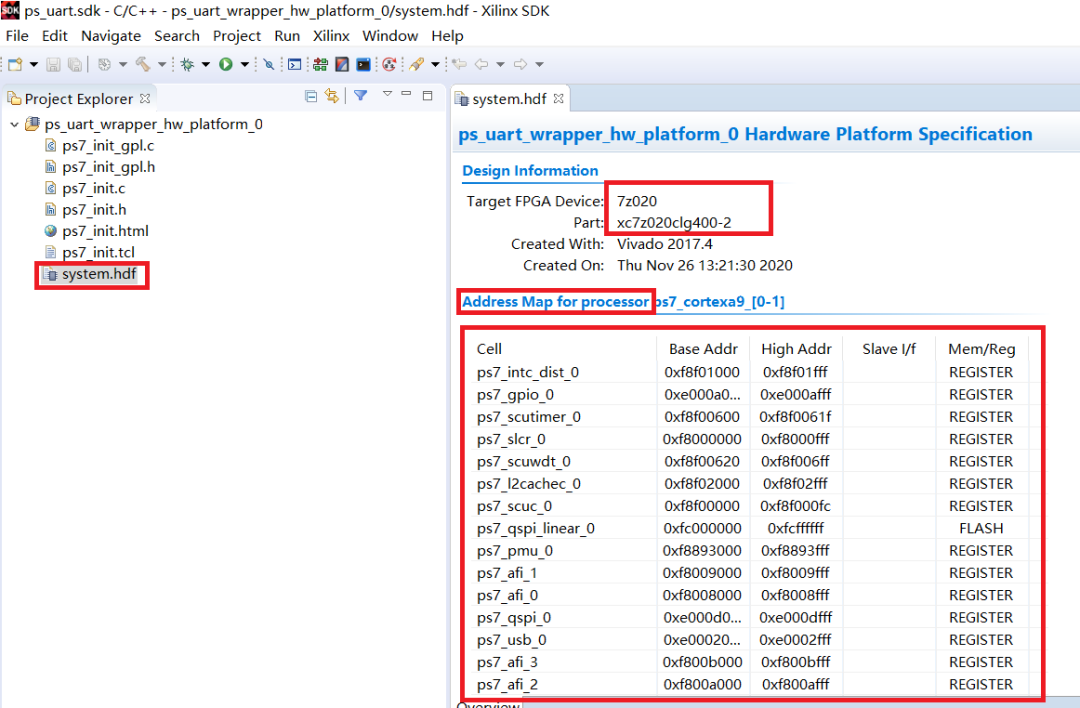

3、启动SDK后我们会看到一个文件夹,有一个名为"system.hdf”文件,这个文件就包含了

Vivado硬件设计的信息,可以给软件开发使用,也可以看到 PS 端外设的寄存器列表。

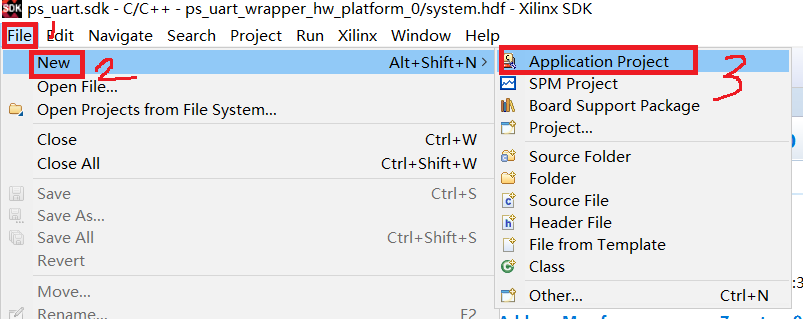

4、在SDK的菜单“New -> Application Project”,建立一个APP工程

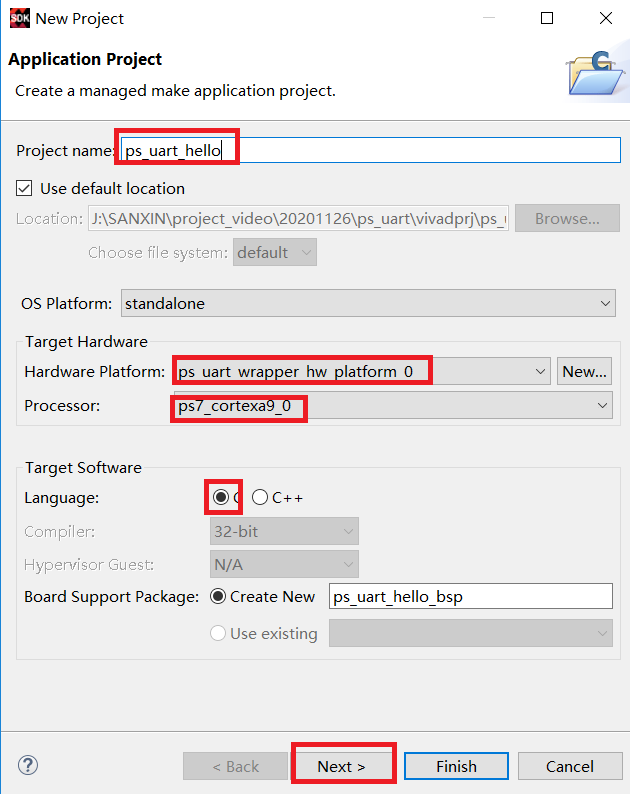

4、在弹出的对话框中,“Project name”填写“ps_uart_hello”,硬件平台选择我们自己定义的ps_uart_wrapper_hw_platform

语言C、其他默认,点击“Next”

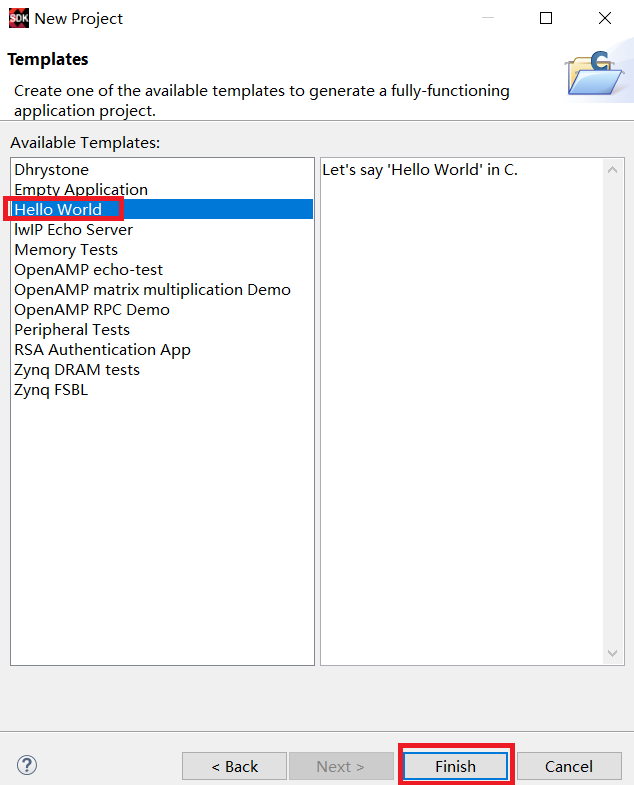

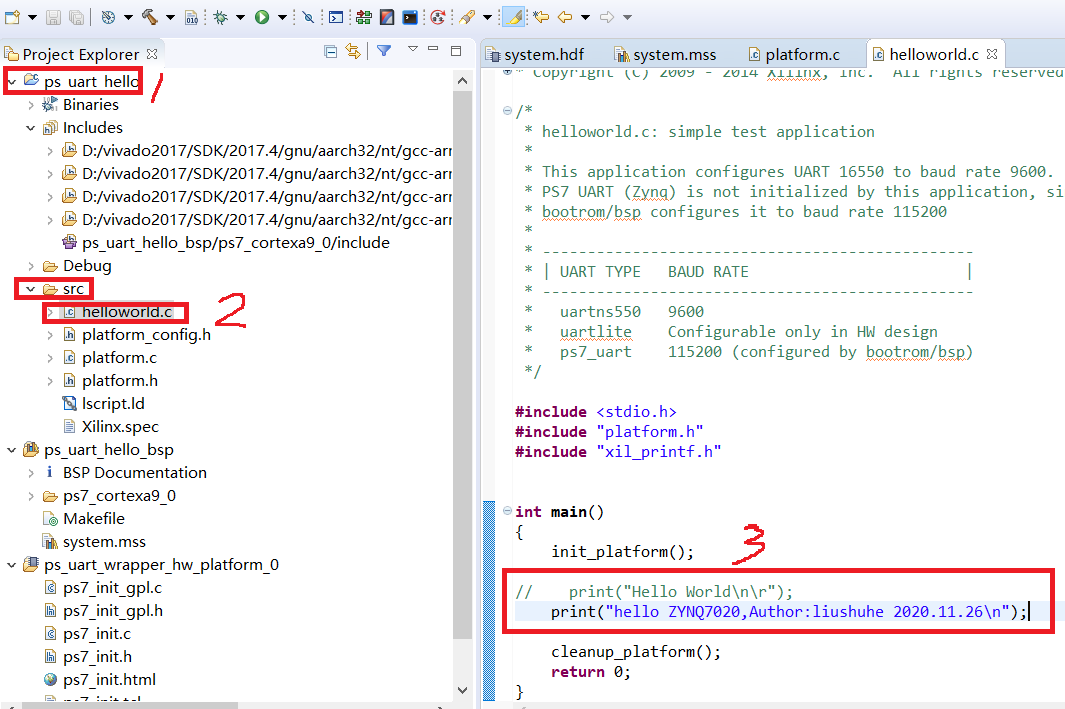

5、模板选择《hello world》,点击Finish

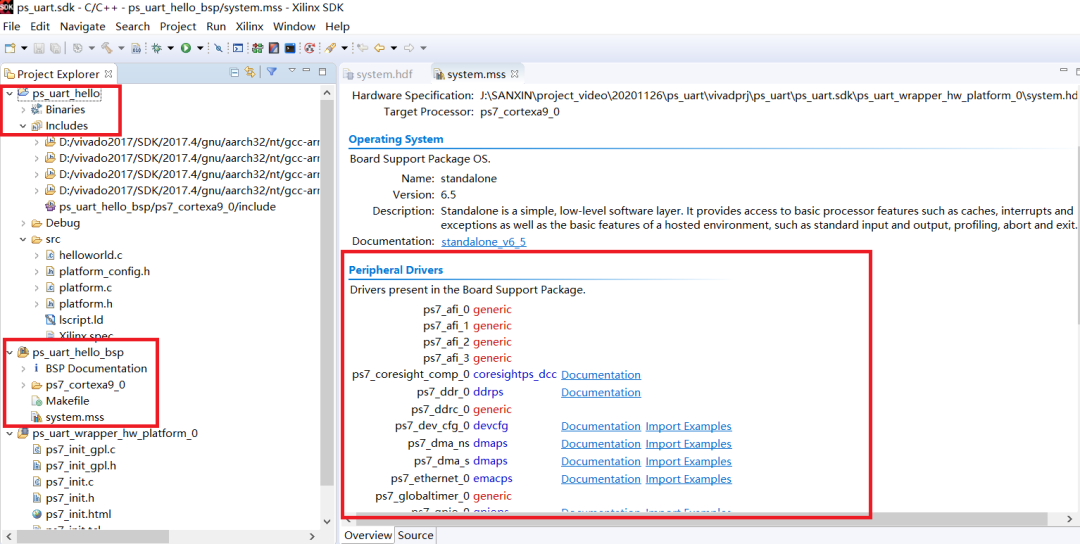

6、可以看到SDK创建了一个“ps_uart_hello”目录,还有一个“ps_usrt_hello_bsp”的目录,在“ps_usrt_hello_bsp”目录中可以找到很多有用的信息,软件开发人员比较清楚,BSP也就是Board Support Package板级支持包的意思,里面包含了开发所需要的驱动文件,用于应用程序开发。

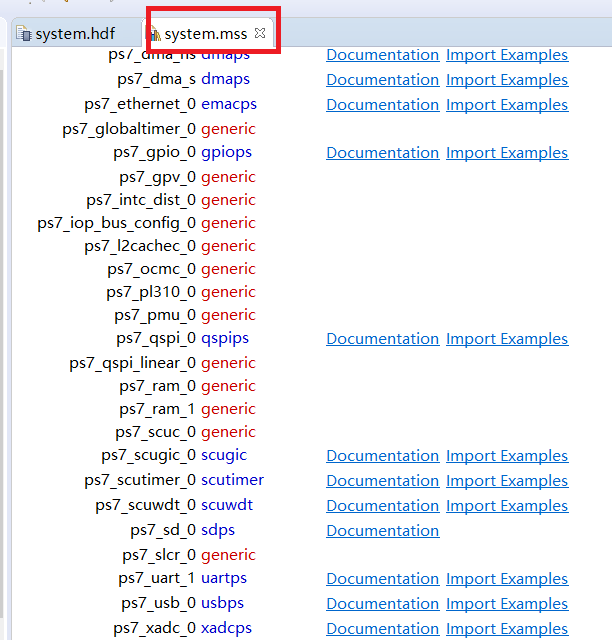

7、双击“system.mss”,还可以看到有些PS外设还提供了例程,这是用来了解学习这些外设的

第一手资料。驱动文档说明可以在 Documentation 中找到。通过 Import Examples 引入官方

例子,加快学习。

8、连接JTAG线到开发板、UART的USB线到PC

9、打开串口终端调试工具,串口根据电脑的COM口设置,波特率设置为115200

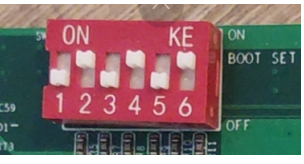

10、将开发板的启动模式设置到JTAG模式

开发板设置拨码为【010101(1~6 JTAG模式)】、【100101(1~6 QSPI模式)】、【101001(1~6 SD卡模式】

11、给开发板上电,准备运行程序

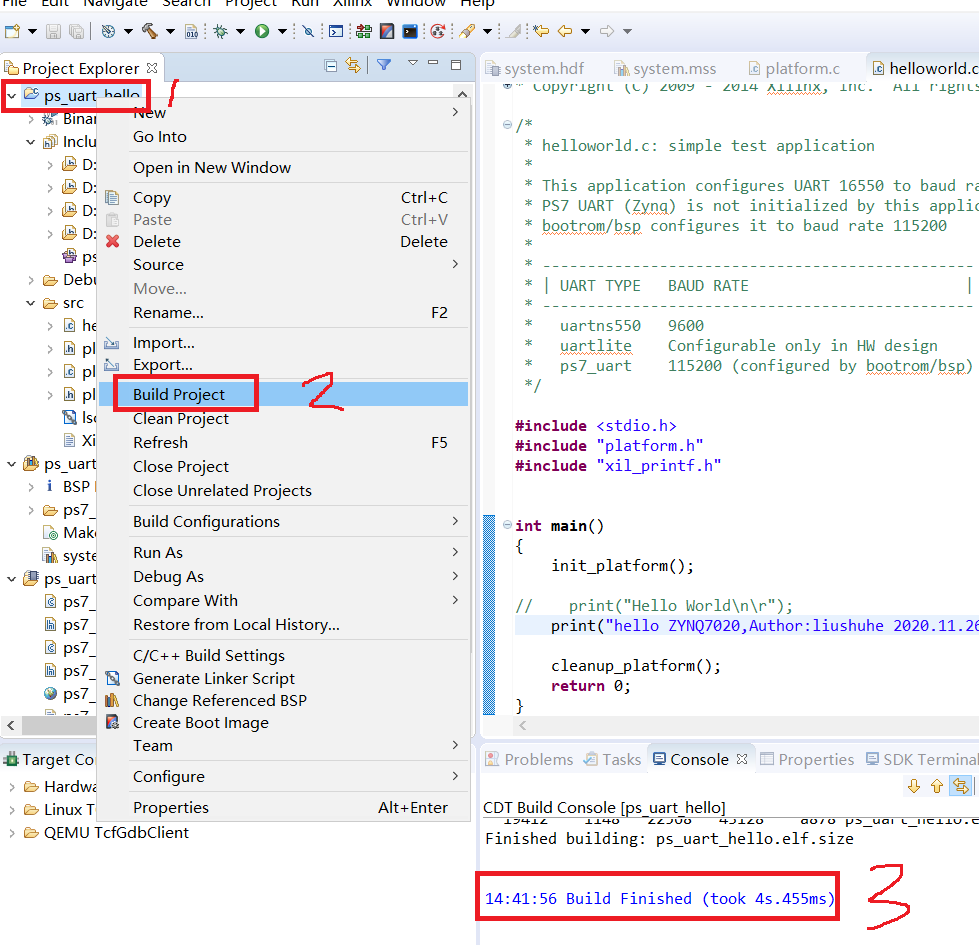

1、修改helloword.c,将printf打印修改为printf("hello ZYNQ7020,Author:liushuhe 2020.11.26 ");

2、编译代码,右键单击ps_uart_hello,在弹出的列表选择Build Project,编译完成可以看看没有报错

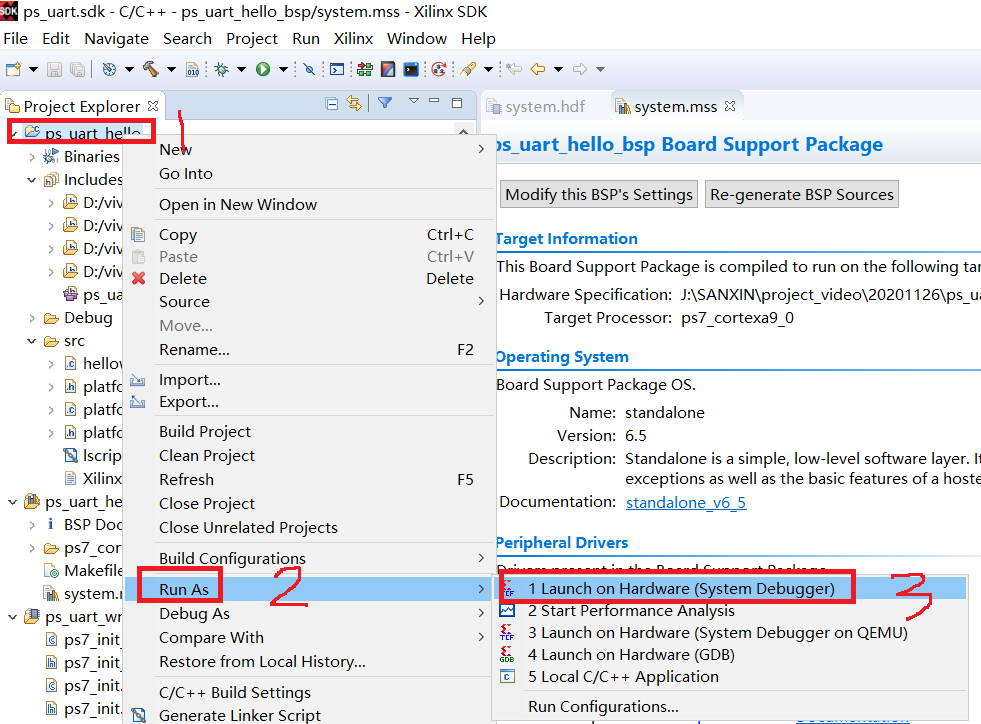

12、选择“ps_uart_hello”,右键“Run as”,选择第一个“Launch on Hardware(SystemDebuger)”,使用系统调试,直接运行程序。

13、可以看到串口没有任何输出

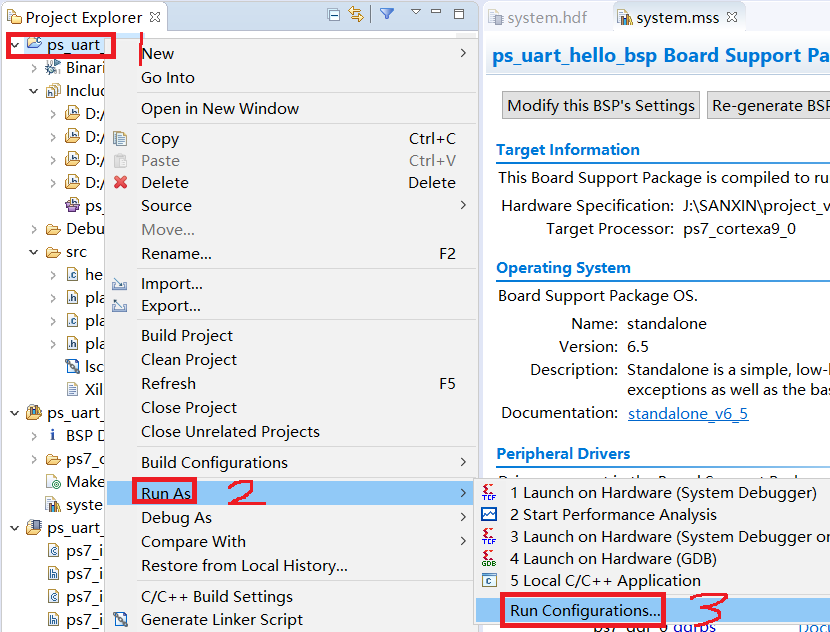

14、为了保证系统的可靠调试,需要添加一个配置,右键“Run As -> Run Configuration...”

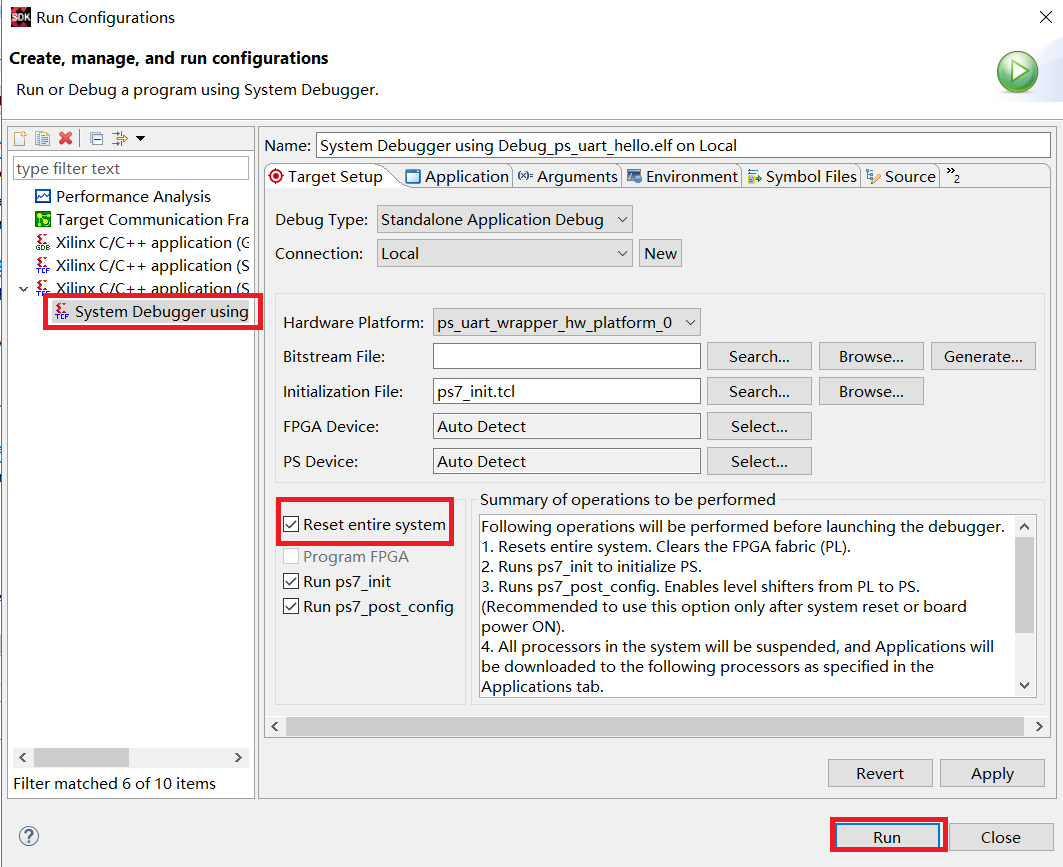

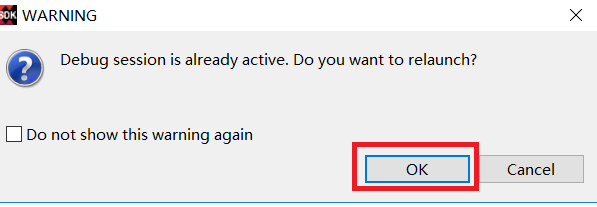

15、选择“Reset entire system”复位整个系统,如果系统中还有PL设计,还必须选择“ProgramFPGA”,再次点击“Run”

16、点击“OK”,确认重新运行

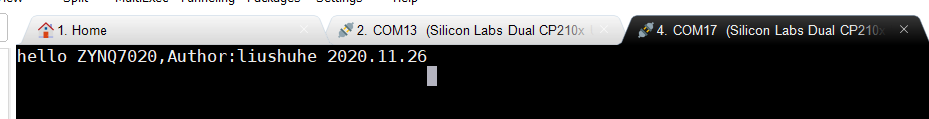

17、这次就可以看到熟悉《hello ZYNQ7020,Author:liushuhe 2020.11.26》显示出来了

三、Debug调试

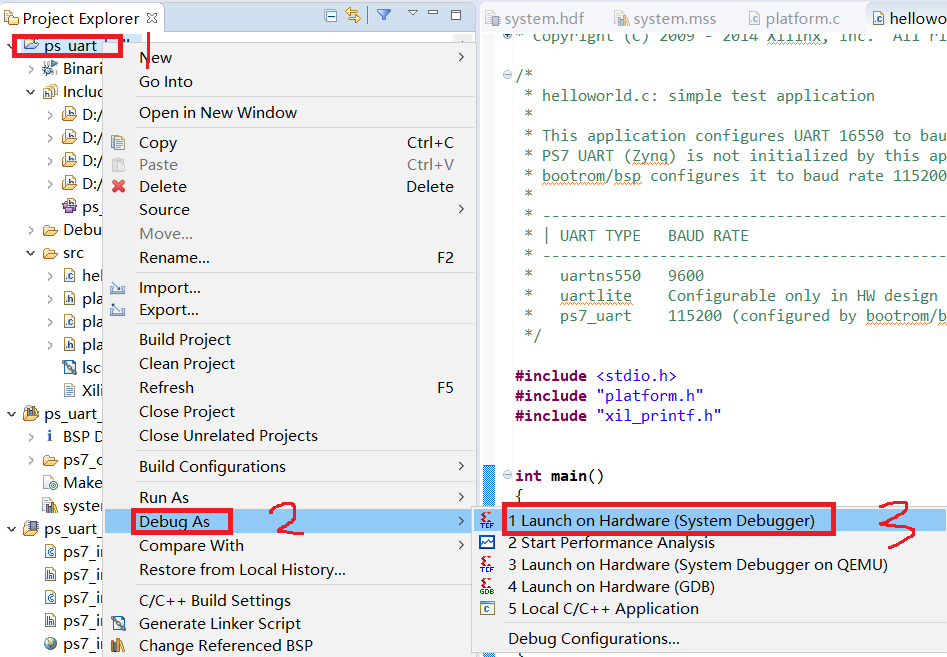

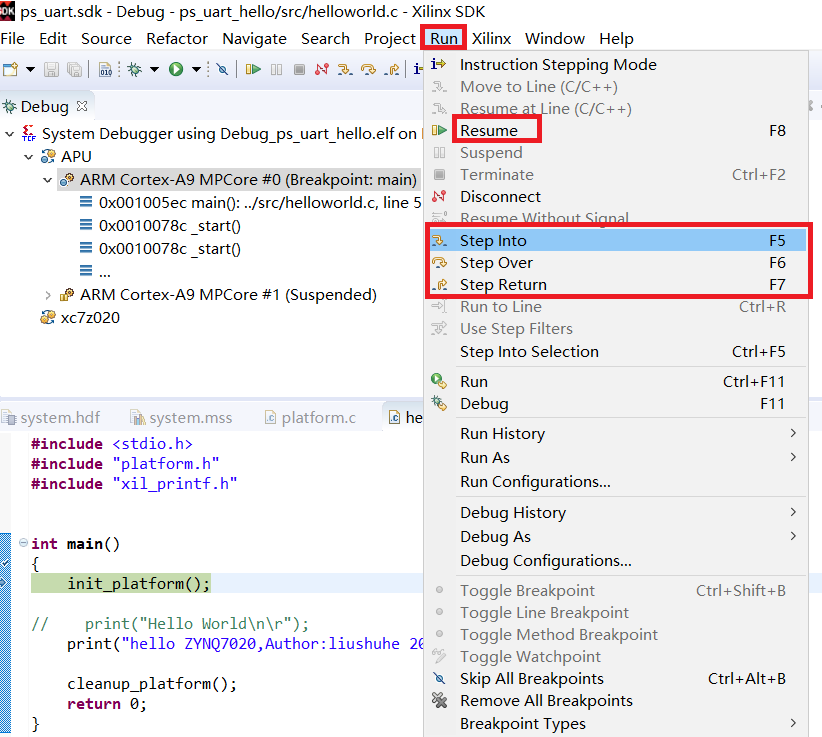

1、除了“Run As”,还可以“Debug As”,这样可以设置断点,单步运行

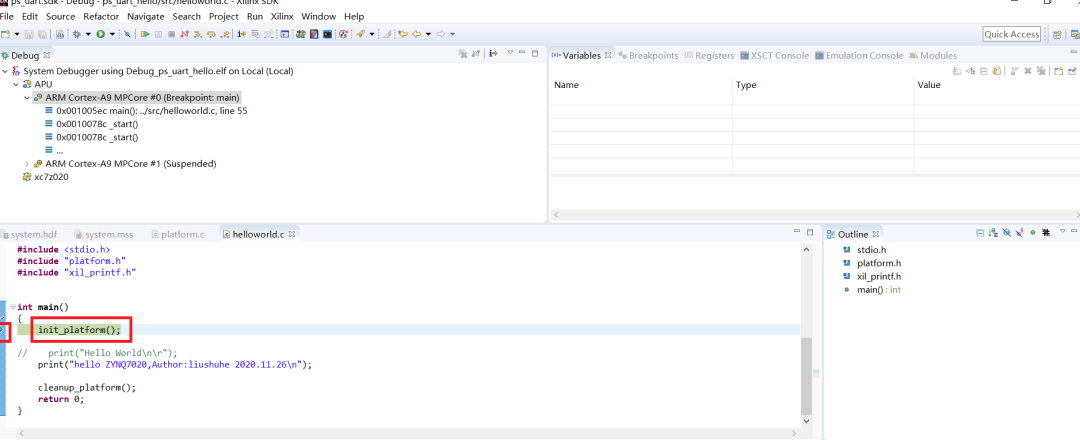

2、进入Debug模式 ,程序会自动运行到main函数处

3、和其他开发工具一样,我们也可以逐步运行、设置断点

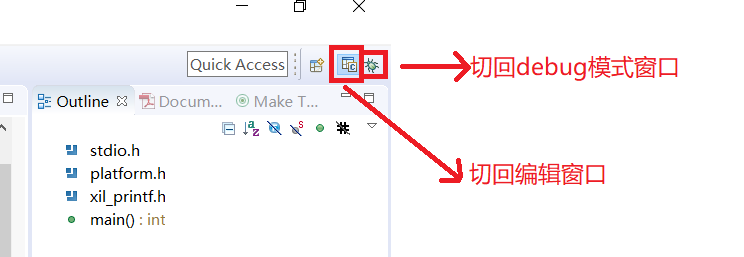

4、窗口右上角,有2个按钮可以方便我们在debug和编辑模式之间进行切换

四、到此,关于ZYNQ7020 的PS端基本开发流程,全部跑通,关于PS-PL的联合实验,待我另写一篇。

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22283浏览量

630286 -

Xilinx

+关注

关注

73文章

2192浏览量

129929 -

C语言

+关注

关注

183文章

7642浏览量

144612 -

uart

+关注

关注

22文章

1304浏览量

106112 -

串口打印

+关注

关注

0文章

11浏览量

3312

原文标题:笔记连载精选 |【xilinx ZYNQ7000系列之《PS端 》串口打印】

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念

请问FX3的UART口和Xilinx ZYNQ7000的PS端的UART进行硬件连接需要TTL电平转换吗?

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

zynq7000 BSP无法在u-boot加载运行,为什么?

zynq7000 BSP无法在u-boot加载运行怎么解决?

dac3174与xilinx zynq7000系列连接,fpga的案例参考代码有没有?

分享黑金ZYNQ7000系列视频教程

Xilinx Zynq-7000特性参数

Xilinx Zynq-7000SOC的相关资料推荐

Zynq7000系列之芯片引脚功能综述

Zynq-7000 PS端IIC接口使用笔记

xilinx ZYNQ7000系列基本开发流程之PS端

xilinx ZYNQ7000系列基本开发流程之PS端

评论