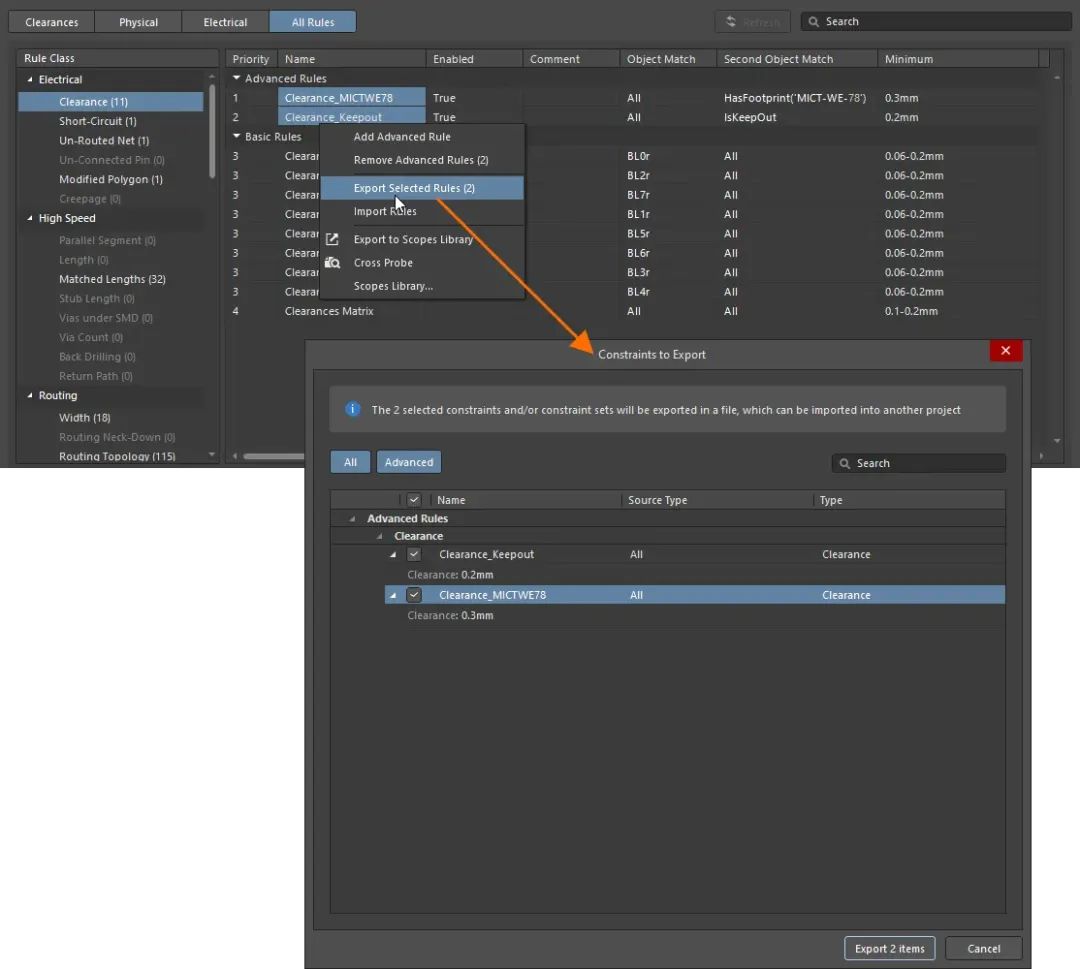

了解如何轻松快捷地在设计周期中随时完成一次性设计约束的导入,并且有信心自己的产品设计全程完全遵守这些约束。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4391文章

23741浏览量

420594 -

设计

+关注

关注

4文章

825浏览量

71152

发布评论请先 登录

相关推荐

热点推荐

蜂鸟e203移植fpga上如何修改约束文件

第一步:我们先导入官方网站中蜂鸟e203的代码提供的e203添加进去,并加入ddr200T中的

src.文件中的system.v文件并加入约束文件(constrs文件夹之中

发表于 10-24 07:18

EXCEL导入—设计与思考

EXCEL导入—设计与思考 一、案例信息与设计 1.1、案例需求与背景 B2BTC同城二期有一个Excel导入的功能,单次数据量小于一千,使用频次不高。但涉及到多个字段组成唯一约束,即每条数据操作

技术资讯 I 图文详解约束管理器-差分对规则约束

本文要点你是否经常在Layout设计中抓瞎,拿着板子无从下手,拿着鼠标深夜狂按;DDR等长没做好导致系统不稳定,PCIe没设相位容差造成链路训练失败……这些都是血泪教训,关键时刻需要靠约束管理器救命

AD、Allegro、Pads的快捷键有什么不同

在高速迭代的电子设计领域,快捷键是工程师与EDA工具对话的核心语言,纵观EDA工具,AD的视觉化交互、Allegro的深度可编程性、Pads的无膜命令——三种理念催生了截然不同的操作逻辑,那么它们的快捷键操作是否会有些不同?

KiCad 已支持导入 Altium 工程(Project)

“ 9.0.3 的小版本更新中增加一个非常实用的功能:直接导入 Altium 的工程,省去了分别导入原理图和 PCB 的麻烦。 ” Altium 导入器 从 8.0 开始,KiCad

Allegro Skill字符功能之导入LOGO

在完成PCB设计之后,常常会遇到需要在PCB板上展示公司标志或者导入设计中需要的logo图片的情况。为了满足这一需求,FanySkill特别提供了“导入LOGO”这一便捷功能。通过这个功能,用户可以轻松地将logo图片放置到PC

VirtualLab Fusion应用:振幅型SLM图片的导入

导入完成后,搭建光路模型,选择Stored Function元件作为SLM,双击打开Stored Function元件,将透过率函数文件加载到元件中:

9.运行场追迹查看调制结果如下:

发表于 06-03 08:49

PCB Layout 约束管理,助力优化设计

本文重点PCBlayout约束管理在设计中的重要性Layout约束有助避免一些设计问题设计中可以使用的不同约束在PCB设计规则和约束管理方面,许多设计师试图采用“一刀切”的方法,认为同

FPGA时序约束之设置时钟组

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径,使用set_false_path约束则会双向忽略时钟间的时序路径

AD软件快捷键设置和导入方法

这种只能一个命令一个更改,无法使用效率高点的批量更改。因此,学习的时候,专门制作了一个系统文件,直接将这个文件导入到AD内,就自动把快捷键设置成和Cadence、Pads一样了。

从下面发的附件里下载

发表于 03-26 10:03

如何在SonarWiz中导入和处理海底数据

本指南将向您介绍如何在 SonarWiz 中导入和处理海底数据。 通过本程序,您将学会如何 将侧视扫描数据导入 SonarWiz 平滑和内插导航 应用分层后退和滚轮偏移 应用增益,如 TVG

如何快捷地完成设计约束的导入

如何快捷地完成设计约束的导入

评论