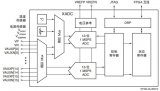

随着xilinx公司进入20nm工艺,以堆叠的方式在可编程领域一路高歌猛进,与其配套的EDA工具——新一代高端FPGA设计软件VIVADO也备受关注和饱受争议。我从2012年开始使用VIVADO,像所有刚推出的软件一样,在刚推出的时候都会存在一些bug,特别是VIVADO2013.2\2013.3。而最新的版本VIVADO2013.4在32位的电脑上也是经常出现运行缓慢、自动退出或挂起等现象,相信在后面的版本中这些问题会得到很好的解决。虽然存在一些bug但是它却阻挡不了VIVADO高效的设计以及良好的布局布线效果。下面我以我工作中碰到的一个工程为例来和大家分享一下VIVADO的高效设计带给我们的全新感受!我的工程是一个ADC数据采集的例子,LVDS总线,12根数据线,DDR模式。根据XILINX给出的xapp585,我将串并转换1:7的设计改成了串并转换1:4。依然使用了selectIO资源的ISERDES。原设计框图如下:[[wysiwyg_imageupload:1348:]]其中Calibration bitslip state machine和Deskew Control模块比较复杂并且使用了较多的算法,整个工程在ISE14.2中光综合过程就跑了将近5分钟左右,然后布局布线就更加的慢了。将近跑了7分钟半。后来我将整个工程移植到VIVADO2013.4中,其效率快的让我吃惊,总共加起来不超过5分钟。在使用VIVADO 的过程中有以下几个亮点,让我感觉效率确实提高不少。第一,当版本升级后,相应的IP版本也要升级,但是不要担心,VIVADO在检测到需要更新的IP后会提醒你更新,只要按着它的提示进行操作就可以将所有的IP一起更新,省去了很多麻烦。第二,调试时,直接从netlist通过mark debug添加NET到ILA中,然后VIVADO会将相应的约束自动添加到xdc文件中,最后通过VIVADO Logic Analyzer来查看波形。这种方法比之前的chipscope更加的高效![[wysiwyg_imageupload:1349:]]第三,掌握基本的几个Tcl命令,如get_cells/get_nets/get_pins/get_ports/get_clocks等,而且相对于ISE环境下的Tcl命令,这些命令都是全称加上下划线的,掌握这些命令可以编成脚本,大大的提高了设计效率。

使用VIVADO对7系列FPGA的高效设计心得

- FPGA(632043)

- 赛灵思(133241)

- Vivado(70638)

相关推荐

热点推荐

FPGA开发Vivado的仿真设计案例分析

仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 6234

6234

6234

6234

如何实现基于FPGA Vivado的74系列IP封装呢?

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 1405

1405

1405

1405

Xilinx 7系列FPGA的时钟结构解析

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 4432

4432

4432

4432

Vivado用于kintex7 FPGA显示找不到功能合成是什么原因?

嗨,我是FPGA的Vivado工具的初学者。我的FPGA是Kintex7系列的XC7K325T-2FFG900C。我安装了vivado,并且获得了我购买FPGA时获得的凭证。作为手册,我去了

2020-05-07 09:03:24

vivado约束参考文档

UG471 - 7 Series FPGAs SelectIOResources User Guide UG472 - 7 Series FPGAs ClockingResources User

2018-09-26 15:35:59

【Artix-7 50T FPGA申请】FPGA由Altera转Xilinx系列笔记

:1、Xilinx A7系列FPGA芯片与S6系列FPGA芯片的对比2、Vivado软件安装与介绍3、使用Vivado 编写Verilog代码进行开发数字逻辑开发和验证的全流程4、使用Vivado软件

2016-10-11 18:15:20

【Artix-7 50T FPGA试用体验】Artix-7 50T FPGA板卡文件安装与使用

感谢电子发烧友论坛给予这次试用机会,一直想试用一下Xilinx FPGA,苦于没有太多机会。这次就让我好好领略一下Xilinx最新7系列FPGA的高大上。首先介绍一下安装板卡文件的优势:1、板载资源

2016-11-28 15:15:16

【创龙TLZ7x-EasyEVM评估板试用连载】Vivado安装详情

命令语言(TcL)、Synopsys系统约束(SDC)以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。 Vivado目前只支持Xilinx的28nm工艺的7系列FPGA,包括

2020-05-31 10:20:03

在使用Vivado 2015.2过程中碰到的问题和心得体会,期待大牛关注指导!!!

本人Vivado小白一枚,项目开发需要,最近才买了一块z-turn板,芯片是XC7Z020。因为购买的IP核是使用vivado 2015.2生成的,所以我也必须使用2015.2。网上和各种论坛的资料

2016-01-22 09:47:18

基于 FPGA vivado 2017.2 的74系列IP封装

基于 FPGA vivado 2017.2 的74系列IP封装实验指导一、实验目的掌握封装IP的两种方式:GUI方式以及Tcl方式二、实验内容 本实验指导以74LS00 IP封装为例,介绍了两种封装

2017-12-20 10:23:11

基于FPGA Vivado的流水灯样例设计资料分享

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2022-02-07 08:02:04

请问7系列FPGA收发器向导v2.3 GTX名称不正确的原因?

你好我试图在KC705板上使用收发器来生成比特流。我正在使用Vivado 2012.3和7系列FPGA收发器向导v2.3。我之前使用过具有不同传输者名称的IBERT核心。IBERT收发器名称类似于

2020-07-28 10:29:31

购买NetFPGA SUME板后,我可以获得Vivado许可吗?

嗨,我发现Vivado webpack版本v2014.4不支持安装在NetFPGA SUME板上的eh Virtex-7 690 FPGA。我想知道购买NetFPGA SUME板的任何许可证捆绑

2018-12-18 10:36:47

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

MYC-J7A100T核心板及开发板Xilinx Artix-7系列XC7A100T开发平台,FPGA工业芯XC7A100T-2FGG484I具有高度的可编程性和灵活性;高速传输和处理,具有285个

2024-05-31 15:28:07

赛灵思客户共贺Vivado 设计套件推出

赛灵思推出的 Vivado 设计套件和 Virtex-7 FPGA,使 EVE 等标准 FPGA 仿真供应商在产品性能和功能方面全面超越定制 ASIC 仿真供应商

2012-04-25 09:10:14 1963

1963

1963

1963赛灵思Kintex-7 FPGA 系列芯片简介

电子发烧友网: 本文主要介绍了赛灵思Kintex-7 FPGA 系列芯片的性能。 业界最佳性价比 Kintex-7 FPGA 是一款新型的 FPGA,展现高端性能,成本降低过半。Kintex-7 系列是在通用 28nm 架构基础

2012-06-12 10:14:18 17125

17125

17125

17125

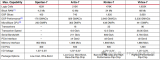

xilinx公司的7系列FPGA应用指南

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201

201

201使用Vivado高层次综合 (HLS)进行FPGA设计的简介

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65

65

65FPGA从Xilinx的7系列学起(5)

RAM实现的。所有7系列的FPGA都具有相同架构的BlockRAM,每一块BlockRAM是36KB大小的真正的双端口存储器,

2017-02-08 10:19:33 374

374

374

374Vivado高效设计案例分享

首先,在这个页面上啰嗦几句。左侧列出了软件不同的版本号,大家根据自己的需要选择相应的版本。中间这一列就是我们需要下载的软件安装包了。目前,Vivado支持windows和linux操作系统。大家可以

2018-07-12 15:21:00 4142

4142

4142

4142

高效、低成本的 FPGA 器件:Spartan-7 FPGA!

赛灵思 Spartan®-7 系列提供了一系列高效、低成本的 FPGA 器件。这些器件经过专门设计,能满足低成本市场的特殊需求。 摘要 Spartan®-7 FPGA 将高性能 28nm 可编程

2017-11-16 15:15:54 10279

10279

10279

10279

用Xilinx Vivado HLS可以快速、高效地实现QRD矩阵分解

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 4363

4363

4363

4363

基于FPGA的Vivado功耗估计和优化

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 7860

7860

7860

7860赛灵思全新7系列FPGA

本视频为您带来赛灵思最新7系列FPGA产品的精彩展示,高性能、低功耗,统一架构实现的可扩展性等将为FPGA产品的应用提供更广阔的空间。

2018-06-06 03:45:00 5542

5542

5542

5542赛灵思推出Spartan-7 FPGA系列密集型器件,能够快速集成和实现

赛灵思公司为成本敏感型应用推出灵活的 I/O 密集型器件——Spartan-7 FPGA系列。该新型系列器件可满足汽车、消费类电子、工业物联网、数据中心、有线/无线通信和便携式医疗解决方案等多种

2018-08-20 10:48:00 1968

1968

1968

1968Xilinx Vivado软件ILA使用心得

Vivado在使用A7芯片时,使用内部逻辑分析仪时,在非AXI总线下最多只能绑定64组信号(例化一个或者多个ILA模块,信号组数相加不能超过64),如果超过64组会出现错误。

2018-11-23 09:38:55 2045

2045

2045

20457 FPGA VC707评估方案

关键词:FPGA , VC707 , Virtex-7 , Xilinx Xilinx公司的7系列FPGA产品包括Artix-7系列, Kintex-7系列和Virtexreg;-7系列,具有低成本

2019-02-11 11:26:02 2524

2524

2524

2524

Xilinx 7系列FPGA的数据手册详细资料概述

Xilinx 7系列FPGA包括四个可满足全系列系统需求的FPGA系列,从低成本、小尺寸、成本敏感、大容量应用到超高端连接带宽、逻辑容量和信号处理能力,满足最苛刻的高性能应用。7系列FPGA包括:

2019-02-25 16:43:37 81

81

81

81Verilog HDL语言及VIVADO的应用

中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 4201

4201

4201

4201

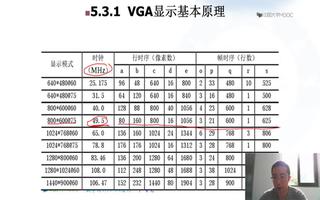

数字设计FPGA应用:VGA显示的基本原理分析

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:09:00 2882

2882

2882

2882

数字设计FPGA应用:时序逻辑电路FPGA的实现

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 3476

3476

3476

3476

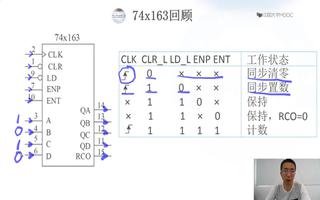

数字设计FPGA应用:74x163回顾

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:07:00 3952

3952

3952

3952

数字设计FPGA应用:硬件描述语言与VIVADO

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:06:00 2845

2845

2845

2845

数字设计FPGA应用:FPGA的基本实践

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:05:00 3652

3652

3652

3652

数字设计FPGA应用:7系列FPGA及7a35tftg256-1特性

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:04:00 6368

6368

6368

6368数字设计FPGA应用:按键扫描设计

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:03:00 2081

2081

2081

2081

数字设计FPGA应用:矩阵式按键的设计

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:02:00 2081

2081

2081

2081

数字设计FPGA应用:LED流水灯的程序编写

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:01:00 2649

2649

2649

2649

数字设计FPGA应用:实现LED小灯功能

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-04 07:01:00 2649

2649

2649

2649

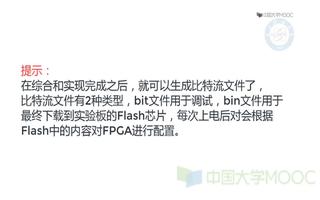

数字设计FPGA应用:数据类型及变量、常量

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:10:00 2553

2553

2553

2553

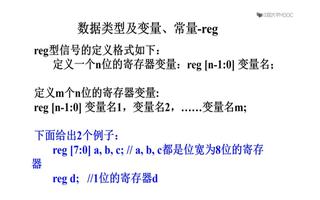

数字设计FPGA应用:循环语句for

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:08:00 3537

3537

3537

3537

数字设计FPGA应用:7系列FPGA xc7a35t

Xilinx Artix®-7 FPGA系列是一款高性价比FPGA, 提供高性能/功耗比, 高收发器线路速率, DSP处理, 集成AMS.

2019-12-03 07:07:00 12963

12963

12963

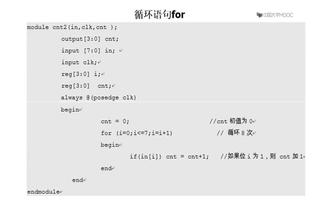

12963数字设计FPGA应用:阻塞与非阻塞

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:06:00 2289

2289

2289

2289

数字设计FPGA应用:编译软件的安装与使用

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:05:00 2360

2360

2360

2360

数字设计FPGA应用:FPGA的基本逻辑结构

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 3009

3009

3009

3009

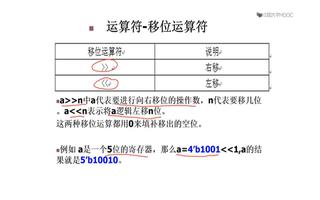

数字设计FPGA应用:移位运算符

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:03:00 3750

3750

3750

3750

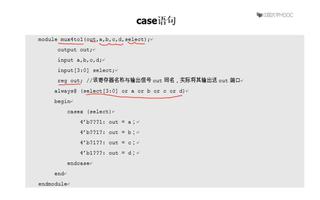

数字设计FPGA应用:case语句

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:02:00 5937

5937

5937

5937

数字设计FPGA应用:Verilog HDL语言基本结构

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-02 07:10:00 3646

3646

3646

3646

数字设计FPGA应用:FPGA概述

中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:00:00 2818

2818

2818

2818

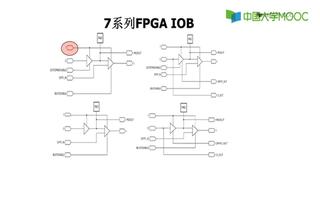

数字设计FPGA应用:7系列FPGA IOB

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-02 07:09:00 4453

4453

4453

4453

极客对Xilinx Vivado HLS工具使用经验和心得

介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 5460

5460

5460

5460digilent Artix-7 FPGA训练板介绍

Basys 3是一款可由Vivado®工具链支持的入门级FPGA开发板,带有Xilinx® Artix®-7 FPGA芯片架构。该款产品是广受欢迎的Basys系列FPGA开发板中最新的一代,特别适合

2019-11-20 15:24:44 3070

3070

3070

3070

基于Project模式Vivado GUI使用的配置文件自动化生成管理

BY 卢昊 曾就职于上海贝尔(阿尔卡特朗讯),任FPGA工程师。目前从事FPGA加速计算方面的工作。有多年使用FPGA开发和应用的经历,熟悉Xilinx FPGA的体系结构。 Vivado相比

2020-11-13 12:48:53 4267

4267

4267

4267

FPGA设计中Tcl在Vivado中的基础应用

Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 3306

3306

3306

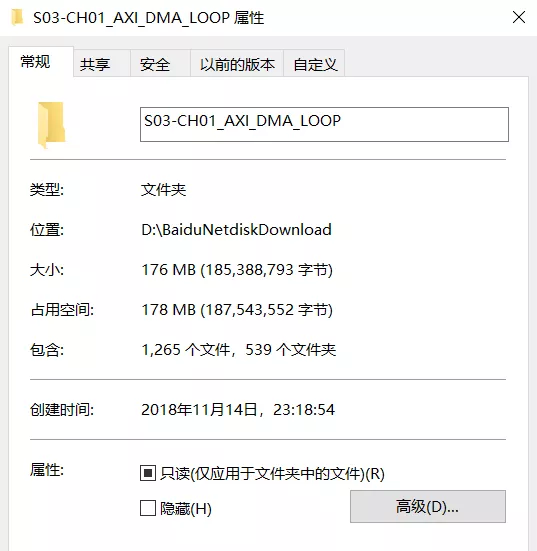

3306使用vivado的过程如何清理/压缩不必要的文件

作者:材哥,玩儿转FPGA 前言 vivado和ISE的使用差别很大,Vivado是专门针对7系列和以后系列的FPGA/AP SOC进行高效设计的工具,特别是最近提出的UltraFast设计方法

2020-12-25 14:53:36 11506

11506

11506

11506

FPGA实现基于Vivado的BRAM IP核的使用

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270

13270

13270Xilinx 7系列FPGA介绍

Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 16550

16550

16550

16550Xilinx 7系列FPGA选择资源的技术参考指南

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 25

25

25

25Xilinx 7系列FPGA可配置逻辑块的用户指南

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达?7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 6

6

6

6Xilinx 7系列FPGA内存资源的用户指南

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 15:31:13 10

10

10

10Xilinx 7系列FPGA时钟资源

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18

18

18Xilinx7系列FPGA选择资源用户指南

Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 15:27:48 24

24

24

24Xilinx 7系列FPGA简介--选型参考

Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列

2021-01-30 06:00:11 21

21

21

21Xilinx 7系列四类FPGA介绍说明

Xilinx 7系列FPGA由四类FPGA系列组成,解决了从低成本、小尺寸、成本敏感、高容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力等完整的系统需求。 首先我们先看

2021-03-09 11:44:22 8099

8099

8099

8099Xilinx 7系列FPGA时钟和前几代有什么差异?

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 6070

6070

6070

6070Xilinx 7系列FPGA管脚是如何定义的?

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 11807

11807

11807

11807

Xilinx 7系列FPGA管脚是如何定义与Pinout文件下载

我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。

2021-04-27 10:45:29 9045

9045

9045

9045

xilinx 7系列FPGA之电源简介

博主的微信公众号:FPGA动力联盟博主的个人微信:fpga_start前几篇咱们说了FPGA内部逻辑,本篇咱们再聊一聊7系列FPGA的供电部分。首先咱们说spartan7系列,通常咱们需要使用以

2021-11-06 19:51:00 20

20

20

20【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 27

27

27

27XILINX可编程逻辑®7系列FPGA

XILINX是可编程逻辑芯片,由多个系列的性能可以满足一般的逻辑设计要求,如赛灵思7系列,Xilinx®7系列FPGA由四个FPGA系列组成 7A 7V 7S 7K,可满足各种系统要求,从低

2022-11-03 14:39:54 3344

3344

3344

3344Xilinx FPGA Vivado开发流程介绍

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado开发软件开发设计流程。话不多说,上货。

2023-02-21 09:16:44 5063

5063

5063

5063在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0

0

0Xilinx 7系列与Ultrascale系列FPGA的区别

Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 9018

9018

9018

9018

Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

员和系统架构师需要探索更为高效的全新工作方式。 AMD Vivado 设计套件 可提供易于使用的开发环境和强大的工具,有助于 加速大型自适应 SoC 和FPGA等系列产品的设计与上市 。 现在,我

2023-11-02 08:10:02 2397

2397

2397

2397AMD Vivado Design Suite 2023.2的优势

由于市场环境日益复杂、产品竞争日趋激烈,为了加快推出新型自适应 SoC 和 FPGA 设计,硬件设计人员和系统架构师需要探索更为高效的全新工作方式。AMD Vivado Design Suite

2023-11-23 15:09:24 1758

1758

1758

1758简述Xilinx 7系列FPGA芯片相关知识

Xilinx 7系列 芯片 应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx( AMD )已延长该系列芯片的生命周期至少到2035年。 本文主要介绍Xilinx 7系列 FPGA

2023-11-28 10:20:02 2842

2842

2842

2842

FPGA实现基于Vivado的BRAM IP核的使用

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291

3291

3291Xilinx 7系列FPGA功能特性介绍

Xilinx7系列FPGA由四个FPGA系列组成,可满足一系列系统需求,从低成本、小尺寸、成本敏感的大容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力。

2024-04-22 10:49:49 9207

9207

9207

9207

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45:10 4694

4694

4694

4694

电子发烧友App

电子发烧友App

评论