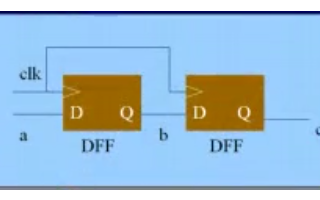

阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看,被赋值对象会比赋值对象差一个时钟周期。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22283浏览量

630292 -

时序

+关注

关注

5文章

402浏览量

38627

发布评论请先 登录

相关推荐

热点推荐

Verilog语言中阻塞和非阻塞赋值的不同

来源:《Verilog数字系统设计(夏宇闻)》 阻塞和非阻塞赋值的语言结构是Verilog 语言中最难理解概念之一。甚至有些很有经验的Verilog 设计工程师也不能完全正确地理解:何

在testbench中如何使用阻塞赋值和非阻塞赋值

本文详细阐述了在一个testbench中,应该如何使用阻塞赋值与非阻塞赋值。首先说结论,建议在testbench中,对时钟信号(包括分频时钟)使用阻塞赋值,对其他同步信号使用

verilog中阻塞赋值和非阻塞赋值

阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。

发表于 03-15 10:57

•7216次阅读

FPGA学习系列:5.阻塞赋值与非阻塞赋值

设计背景: 阻塞 (=)和非阻塞(=)一直是在我们FPGA中讨论的问题,资深的学者都是讨论的是赋值应该发生在上升下降沿还是在哪里,我们在仿真中看的可能是上升下降是准确的,但是在时间电路

FPGA的视频教程之Verilog中阻塞与非阻塞的详细资料说明

本文档的主要内容详细介绍的是FPGA的视频教程之Verilog中阻塞与非阻塞的详细资料说明。

发表于 03-26 17:16

•2次下载

简述Verilog HDL中阻塞语句和非阻塞语句的区别

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。 Verilog语言中讲的阻塞

阻塞与非阻塞通信的区别 阻塞和非阻塞应用场景

阻塞通信(Blocking Communication):当进行阻塞通信时,调用者在发起一个I/O操作后会被阻塞,直到该操作完成返回才能继续执行后续代码。

socket阻塞和非阻塞的区别是什么

在计算机编程中,socket 是一种通信端点,用于在网络中进行数据传输。Socket 可以是阻塞的或非阻塞的,这两种模式在处理数据传输时有不同的行为。 阻塞模式(Blocking Mo

数字设计FPGA应用:阻塞与非阻塞

数字设计FPGA应用:阻塞与非阻塞

评论