JEDEC 固态技术协会,微电子产业标准全球领导制定机构,今天宣布正式发布JEDEC DDR3L规范。这是广受期待的DDR3存储器标准JESD79-3 的附件。这是DDR3作为当今DRAM主导性标准演变的继续

2010-08-05 09:10:50 4183

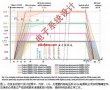

4183 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB设计。

2014-07-24 11:11:21 6350

6350

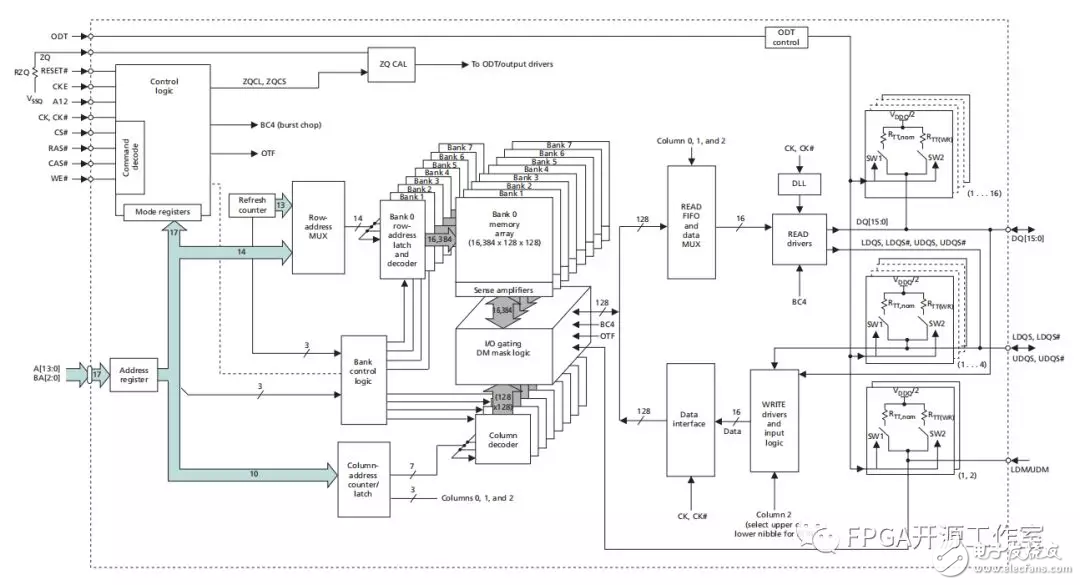

本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。##每片

2015-04-07 15:52:10 13985

13985

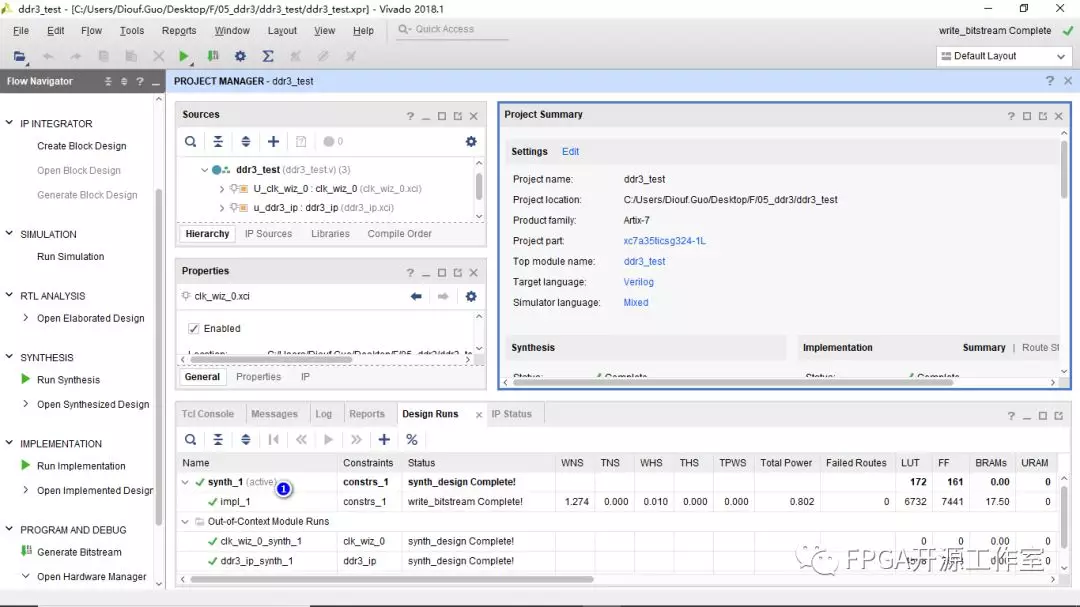

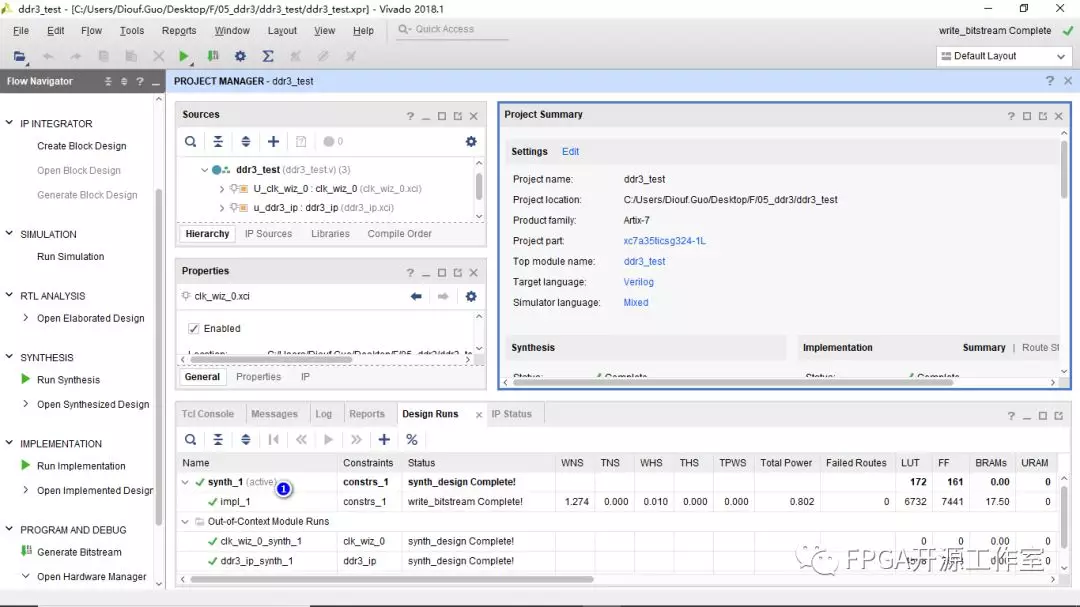

将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA

2020-12-15 16:45:16 3617

3617

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2020-12-16 15:47:59 2622

2622

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2021-01-01 10:09:00 5267

5267

为了更好地管理各类DDR3内存的特性,并提供一种简便的、带宽效率高的自动化方式来初始化和使用内存,我们需要一款高效DDR3内存控制器。

2021-02-09 10:08:00 14491

14491

本实验为后续使用DDR3内存的实验做铺垫,通过循环读写DDR3内存,了解其工作原理和DDR3控制器的写法,由于DDR3控制复杂,控制器的编写难度高,这里笔者介绍采用第三方的DDR3 IP控制器情况下的应用,是后续音频、视频等需要用到DDR3实验的基础。

2021-02-05 13:27:00 10988

10988

2022年4月20日,中国苏州讯 —— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。 华邦的 1.35V DDR3 产品在 x8

2022-04-20 16:04:03 3594

3594

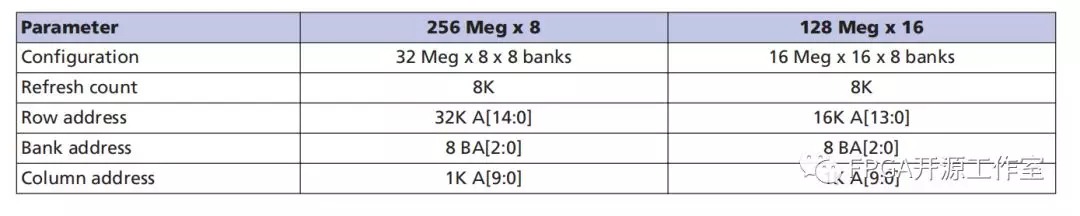

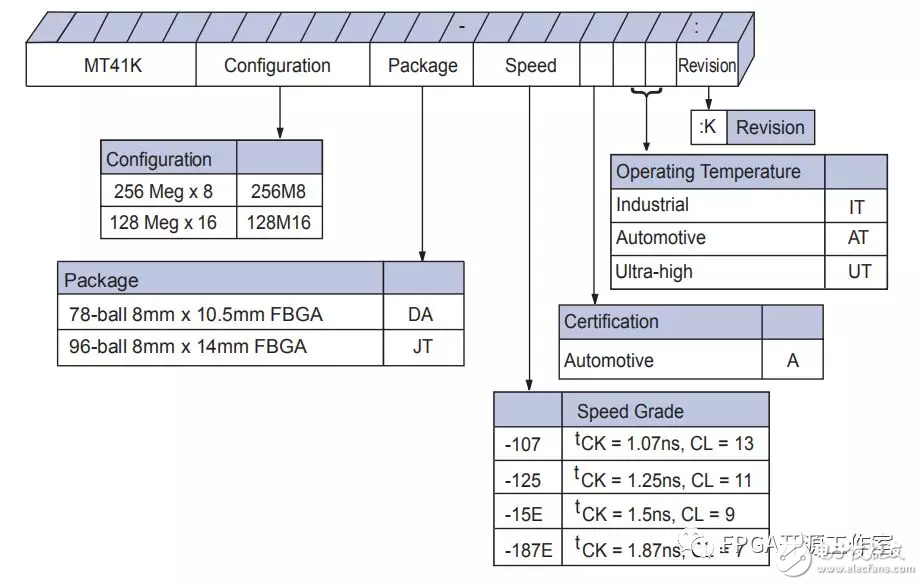

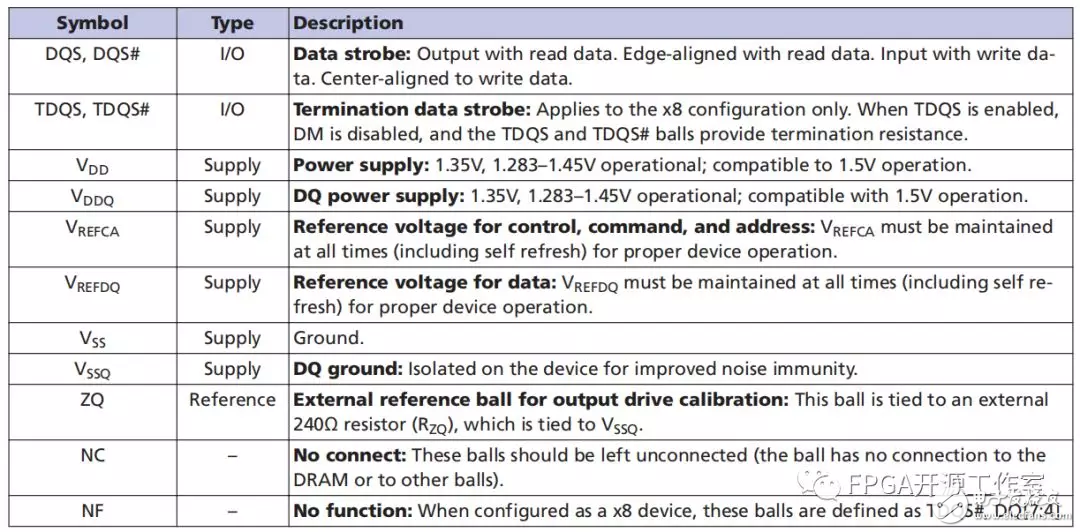

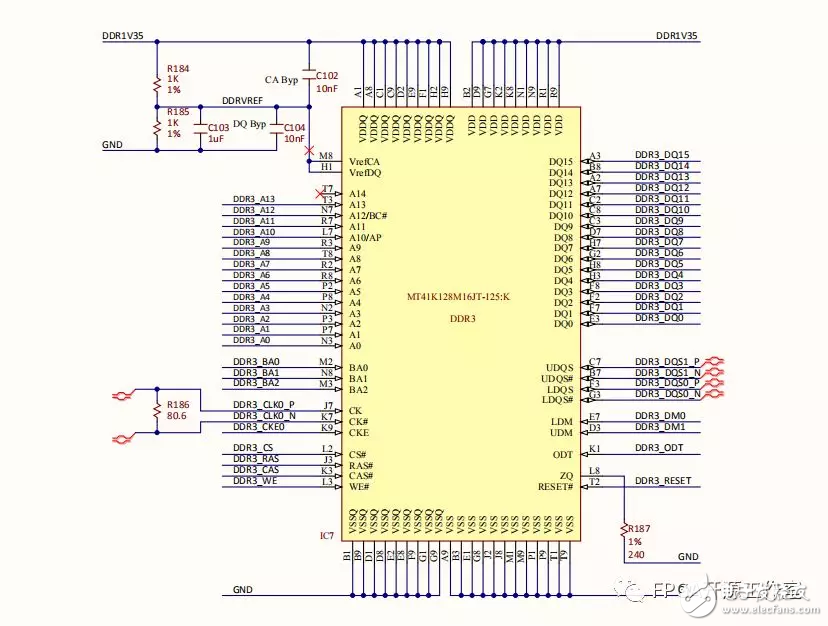

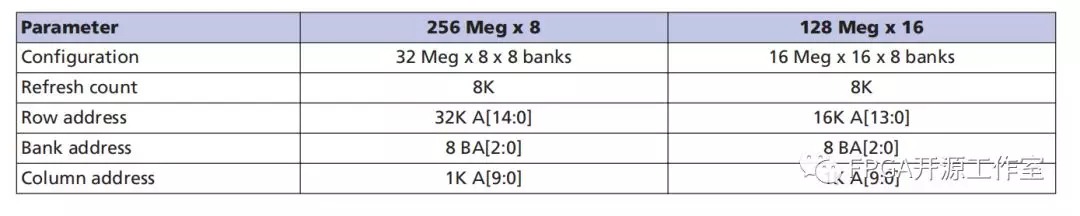

以MT41J128M型号为举例:128Mbit=16Mbit*8banks 该DDR是个8bit的DDR3,每个bank的大小为16Mbit,一共有8个bank。

2023-09-15 15:30:09 3825

3825

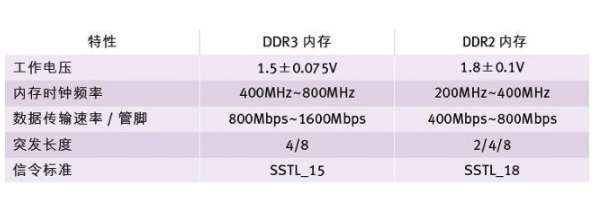

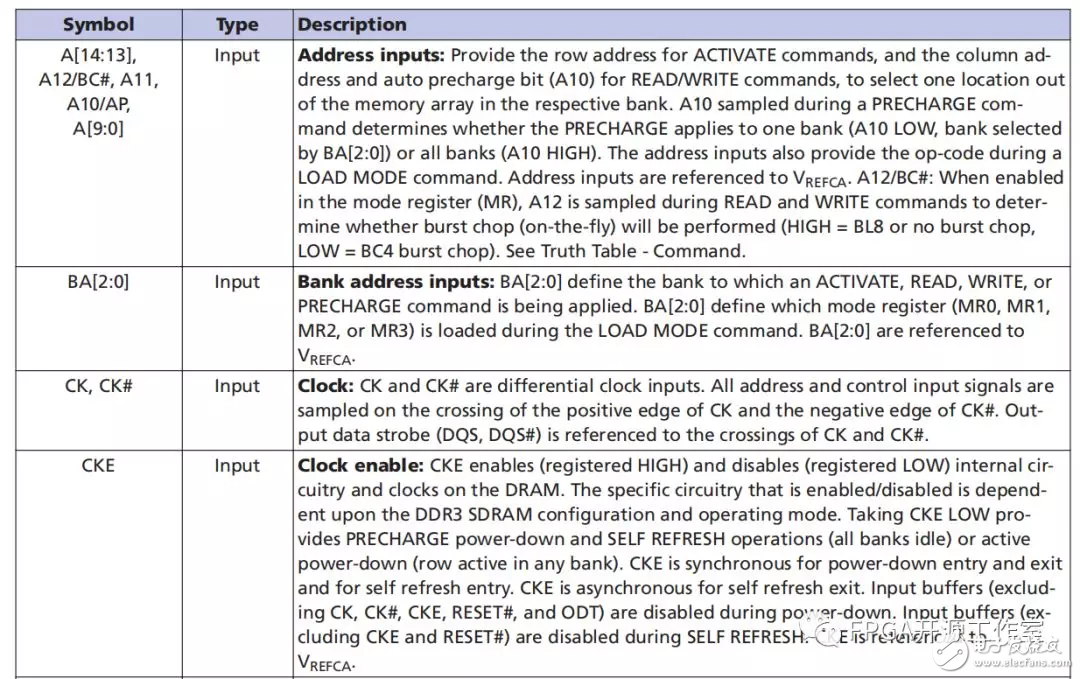

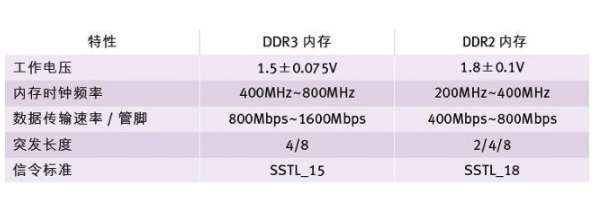

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3931

3931

下面是调用的DDR3模块的,模块的倒数第二行是,模块的时钟输入,时钟源来自PLL产生的系统时钟的倍频。

2025-05-03 10:21:00 1339

1339

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

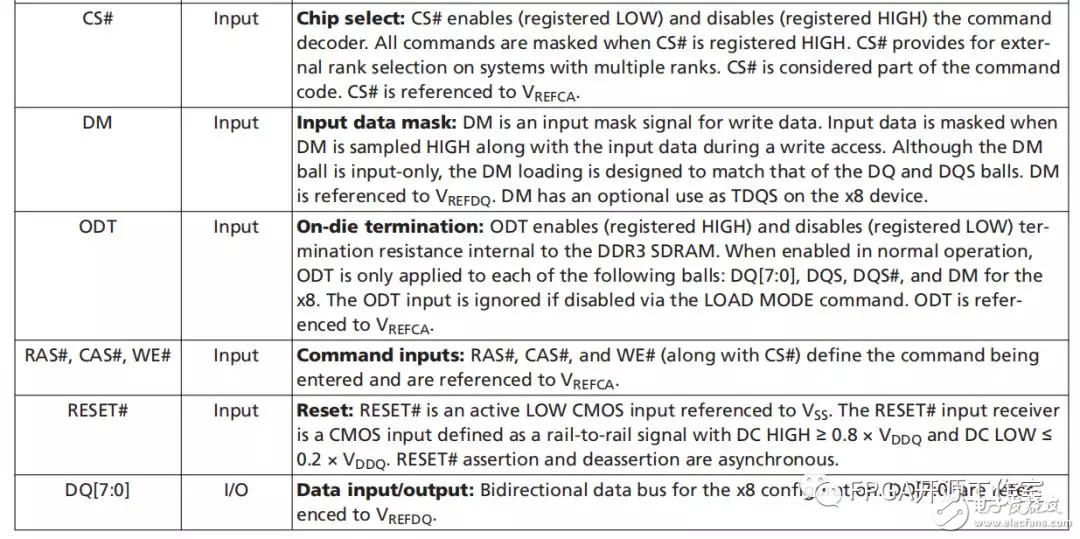

为了实现更强大的系统操作,DDR3 SDRAM驱动器设计通过降低电容得到了增强,动态片上端接(ODT)和新的校准方案。电容减少来自于使用新的合并驱动器。使用新驱动程序,组成输出驱动程序的电路共享用于ODT。DDR2上使用单独的结构作为输出驱动器和终端阻抗。

2019-05-23 08:20:56

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

最近阿威也在玩MIG ,然后对我问了一大堆问题,主要针对MIG的时钟。后来发现自己理解得还是不够。这么一讨论更加清晰了,做个笔记吧。第一个时钟,也就是MIG 对DDR接口的时钟。因为我用的是ddr3

2019-05-21 07:21:10

你好,ISE版本为13.3,modelsim版本为10.1c 64bit.MIG工具为ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

”。13.点击“Generate”生成MIG控制器。四、生成文档点击“Generate”,生成MIG控制器相关的设计文档。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置过程。

2019-12-19 14:36:01

IP并完成连线。3.按照下图对IP进行相应的配置。Axi Datamover 配置:mig_7_series配置:打开该IP后点击NEXT进入配置界面:选择型号之后点击NEXT,选择DDR3

2021-07-30 11:23:45

MT41J25616XX用于DDR3芯片。当我们使用MIG工具配置DDR3时,对于我们的FPGA,此DDR3组件未显示在支持的DDR3组件列表中。如果我们使用“创建自定义部件”添加我们的芯片,那么

2019-02-18 09:01:37

我可以使用mig生成ddr控制器(xc6vlx130t)吗?mig向导只支持ddr2和ddr3!

2020-06-12 07:32:48

用DDR3获得更好的性能,DDR3的可用性可能不如DDR2,但我不想在部件选择中出错并选择一个已知的部件,并得到MIG发电机的支持在ISE。最好的祝福,埃尔维斯·道森以上来自于谷歌翻译以下为原文Hi, I

2019-05-21 06:16:43

IP DDR3控制器 RISC-V

基于DDR200T开发板原理图,找到所需要使用的DDR引脚,制成DDR.ucf文件方便在添加管脚约束时使用。在使用MIG IP核时,为了方便使用DDR产生的时钟

2025-10-21 12:43:40

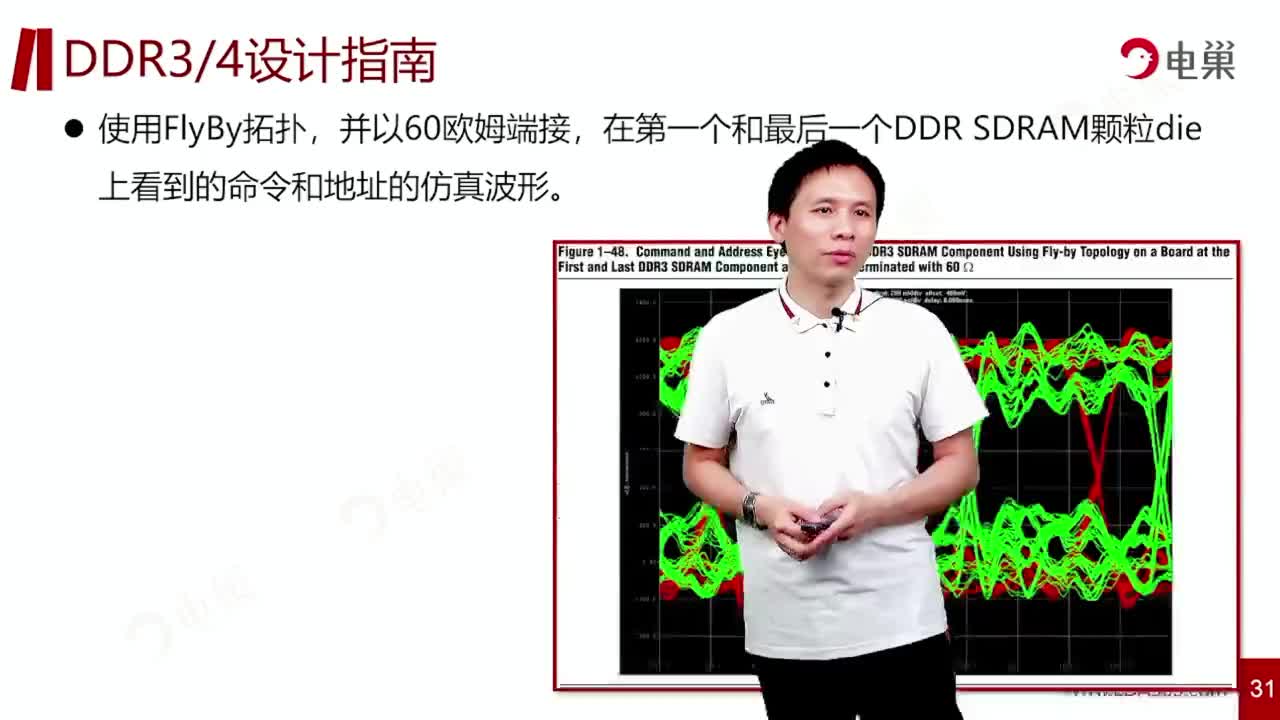

。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配技术对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM

2018-08-02 09:34:58

的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3读写操作。DDR3用户接口仲裁控制模块将中断请求分成多个子请求,实现视频中断和图形中断的并行

2024-06-26 18:13:42

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

亲爱的先生Vivado:v2016.4装置:Artix-7我尝试在Vivado中使用MIG设计DDR3 SODIMM接口。但是,MIG只生成一对ddr_ck。我认为DDR3 SODIMM需要2对ddr_ck,如ddr_ck0和ddr_ck1。我该如何生成2对ddr_ck?谢谢。

2020-08-24 06:45:17

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

我正在使用vivado 2014.3,MIG 7 ddr3 verilog IP,内存时钟400MHz,用户时钟200 MHz,ddr数据宽度64位,AXI数据宽度128位。在我的系统中,我们有微型

2020-08-05 13:45:44

大家好 我的问题是DDR3校准完成失败。调试结果:dbg_wrcal_err = 1,通过波形,我们可以看到写入模式不匹配。 我的问题是MIG IP Core配置中是否有任何参数可以调整它?或者我

2020-07-23 10:09:37

嗨,我正在尝试用我的设计生成带有MIG3.2的DDR3控制器,并修改example_design项目以适应我的电路板。在更改.ucf文件之前,实现成功。但在改变.ucfaccording我的设计后

2020-06-10 08:25:16

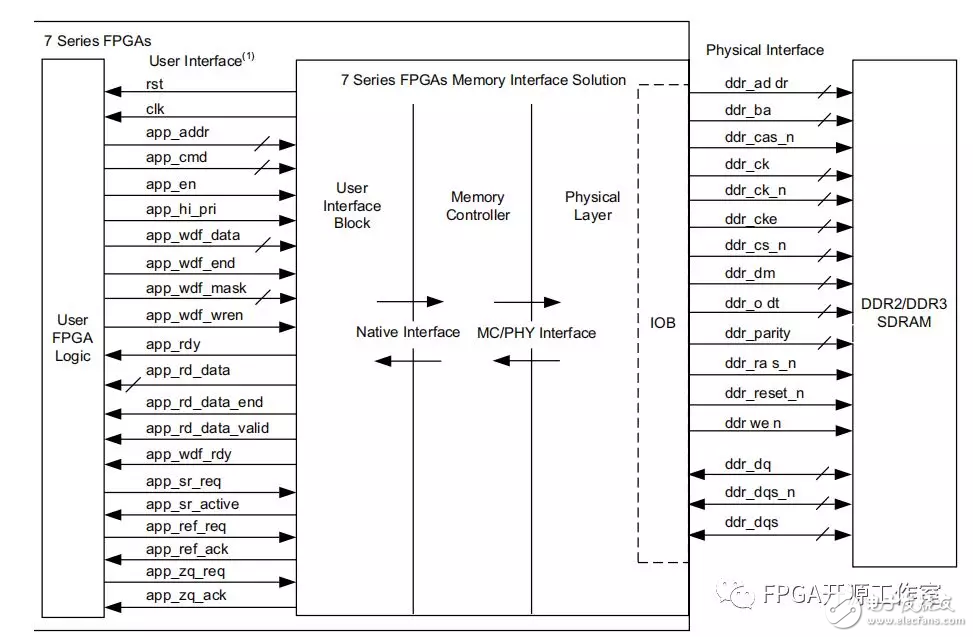

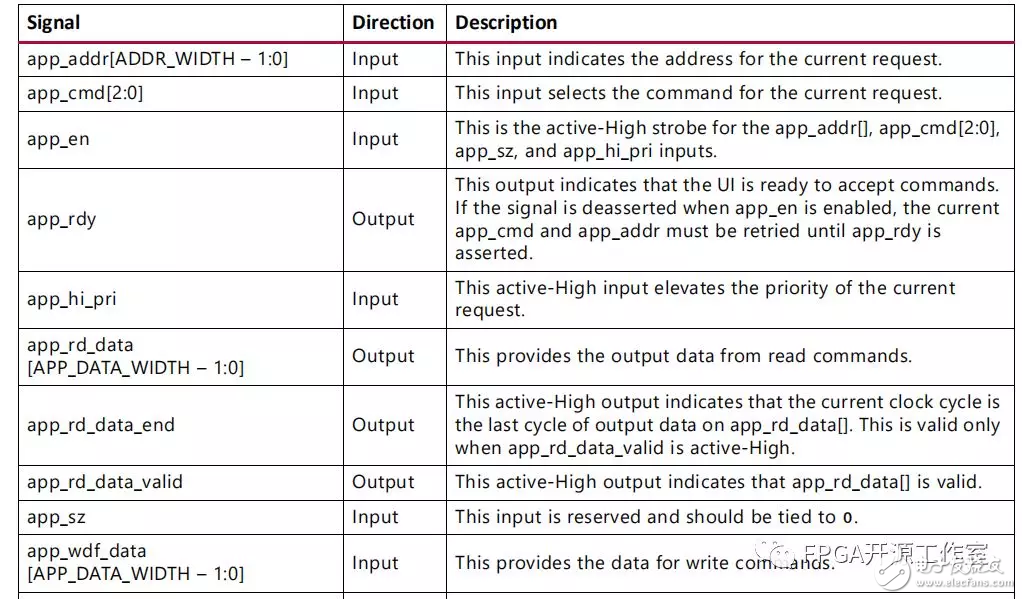

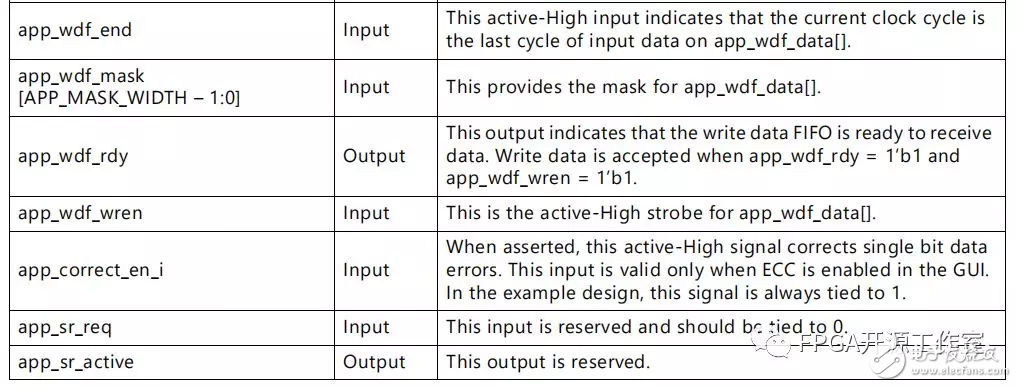

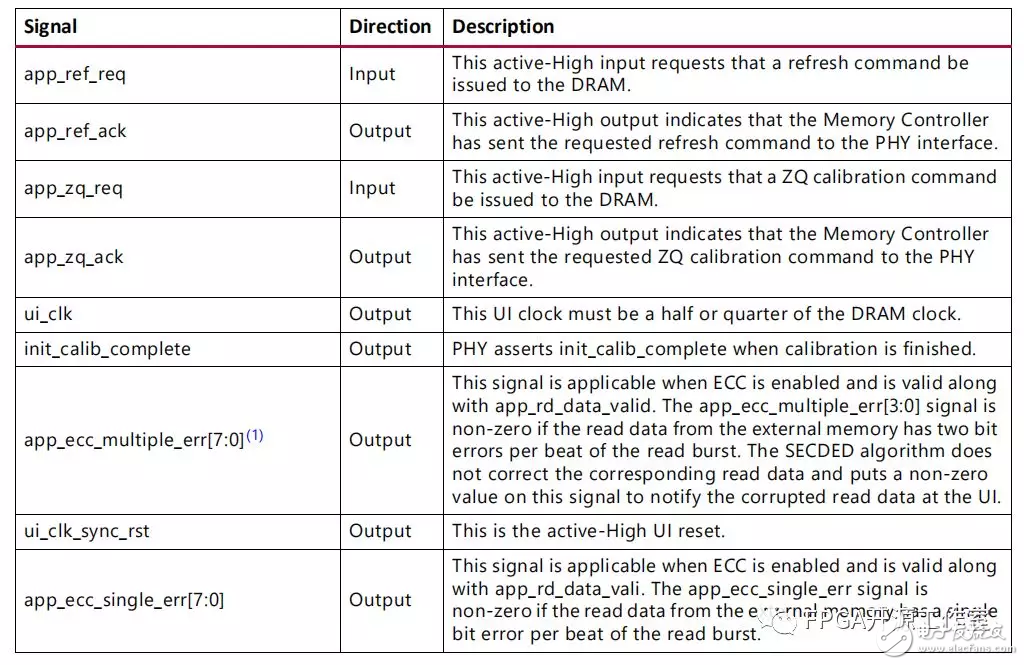

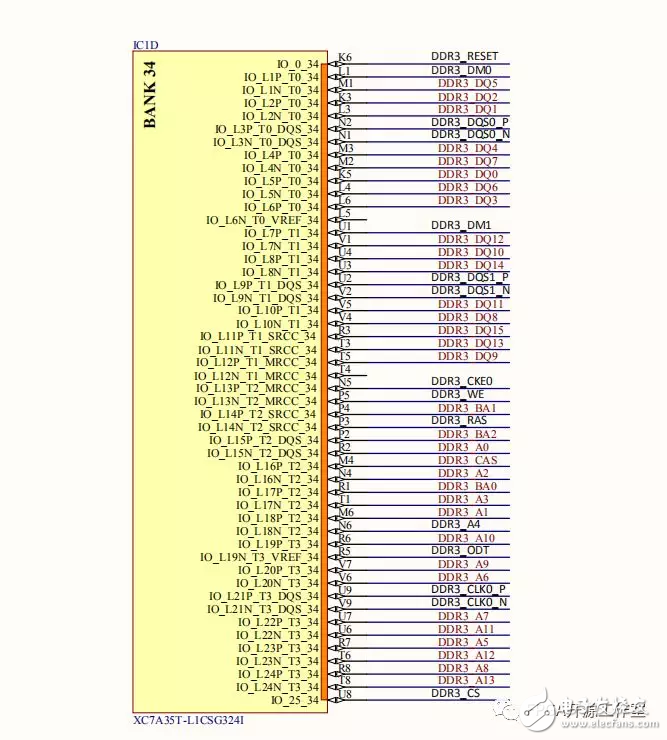

的控制流程。下图所示是7系列的MIG IP核结构图。MIG IP核对外分出了两组接口,左侧是用户接口,右侧是DDR物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

DDR3的读写都包含写

2025-10-21 08:43:39

我需要在V7中实现与DDR3 SDRAM相同的功能和接口。这意味着命令/地址,读取数据和写入数据流的方向与MIG的方向不同。这可以实现吗?

2020-07-14 16:18:04

喜 我需要支持ml605板的2G内存,我在用2G DDR3更换512M DDR3后遇到了一些问题..它没有用。我使用ise13.3我通过核心生成器生成mig,当我生成核心时,我应该做什么谢谢。

2020-06-14 14:59:33

/Trenz_Electronic/TE0630_series/TE0630/documents/UM-TE0630.pdf)在这个主板上有Nanya的DDR3内存(NT5CB64M16DP)。对于

2019-08-05 08:08:14

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

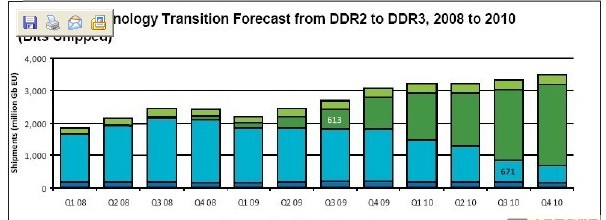

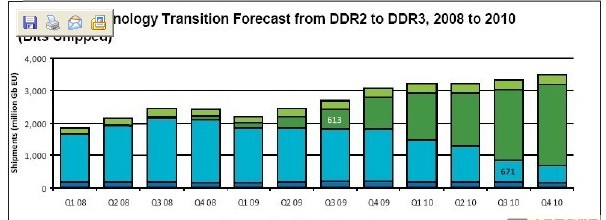

30 DDR3将是2010年最有前景市场

2009 年即将结束,DDR2 作为DRAM 市场之王的日子同样所剩无几。速度更快且功耗更低的DDR3 几年前就已经问世,iSuppli 公司认为,它即将成为世

2009-12-15 10:28:14 1003

1003

台湾DRAM厂商大举转产DDR3

2010年PC主流内存标准从DDR2向DDR3的转换正在逐步成为现实。据台湾媒体报道,由于下游厂商的DDR2订单量近期出现急剧下滑,多家台系DRAM芯片

2010-01-18 09:25:13 795

795 DDR2芯片价格有望在下半年超过DDR3

报道,威刚主席Simon Chen今天表示,随着DRAM制造商把重点放在DDR3芯片生产上,DDR2芯片的出货量将开始减少,其价格有望在今年下半

2010-02-05 09:56:18 1177

1177 金士顿:DDR2/DDR3价格可能会继续上涨

据报道,存储大厂金士顿亚太地区副总裁Scott Chen近日表示,虽然1Gb DDR2/DDR3的芯片价格已经超过了3美元大关,

2010-04-09 09:11:05 904

904 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4760

4760

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,DDR4雏形初现。但是在我们利用这些新技术前,设计人员必须了解如何

2011-07-11 11:17:14 6408

6408

总结了DDR和DDR2,DDR3三者的区别,对于初学者有很大的帮助

2015-11-10 17:05:37 36

36 用ise工具调用DDR3 IP核教程,内容非常的详细

2015-11-20 11:56:20 0

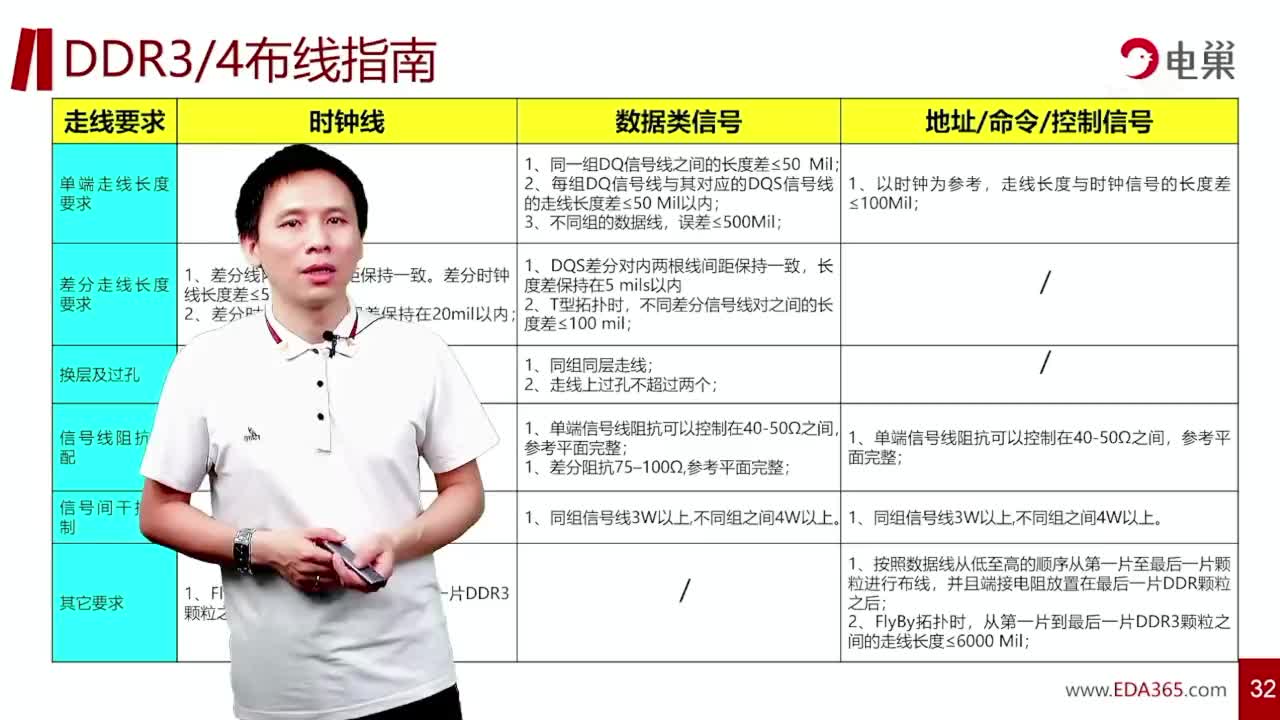

0 针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 Xilinx FPGA工程例子源码:Xilinx DDR3最新VHDL代码(通过调试)

2016-06-07 14:54:57 77

77 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 华芯半导体DDR3内存颗粒 datasheet

2016-12-17 21:59:12 0

0 DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 9412

9412

DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank

2017-11-07 10:48:51 55968

55968

虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 32469

32469 为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 25160

25160

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 28010

28010 本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取

2017-11-17 14:26:43 26092

26092

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 7989

7989

针对采用DDR3接口来设计的新一代闪存固态盘(SSD)需要完成与内存控制器进行通信与交互的特点,提出了基于现场可编程门阵列( FPGA)的DDR3协议解析逻辑方案。首先,介绍了DDR3内存工作原理

2017-12-05 09:34:44 10

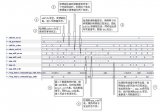

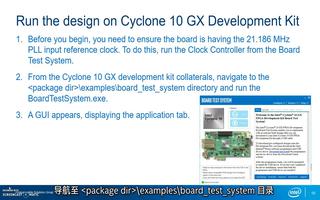

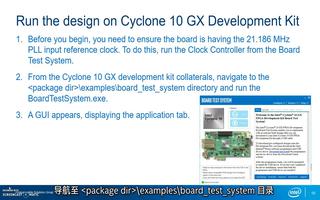

10 Cyclone 10 GX DDR3 示例设计的步骤

2018-06-20 00:12:00 6906

6906

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11:53 6929

6929

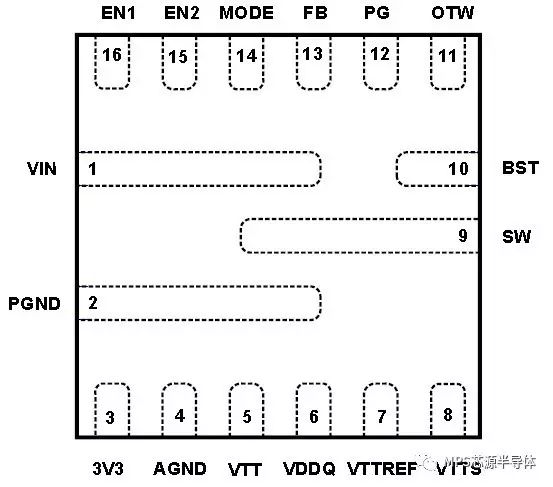

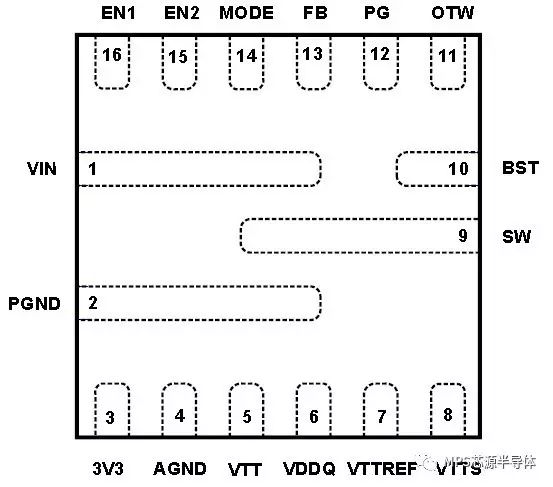

NB685简约而不简单,只需要简单而又不占太大空间的外部电路,即可有效地控制供电电压,使其能够为诸如DDR3, DDR3L, LPDDR3, DDR4等内存供电。并且输出电压可调节,只要微调外部电路即可。

2019-10-11 15:30:37 19137

19137

DDR3 SDRAM是DDR3的全称,它针对Intel新型芯片的一代内存技术(但目前主要用于显卡内存),频率在800M以上。DDR3是在DDR2基础上采用的新型设计,与DDR2 SDRAM相比具有功耗和发热量较小、工作频率更高、降低显卡整体成本、通用性好的优势。

2019-10-29 08:00:00 0

0 本文意在介绍如何使用i.MX6 系列微处理器设计和初始化DDR3。本文将涉及原理图及PCB 布线设计规则、DDR3 脚本(初始化代码)生成工具、DDR3 板级校准和压力测试工具等内容。

2020-05-11 17:04:00 80

80 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 从成本的角度来看,DDR3也许的确要比DDR4低一些,所以从这个角度可以讲通。

2020-09-08 16:28:23 5268

5268 用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准

2021-03-19 08:44:50 13

13 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2021-05-02 09:05:00 4229

4229

DDR4相比DDR3的相关变更点相比DDR3,DDR4存在诸多变更点,其中与硬件设计直接相关的变更点主要有: 增加Vpp电源; VREFDQ删除; CMD、ADD、CTRL命令的端接变更为

2021-11-06 20:36:00 30

30 文章目录一、 项目介绍:写命令和写数据总线介绍写控制模块框图及波形代码(1)连续写(2)间隔部分测试代码一、 项目介绍:本章节将会讲解 A7 芯片内自带的 DDR3 SDRAM 的 IP 核的写时序

2021-12-04 19:21:05 4

4 本文以一个案例的形式来介绍lattice DDR3 IP核的生成及调用过程,同时介绍各个接口信号的功能作用

2022-03-16 14:14:19 2713

2713

日前,世界著名硬件网站TomsHardware上有消息表示,多家大厂都在考虑停止DDR3内存的生产。DDR3内存早在2007年就被引入,至今已长达15年,因为其不再泛用于主流平台,即便退出市场也不会

2022-04-06 12:22:56 6223

6223 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28:58 3160

3160 一、DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据

2022-12-21 18:30:05 5150

5150 DDR3的速度较高,如果控制芯片封装较大,则不同pin脚对应的时延差异较大,必须进行pin delay时序补偿。

2023-07-04 09:25:38 936

936

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 3

3 复制Vivado工程路径vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夹。粘贴到仿真路径testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夹)下。

2023-08-12 11:08:27 2190

2190 本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 7275

7275

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 3353

3353

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 1889

1889

是目前使用最为广泛的计算机内存标准,它已经服务了计算机用户多年。但是,DDR4内存随着技术的进步,成为了更好的内存选择。本文将详细介绍DDR4和DDR3内存的各种区别。 1. 工作频率 DDR3内存的标准工作频率为1600MHz,而DDR4内存标准则为2133MHz。这意味着DDR4内存的传输速度

2023-10-30 09:22:00 13839

13839 随着技术的不断进步,计算机内存技术也在不断发展。DDR(Double Data Rate)内存条作为计算机的重要组成部分,其性能直接影响到电脑的运行速度和稳定性。DDR3和DDR4是目前市场上最常

2024-11-20 14:24:22 11362

11362 DDR3、DDR4、DDR5是计算机内存类型的不同阶段,分别代表第三代、第四代和第五代双倍数据速率同步动态随机存取存储器(SDRAM)。以下是它们之间的性能对比: 一、速度与带宽 DDR3 :速度

2024-11-29 15:08:28 19708

19708 据报道,业内人士透露,全球三大DRAM内存制造商——三星电子、SK海力士和美光,有望在2025年内正式停产已有多年历史的DDR3和DDR4两代内存。 随着技术的不断进步和消费级平台的更新换代

2025-02-19 11:11:51 3465

3465 的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

2025-07-28 16:33:12 4

4 电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4

电子发烧友App

电子发烧友App

评论