2022年4月20日,中国苏州讯—— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。

华邦的1.35V DDR3 产品在x8 和x16 配置中均可提供高达2133Mbps 的数据传输速率,并可与1.5V DDR3实现100%兼容。目前,华邦的DRAM 产品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR2、512Mb-2Gb LP DDR2,以及LP DDR4x、LP DDR3、LP DDR、SDRAM,适用于需配备4Gb 或以下容量DRAM 的应用,如人工智能加速器、物联网、汽车、工业用、电信、WiFi-6、WiFi-6E、xDSL、光纤网络、智能电视、机顶盒、IP摄像头等。此外,华邦位于台湾高雄的新建晶圆厂将于2022 年第四季度启用,采用更先进的制造技术提升产能。华邦DDR3 出货量占DRAM 总收入的30%,预计2024 年将增加至50%。

华邦表示:“十年来,华邦一直为业界供应极具竞争力的DDR3 产品,并将在未来10多年内继续生产DDR3,为客户提供高品质的产品及服务支持。如今,客户仍然需要DDR3 SDRAM产品,而将客户放在首位则是华邦的运营理念与目标,因此我们将持续供应DDR3,以确保满足客户的长期使用需求。”

欲了解有关华邦DDR3产品的更多信息,请访问https://www.winbond.com/hq/product/specialty-dram/ddr3-sdram/?__locale=zh

-

半导体

+关注

关注

336文章

29977浏览量

258222 -

物联网

+关注

关注

2939文章

47317浏览量

407851 -

华邦电子

+关注

关注

0文章

81浏览量

17155

发布评论请先 登录

华邦电子推出先进 16nm 制程 8Gb DDR4 DRAM 专为工业与嵌入式应用而生

HummingBird EV Kit - DDR3 引脚不匹配是怎么回事?

基于FPGA的DDR控制器设计

基于DDR200T开发板的e203进行DDR3扩展

DDR200T中的DDR3的使用配置

FPGA搭建DDR控制模块

用FPGA实现DDR控制模块介绍

AD设计DDR3时等长设计技巧

AD设计DDR3时等长设计技巧

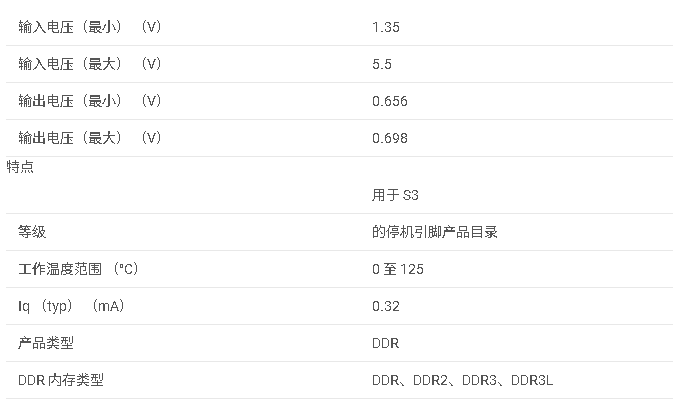

LP2996A 1.5A DDR 终端稳压器,带关断引脚,用于 DDR2/3/3L数据手册

DDR3 SDRAM配置教程

华邦将持续扩产 DDR3 SDRAM

华邦将持续扩产 DDR3 SDRAM

评论