将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1。

参考工程:ddr3_test。

第五篇:mig读写时序下板实现

1顶层文件和约束文件

ddr3_test.v

参见参考工程:ddr3_test。

ddr3.xdc

1. set_property PACKAGE_PIN E3 [get_ports clk]

2. set_property IOSTANDARD LVCMOS33 [get_ports clk]

3. set_property PACKAGE_PIN D9 [get_ports reset]

4. set_property PACKAGE_PIN E1 [get_ports init_calib_complete]

5. set_property IOSTANDARD LVCMOS33 [get_ports init_calib_complete]

6. set_property IOSTANDARD LVCMOS33 [get_ports reset]

2 下板实现读写时序

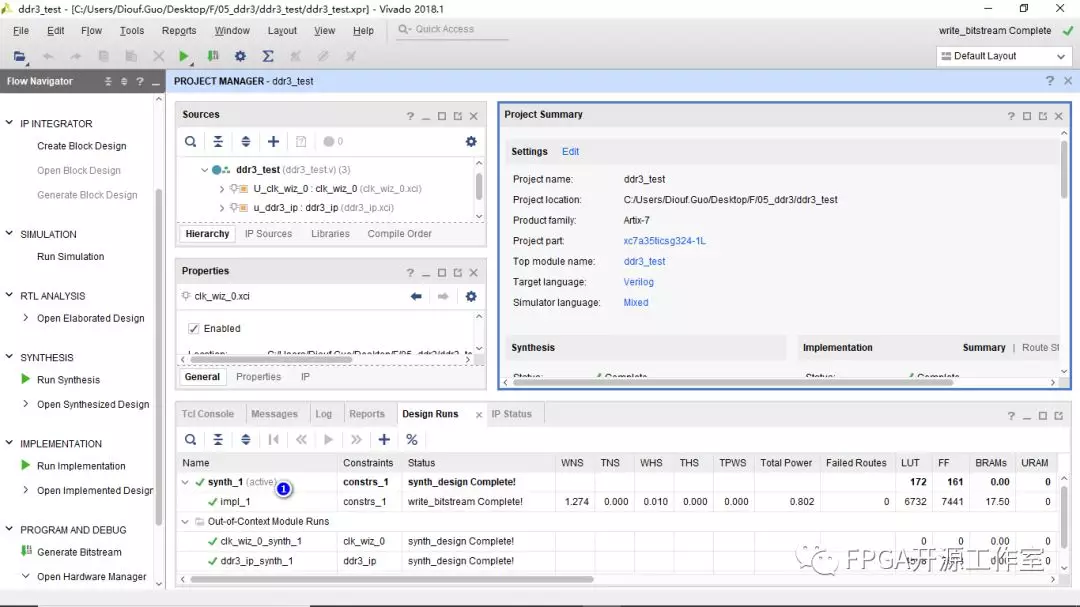

1>①完成综合和实现

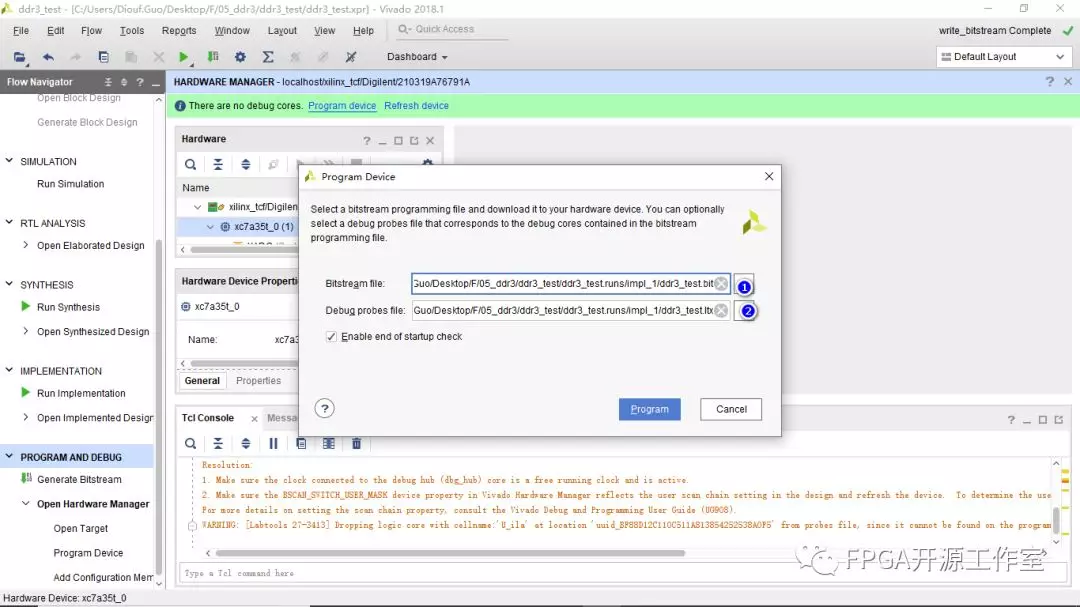

2>下载bit文件和debug文件。

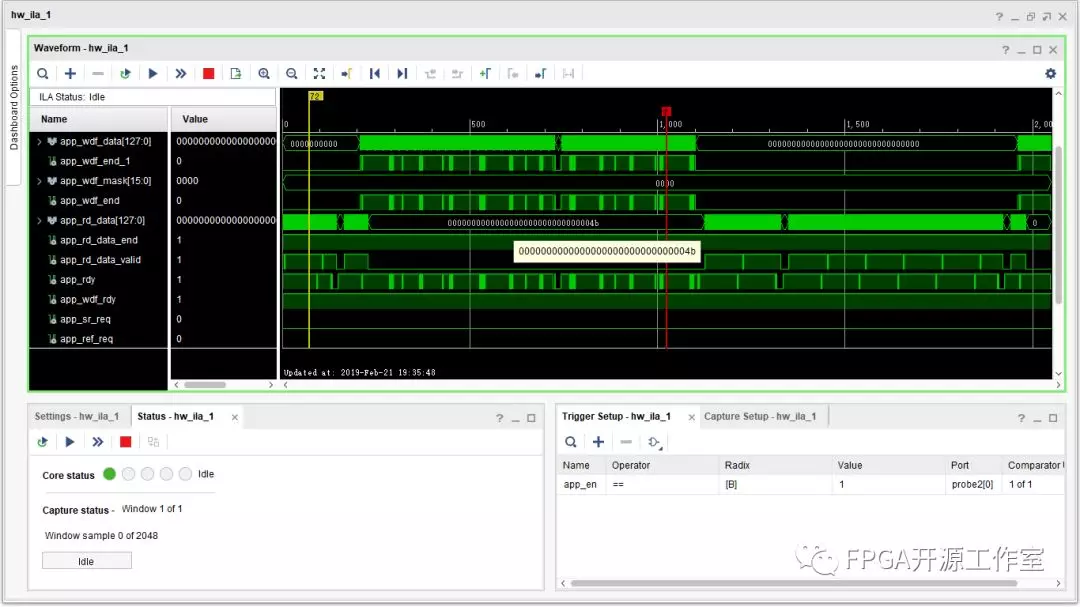

3>下载完成,查看波形。

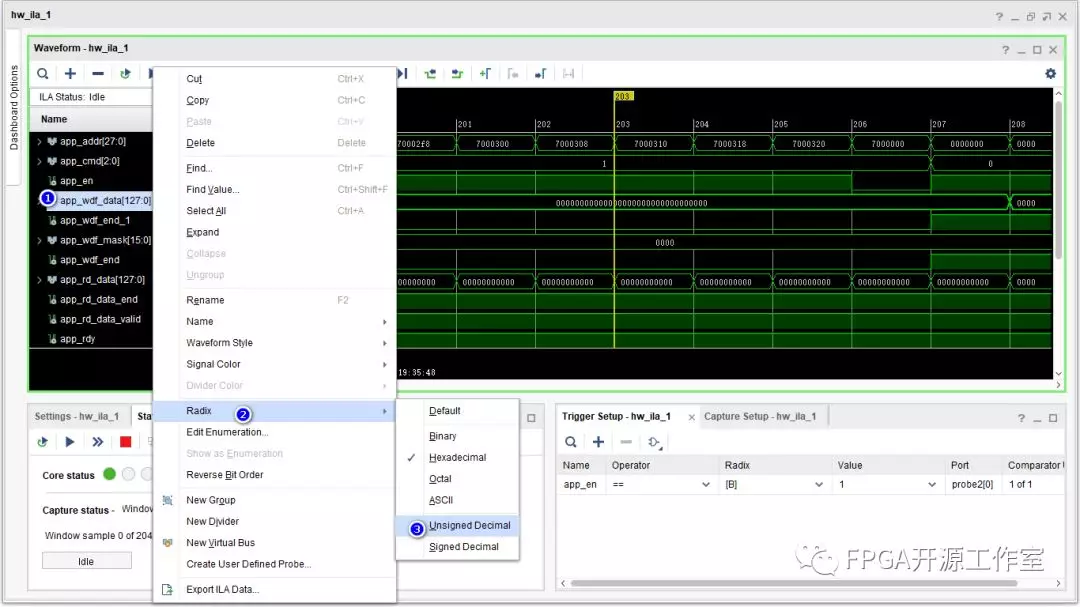

4>将app_wdf_data数据格式改为Unsigned Decimal。

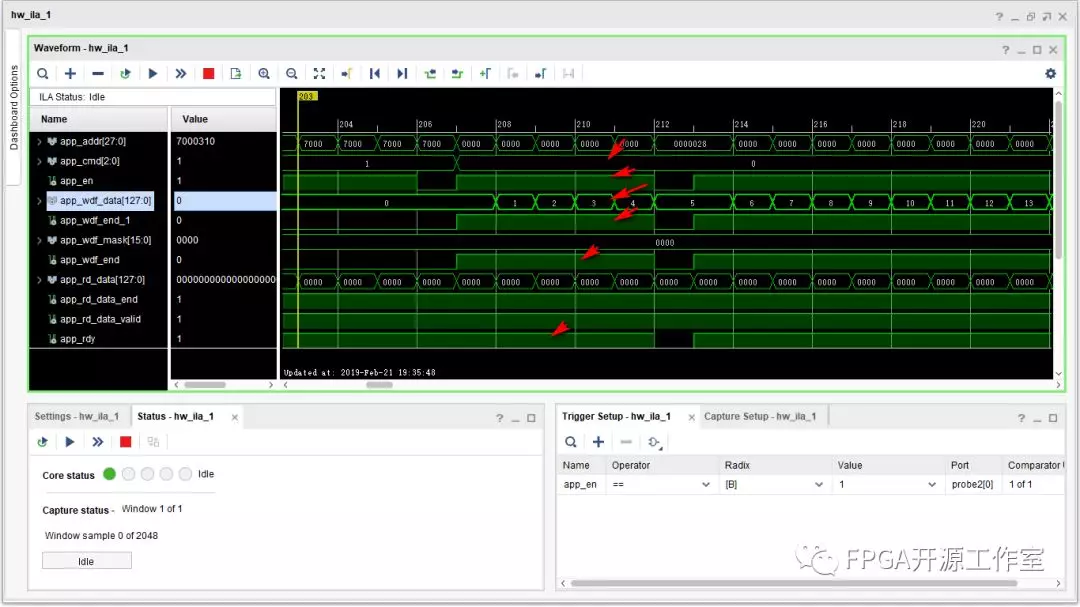

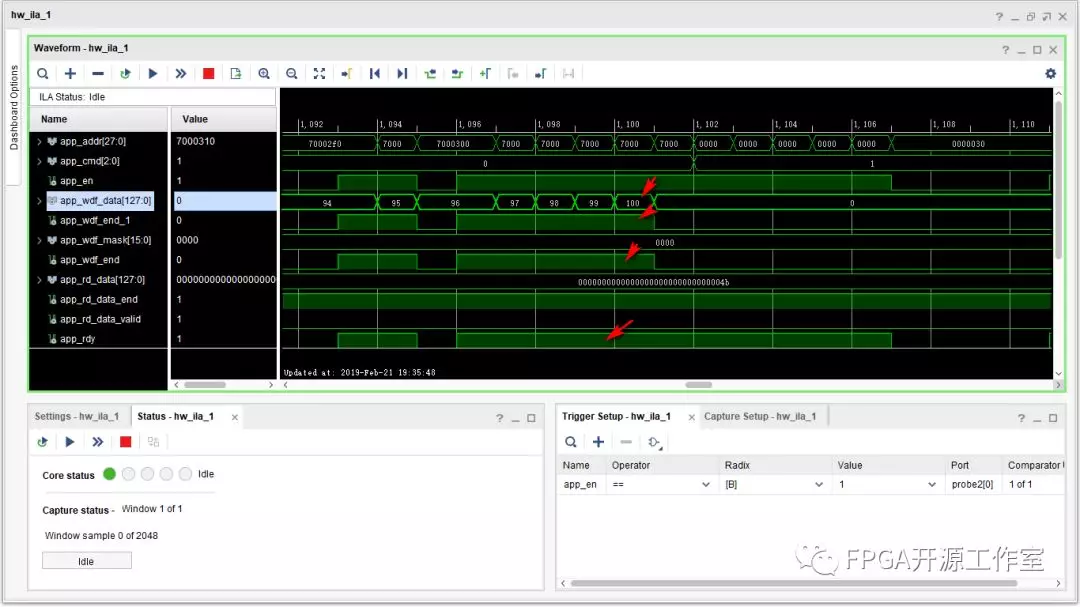

5>查看写时序。

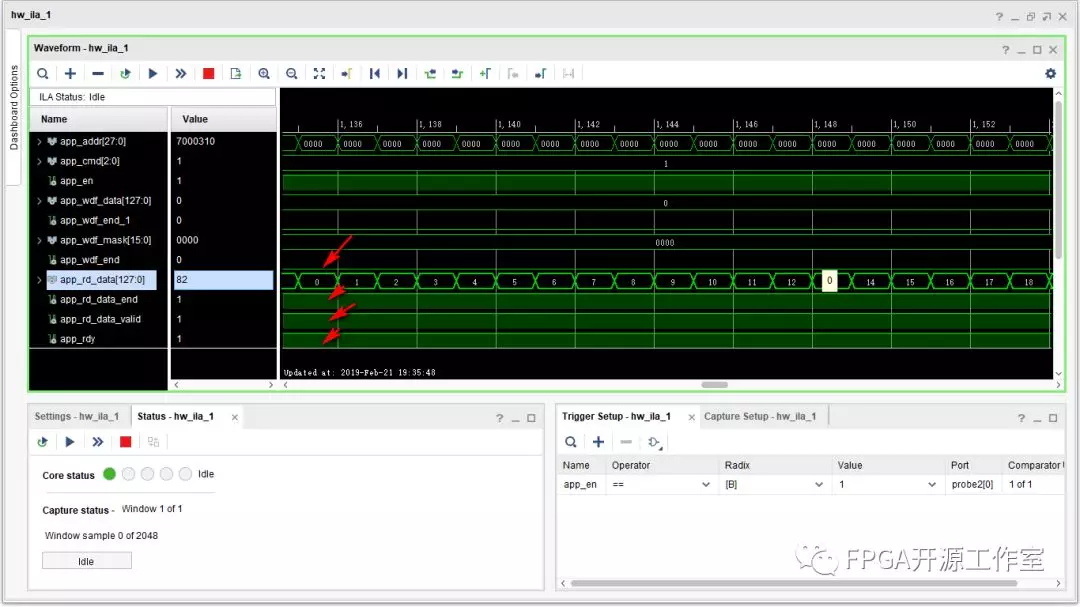

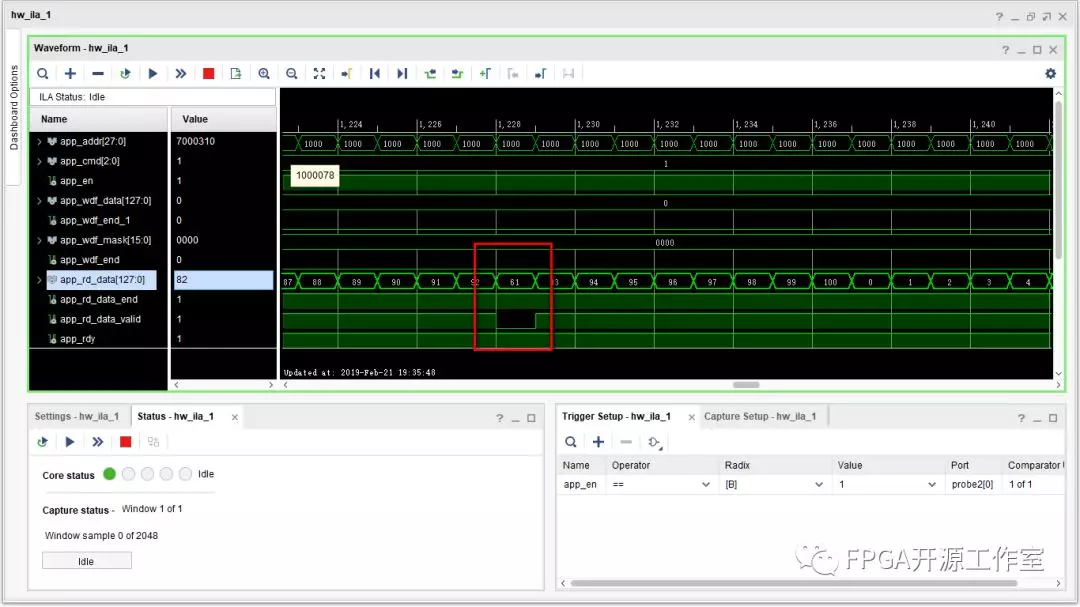

6>查看读时序。

基于xilinx mig ip对ddr3读写验证完成。

编辑:hfy

-

FPGA

+关注

关注

1655文章

22288浏览量

630335 -

DDR3

+关注

关注

2文章

287浏览量

43943

发布评论请先 登录

如何不用olimex ARM-USB-TINY-H debugger实现调试?

vivado连接Atry A7-35T死机怎么解决?

Hbirdv2移植到Nexys4 DDR和Nexys Video开发板

利用蜂鸟E203搭建SoC【4】——DDR200T内存扩展

基于FPGA的DDR控制器设计

FPGA搭建DDR控制模块

用FPGA实现DDR控制模块介绍

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板

AD设计DDR3时等长设计技巧

AD设计DDR3时等长设计技巧

【RK3568+PG2L50H开发板实验例程】FPGA部分 | DDR3 读写实验例程

【FPGA新品】正点原子L22开发板来了!采用紫光的Logos系列FPGA,适合工业控制、图像处理、高速通信等领域!

DDR3 SDRAM配置教程

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

评论