DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

最开始的DDR,芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,它采用的是BGA封装,所有焊点是藏在芯片的底部的,测试起来非常不便,一般需要提前预留测试点。

在DDR读写burst分析之前,首先得把read burst和write burst分离出来,读写双向的数据全部都搁在DQS和DQ上。那么,DDR的手册中,留下了哪些线索供我们进行读写的分离呢?

要实现DDR的快速的便捷的分离,在读写分离之前,我们必须得知道DDR读写信号之间的特征差异。首先,看看SPEC里面的定义:

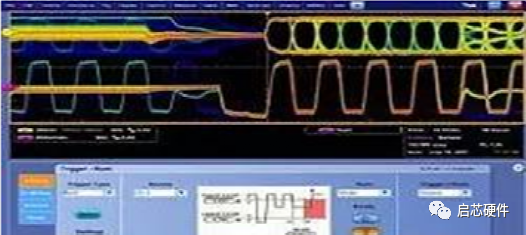

方法一:preamble的差异

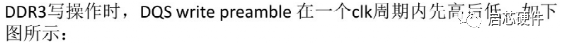

在每次的burst之前,DQS会从高阻态切换到一段负脉冲,然后才开始正常的读写。这段负脉冲,我们叫做preamble(preamble实际上是在读写前,DQS提前通知DRAM芯片或者是controller的信号)。一般说来,读数据DQS的preamble宽度要大于写数据。对于DDR3,情况就更简单了。因为在DDR3中,读数据的preamble是负脉冲,写数据的preamble是正脉冲。

方法二:幅度上的差异

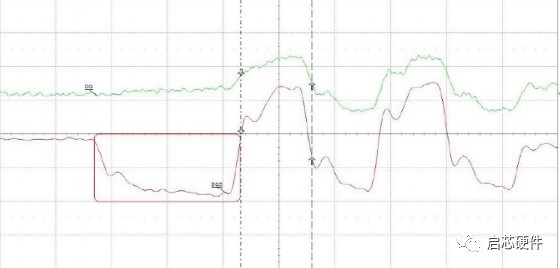

一般在DRAM端进行测试,写数据从memory controller出来,经过了主板PCB板,内存插槽和内存条PCB板,到达DRAM颗粒的时候,信号已经被衰减了,而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的幅度要大于写数据。

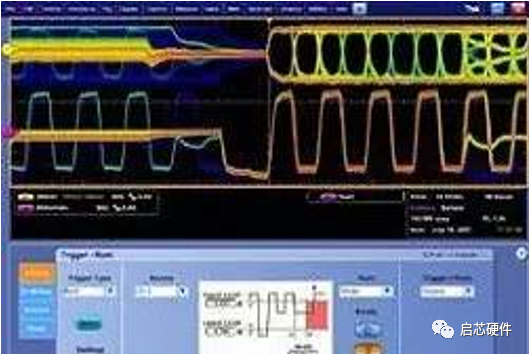

方法三:对齐方式

写数据是DQS和DQ centre-align(中间对齐), 读数据DQS和DQ是edge align(边沿对齐),memory controller在接收到内存的读数据时,在controller内部把DQS和DQ的相位错开90度,实现中间对齐来采样(这个过程示波器就看不到咯);

方法四:斜率的差异:

读数据的斜率大于写数据。一般在DRAM端进行测试,写数据从memory controller出来,经过了主板PCB板,内存插槽和内存条PCB板,到达DRAM颗粒的时候,信号已经被衰减了,所以,斜率也小一些;而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的斜率要大于写数据。也可以从下图得到区分。

Read

Write

总结:

在计算机内存系统中,DDR3(Double Data Rate 3)是一种内存类型,具有读写分离(Read-Write Separation)的特性。这种特性可以在一定程度上提高内存的性能和效率。

DDR3的读写分离是DDR内存的一项基本功能,它是通过DQ和DQS信号来区分读操作和写操作的。

读写分离原理:

读写分离是指DDR3内存模块在执行读取和写入操作时使用不同的内部电路和通道。这使得内存可以同时进行读取和写入操作,而不需要等待一个操作完成后再执行另一个操作。这样可以显著提高内存的数据传输速度和效率,从而加快整个系统的响应速度。

在DDR3内存中,DQ信号用于传输数据,而DQS信号用于传输数据读取和写入的时钟信号。在读操作时,DQS信号会与DQ信号的边沿对齐,而在写操作时,DQS信号会在DQ信号的中央对齐。这种不同的对齐方式使得DDR3内存可以区分读操作和写操作。

内部通道分离:

DDR3内存模块内部通常分为读取通道和写入通道。这两个通道可以并行工作,分别处理读取和写入操作。通过这种分离,读取和写入操作可以同时进行,减少了等待时间。

命令队列:

DDR3内存模块通常具有命令队列(Command Queue)的功能。命令队列可以在内存控制器和内存模块之间缓存一系列的读取和写入命令。这有助于提高内存的效率,因为内存控制器可以将命令连续发送到内存模块,而无需等待每个命令的完成。

并行性提高性能:

读写分离以及命令队列的特性使DDR3内存模块能够在一定程度上实现并行性,从而提高了内存的性能。它可以在处理大量数据时更加高效,同时也有助于降低内存延迟。

利用DDR3内存中读数据和写数据之间信号特征的差异:在每次的burst开始时,DQS会从高阻态切换到一段负脉冲,然后才开始正常的读写。这段负脉冲叫做preamble(preamble实际上是在读写前,DQS提前通知DRAM芯片或者是controller的信号)。一般说来,读数据DQS的preamble宽度要大于写数据。对于DDR3,情况就更简单了。因为在DDR3中,读数据的preamble是负脉冲,写数据的preamble是正脉冲。

幅度上的差异:一般在DRAM端进行测试,写数据从memory controller出来,经过了主板PCB板,内存插槽和内存条PCB板,到达DRAM颗粒的时候,信号已经被衰减了,而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的幅度要大于写数据。

请注意,对于DDR3内存的读写分离具体实现可能会因不同的硬件设备和系统环境而有所不同。如果您需要更详细或最新的信息,建议咨询相关的硬件工程师或参考最新的技术文档。

-

芯片

+关注

关注

447文章

47788浏览量

409121 -

DDR3

+关注

关注

2文章

268浏览量

41788 -

封装

+关注

关注

123文章

7278浏览量

141096 -

DDR

+关注

关注

9文章

677浏览量

64240 -

BGA

+关注

关注

4文章

504浏览量

46025

发布评论请先 登录

相关推荐

如何提高DDR3的效率

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

基于Xilinx MIS IP的DDR3读写User Interface解析

基于FPGA的DDR3六通道读写防冲突设计

基于FPGA的DDR3 SDRAM控制器的设计与优化

基于FPGA的DDR3多端口读写存储管理的设计与实现

DDR3芯片读写控制及调试总结

基于FPGA的DDR3多端口读写存储管理的设计与实现

阐述DDR3读写分离的方法

阐述DDR3读写分离的方法

评论