相较于传统边射型半导体雷射的发展,垂直共握腔面射型雷射(VCSEL)的设计概念直到1979年首先被I....

共振腔中雷射光来回(round trip)振荡后保持光学自再现(self-consistency)的....

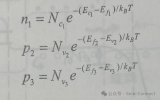

在半导体中,光子的放射是由电子和电洞借由垂直跃迁所达成的,我们可以把具有相同k值的电子一电洞看成一种....

一个基本的半导体雷射如图2-1所示,包含了两个平行劈裂镜面组成的共振腔,称为Fabry-Perot ....

早期面射型雷射由于半导体磊晶技术简在发展初期阶段,因此还无法直接成长反射率符合雷射操作需求的全磊晶导....

早期所谓的面射型雷射(surface emitting laser, EBL)本质上仍然是边射型雷射....

LASER是“light amplification by stimulated emission ....

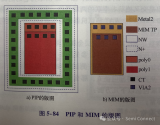

CMOS 工艺技术平台的电容包括 MIM 和 PIP (Poly Insulator Poly)。P....

CMOS 工艺平台的金属方块电阻的测试结构包含该平台的所有金属层,例如如果该平台使用五层金属层,那么....

CMOS工艺平台的Poly 方块电阻有四种类型的电阻,它们分别是n型金属硅化物 Poly 方块电阻、....

图5-34所示为PW方块电阻的版图,图5-35所示为它的剖面图。PW方块电阻是通过DNW 隔离衬底(....

CMOS 工艺技术平台的方块电阻的测试结构是NW方块电阻、PW方块电阻、Poly 方块电阻、AA 方....

虽然 WAT测试类型非常多,不过业界对于 WAT测试类型都有一个明确的要求,就是包括该工艺技术平台所....

WAT是英文 Wafer Acceptance Test 的缩写,意思是晶圆接受测试,业界也称WAT....

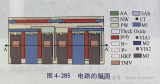

顶层金属 AI工艺是指形成顶层金属 AI 互连线。因为 Cu很容易在空气中氧化,形成疏松的氧化铜,而....

IMD4 工艺是形成 TMV (Top Metal VIA,顶层金属通孔)的介质隔离材料,同时IMD....

IMD3工艺包括 IMD3a工艺和IMD3b工艺。IMD3a 工艺是形成 VIA2 的介质隔离材料,....

接触孔工艺是指在 ILD 介质层上形成很多细小的垂直通孔,它是器件与第一层金属层的连接通道。通孔的填....

IMD1工艺是指在第一层金属之间的介质隔离材料。IMD1的材料是 ULK (Ultra Low K)....

金属层1工艺是指形成第一层金属互连线,第一层金属互连线的目的是实现把不同区域的接触孔连起来,以及把不....

ILD 工艺是指在器件与第一层金属之间形成的介质材料,形成电性隔离。ILD介质层可以有效地隔离金属互....

Salicide 工艺是指在没有氧化物覆盖的衬底硅和多晶硅上形成金属硅化物,从而得到低阻的有源区和多....

与亚微米工艺类似,源漏离子注入工艺是指形成器件的源漏有源区重掺杂的工艺,降低器件有源区的串联电阻,提....

与亚微米工艺类似,侧墙工艺是指形成环绕多晶硅的氧化介质层,从而保护LDD 结构,防止重掺杂的源漏离子....

与亚微米工艺类似,多晶硅栅工艺是指形成 MOS器件的多晶硅栅极,栅极的作用是控制器件的关闭或者导通。....

与亚微米工艺类似,栅氧化层工艺是通过热氧化形成高质量的栅氧化层,它的热稳定性和界面态都非常好。

与亚微米工艺类似,双阱工艺是指形成NW和PW的工艺,NMOS 是制造在PW里的,PMOS是制造在NW....

STI 隔离工艺是指利用氧化硅填充沟槽,在器件有源区之间嵌入很厚的氧化物,从而形成器件之间的隔离。利....

有源区工艺是指通过刻蚀去掉非有源区的区域的硅衬底,而保留器件的有源区。

集成电路的可靠性与内部半导体器件表面的性质有密切的关系,目前大部分的集成电路采用塑料封装而非陶瓷封装....