为了确保验证的完备性,我们需要量化验证目标。SystemVerilog提供了一套丰富的覆盖率建模方式....

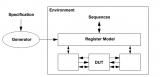

寄存器模型保持着DUT内部寄存器值的 镜像(mirror) 。 镜像值不能保证是正确的,因为寄存器模....

UVM register layer classes用于为DUV中的memory-mapped寄存器....

在一个系统级的验证环境中,多个验证组件并行地产生激励。测试用例开发者可能希望协调多个通道激励之间的时....

在验证过程中让DUT进入特定场景只是验证的重要部分之一,验证环境还应该检查来自DUT的输出响应。

为了实现验证目标,测试用例开发者需要控制测试激励的生成以覆盖特定的场景。测试用例开发者可以用下面这些....

在UVM中,Testcase是一个类,它封装了测试用例开发者编写的特定激励序列。

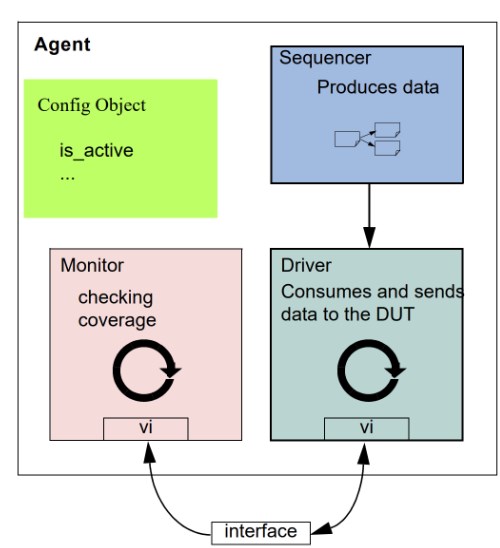

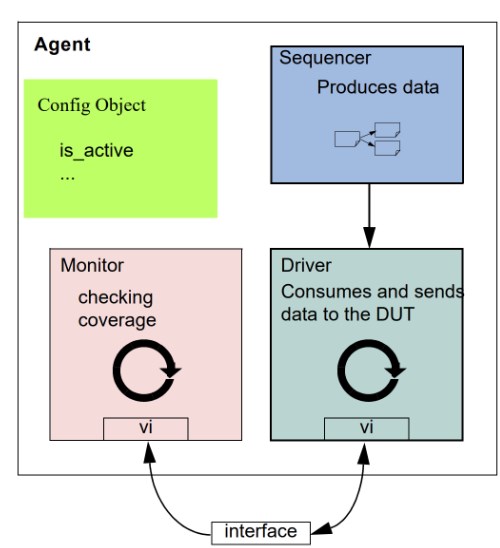

一些典型 的 验证组件 配 置参数示例: 一个agent可以被配置为 active 或者 pass....

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程....

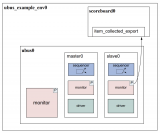

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程....

Checks和coverage是覆盖率驱动的验证流程的关键。在验证环境中,Checks和covera....

UVM中每个phase都有一个内置的objection ,为components和objects提供....

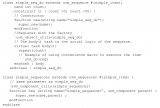

Sequencer默认不执行任何Sequence。验证工程师可以通过调用start()启动一个Seq....

验证环境用户需要创建许多测试用例来验证一个DUT的功能是否正确,验证环境开发者应该通过以下方式提高测....

uvm_do宏及其变体提供了创建、随机化和发送transaction items或者sequence....

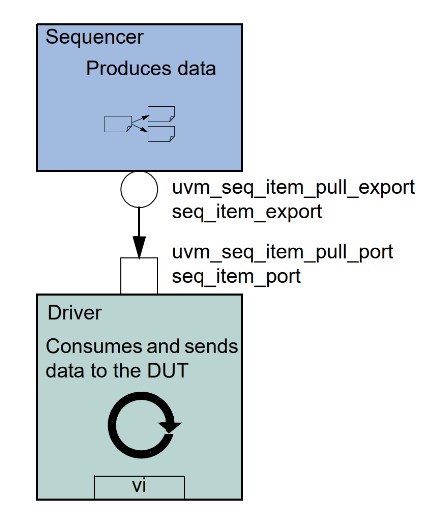

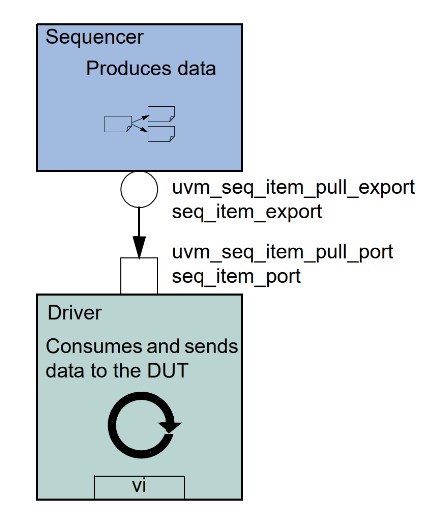

sequencer生成激励数据,并将其传递给driver执行。UVM类库提供了uvm_sequenc....

本文使用Easier UVM Code Generator生成包含多个agent和interface....

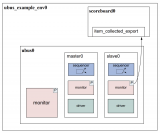

uvm environment 类是一个包含多个可重用的验证组件的类,它定义了测试用例所需的验证组件....

agent(如下图)实例化并使用TLM连接driver、monitor和sequencer。

Driver的作用是从sequencer中获得数据项,按照接口协议将数据项驱动到总线上。

作为DUT的激励对象。

TLM接口的使用将验证环境中的每个组件与其他组件隔离。验证环境实例化一个组件,并完成其ports/e....

如下图所示,UVM中的TLM接口为组件之间Transaction的发送和接收提供了一套统一的通信方法....

Analysis port 每个组件通过其TLM接口与系统中的其他组件进行通信,用于给DUT发送激....

在UVM中,transaction 是一个类对象,它包含了建模两个验证组件之间的通信所需的任何信息。

UVM类库提供了通用的代码功能,如component hierarchy、transaction l....

验证生产力的关键之一是在一个合适的抽象级别上考虑验证问题。也就是说,在验证DUT时应该创建一个支持适....

在本文中,我们将进一步实现monitor和coverage collector components....

在运行uvm代码生成器后,我们现在可以开始运行仿真。同样,我们将命令行放入脚本文件中