数据项:

作为DUT的激励对象。

表示验证环境处理的transactions。

用于 transaction-level的覆盖率收集和功能比对。

UVM类库提供uvm_sequence_item基类。每个用户定义的数据项都应该直接或间接地派生自这个基类。

要创建一个数据项,需要:

分析DUT的transaction规格,确定属性、约束、task和function。

从uvm_sequence_item基类(或它的派生类)派生出一个数据项类。

为数据项定义一个new函数。

为步骤(a)中确定的项目增加控制字段("旋钮"),以便于编写测试。

使用UVM field macros来实现打印、复制、比较等,UVM允许单独指定每个字段所需的自动化。

定义do_*函数,用于创建、比较、打印、packing和unpacking所需的transaction数据。

为了帮助debugging和tracking transaction,uvm_transaction基类通过get_transaction_id()成员函数获取唯一的transaction number。因为uvm_sequence_item基类从uvm_transaction扩展而来,所以也包括get_transaction_id()成员函数。

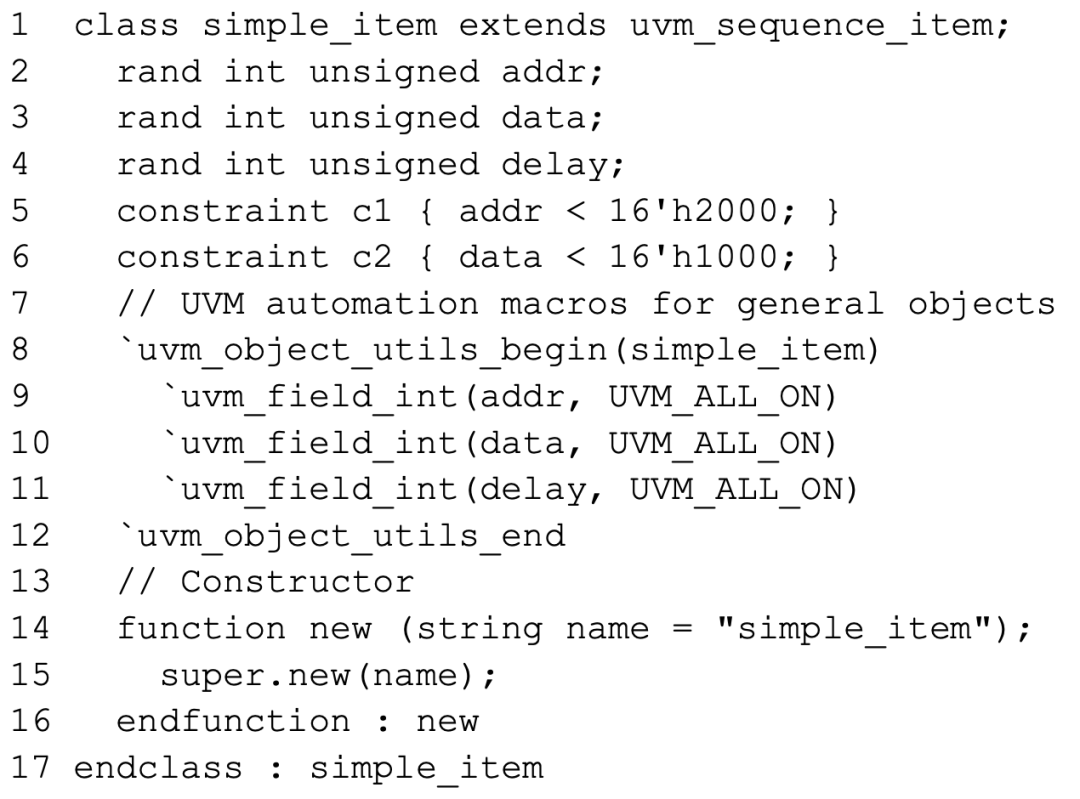

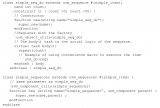

下例中的simple_item类定义了几个随机变量和约束。UVM的宏实现了对这个类进行操作的各种方法,如复制、比较、打印等等。特别是,`uvm_object_utils宏将类的类型注册到factory。

第1行 从uvm_sequence_item派生出数据项,以便它们可以在sequence中生成。

第5行和第6行向数据项添加约束条件,以便:

指定数据项规格。

指定生成数据项的默认分布。

第7行-第12行 使用UVM的宏来自动实现诸如copy(), compare(), print(), pack()等函数。

继承和约束分层

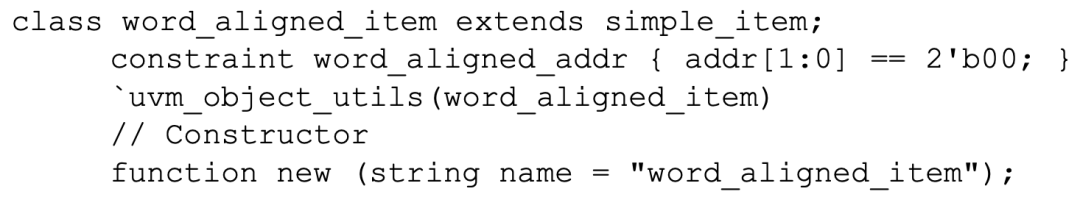

在验证过程中,验证组件用户可能需要通过在类定义中添加更多的约束来调整数据项的生成。在SystemVerilog中 ,这是用继承(inheritance)来完成的。下面的例子显示了一个派生的数据项word_aligned_item,它包括一个额外的约束条件,只选择word对齐的地址。

为了实现这种数据项类型的可扩展性:

数据项的基类(本例中的simple_item)应该使用virtual methods,以允许派生类重写功能。

确保约束块的组织方式,使其能够覆盖或禁用随机变量的约束,而不必重写更多的代码。

字段可以用protected或local关键字声明,以限制对属性的访问。

定义控制字段("旋钮")。

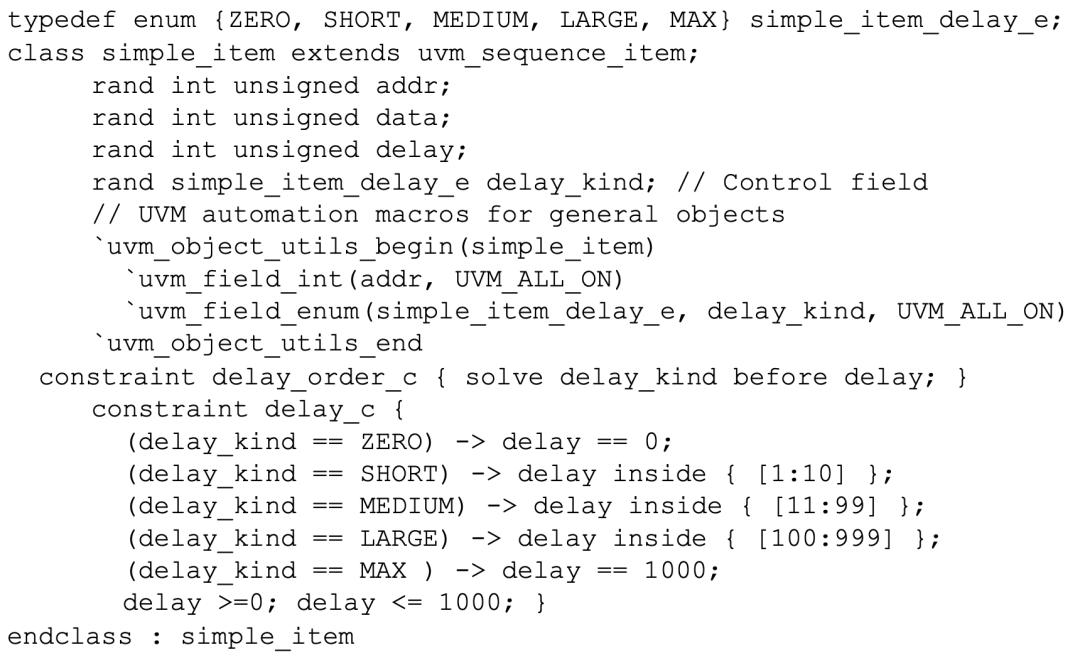

产生输入空间的所有数值往往是不可能的,通常也没有必要。能够从范围或类别的值中生成部分值是很重要的。在上述simple_item例子中,delay属性可以随机化为0和最大无符号整数之间的任何值。

覆盖整个合法空间是没有必要的(也不实际),但是尝试背靠背、短、中、大延迟,以及所有这些delay模式的组合是很重要的。为了做到这一点,需要定义控制字段(通常称为 "旋钮"),使用例编写者能够控制这些变量。

这些控制旋钮也可以用于覆盖率的收集。为了提高可读性,使用枚举类型来表示各种生成的类别。

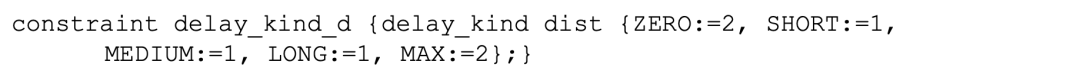

使用这种方法可以创建更加抽象的测试。例如,你可以指定分布为:

在创建数据项时,要牢记经常使用什么范围的值,或者哪些类别是该数据项所需要关注的。然后给数据项添加旋钮,以简化对这些数据项类别的控制和覆盖收集。

审核编辑:汤梓红

-

函数

+关注

关注

3文章

4408浏览量

66905 -

UVM

+关注

关注

0文章

183浏览量

19949 -

验证

+关注

关注

0文章

64浏览量

15676

原文标题:UVM验证环境开发之建模激励数据

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

IC验证"UVM验证平台"组成(三)

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...

如何构建UVM寄存器模型并将寄存器模型集成到验证环境中

ASIC芯片设计之UVM验证

Easier UVM Code Generator Part 4:生成层次化的验证环境

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

UVM验证环境开发之建模激励数据

UVM验证环境开发之建模激励数据

评论