为了实现验证目标,测试用例开发者需要控制测试激励的生成以覆盖特定的场景。测试用例开发者可以用下面这些方法控制测试激励的创建:

添加约束条件来控制单个数据项。

使用UVM sequences来控制多个数据项的顺序。这种方法提供了更多的灵活性和控制。

约束数据项

默认情况下,sequencers会生成完全随机的数据项。测试用例编写者可以控制生成的数据项数量,并向数据项添加约束。为了约束数据项,需要:

识别验证组件中的数据项类和它们的字段。

创建一个数据项类的派生,增加或覆盖默认约束。

在测试用例中,调整环境以使用新定义的数据项。

使用命令行选项指定测试用例名称来运行仿真。

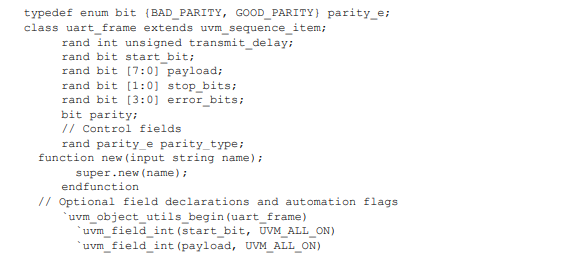

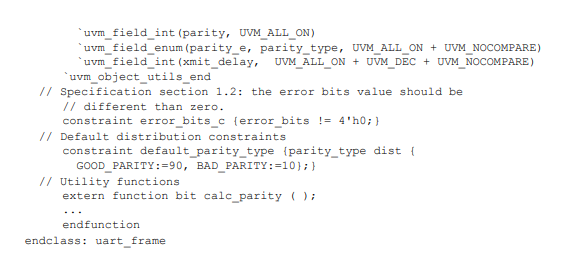

数据项类的定义

派生类中的几个字段来自于DUT规格。例如,一个帧(frame)应该有一个payload被发送到DUT。其他字段的存在是为了帮助测试用例开发者控制激励数据的生成。例如,字段parity_type不被发送到DUT,但它允许测试用例开发者轻松地指定和控制奇偶分布。这样的控制字段被称为 "旋钮knobs"。

验证组件的文档应该列出数据项的旋钮、它们的作用和合法范围。

数据项约束可以来自DUT的规范,例如一个合法的帧必须有不等于0的error_bits_c。数据项中不同类型的约束对数据项的生成进行约束。例如,在约束块default_parity_type中,奇偶校验位被约束为90%合法(good parity)和10%非法(bad parity)。

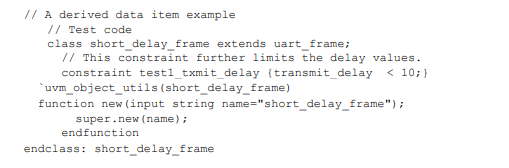

创建一个特定的测试用例

在测试用例中,用户可能希望改变数据项的生成方式。例如,测试用例开发者可能希望有short delays,这可以通过派生一个新的数据项类并根据需要添加约束或其他类成员来实现。

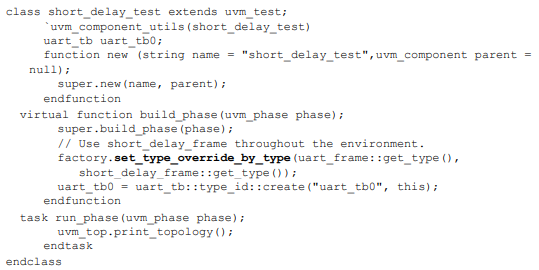

UVM类库的factory机制可以用来将派生类(short_delay_frame)引入到环境中。

调用factory函数set_type_override_by_type(),指示环境使用short-delay帧。有时,测试用例可能想向某一个接口发送特殊的流量,同时继续向其他接口发送常规流量。这可以通过在一个UVM组件中使用set_inst_override_by_type()来实现。

set_inst_override_by_type("uart_env0.master.sequencer.*",

uart_frame::get_type(), short_delay_frame::get_type());

通配符也可以用来覆盖一些组件的实例,例如:

set_inst_override_by_type("uart_env*.master.sequencer.*",

uart_frame::get_type(), short_delay_frame::get_type());

责任编辑:彭菁

-

数据

+关注

关注

8文章

7349浏览量

95025 -

仿真

+关注

关注

55文章

4536浏览量

138671 -

DUT

+关注

关注

0文章

194浏览量

13494

原文标题:创建约束随机测试用例

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

设计验证中的随机约束

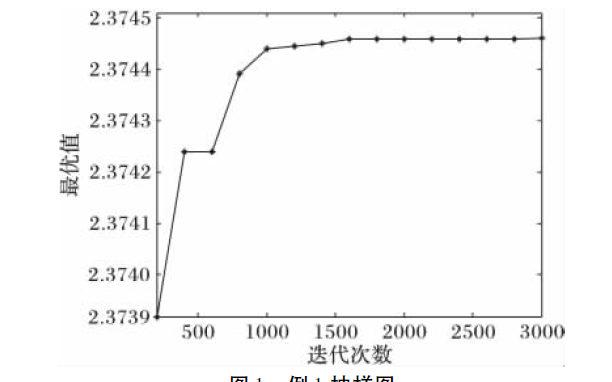

约束优化进化算法研究

基于约束修补的多目标优化算法

如何使用随机模拟技术和神经网络讲解随机机会约束的规划问题

创建输入输出接口时序约束的窍门

创建约束随机测试目标

创建约束随机测试目标

评论